# K2G Industrial Communications Engine (K2G ICE)

# 1 Introduction

This technical user's guide describes the hardware architecture of the 66AK2G02 Industrial Communications Engine (K2GICE). The 66AK2G02 is a KeyStone<sup>™</sup> II-based DSP + ARM System-on-Chip (SoC). This chapter provides an introduction to the K2G ICE, along with the key features and block diagram.

# 1.1 Key Features

The K2G ICE is a high-performance, cost-efficient, standalone development platform that enables users to evaluate and develop industrial applications for the Texas Instrument's Keystone II System-on-Chip (SoC) 66AK2G02.

The K2G SoC (66AK2G02) is the new device from TI's Keystone II architecture with:

- ARM® Cortex®-A15 Microprocessor Unit (ARM A15) Subsystem at up to 600 MHz

- · C66x Fixed- and Floating-Point VLIW DSP Subsystem at up to 600 MHz

- Two Programmable Real-Time Unit and Industrial Communication Subsystems (PRU-ICSS)

- Multicore Shared Memory Controller (MSMC) with 1024KB of Shared L2 RAM

- Up to 36-Bit DDR3 External Memory Interface (EMIF) with ECC (32-Bit Data + 4-Bit ECC)

- PCI-Express<sup>®</sup> 2.0 Port with Integrated PHY

- Three Multichannel Audio Serial Port (McASP) Peripherals

- Multichannel Buffered Serial Port (McBSP)

- Six Enhanced High-Resolution Pulse Width Modulation (eHRPWM) Modules

- Three Inter-Integrated Circuit (I2C) Interfaces, Three UART Interfaces, and Four Serial Peripheral Interfaces (SPI)

- Seven 64-Bit Timers

- Secure Device Supports High Secure Boot Option

- 21 × 21 mm<sup>2</sup> 0.8-mm pitch WBBGA

Introduction

www.ti.com

The key features of the EVM are:

- Based on the KeyStone II architecture with ARM® Cortex®-A15 @600 MHz and C66x DSP @600 MHz

- 2x PRU-ICSS, supporting multi-protocol industrial Ethernet with up to 4 ports

- 512 MByte of DDR3L

- 256 Mbit of QSPI Flash

- 32 kByte of I2C EEPROM

- Micro SD-Card slot

- 1x Gigabit Ethernet port supporting 10/100/1000 Mbps data rate on RJ45 connector

- PCIe ×1 card edge connector

- LCD display

- Expansion connector with industrial interface signals for customer designs

- On-board XDS100 JTAG Emulator Circuit

- 20-pin JTAG header to support all types of external emulator

- RoHS compliant design

- Powered by DC power-wall adaptor (24 V / 2.5 A) or PCIE Edge Connector

- 8-bit digital output LEDs

- Industrial Ethernet LEDs

- Rotary switch input

- · Boot media selection using DIP switches

- Discrete Board Power Solution

#### CAUTION

Operation my result in high temperatures for some components. Be cautious when handling during operation.

# CAUTION

Components installed on this product are sensitive to Electrostatic Discharge (ESD). Take precautions before handling this product.

# 1.2 REACH Compliance

#### CAUTION

In compliance with the Article 33 provision of the EU REACH regulation, we are notifying you that this module includes crystals (ABM3-25.000MHz-B2-T, ABM3-12.000MHz-D2Y-T) from Abracon LLC that contains two Substance of Very High Concern (SVHC) above 0.1%. These uses from Texas Instruments do not exceed 1 ton per year. The SVHC's are Diboron trioxide CAS# 1303-86-2 and Lead Oxide CAS# 1317-36-8.

# 1.3 Functional Block Diagram

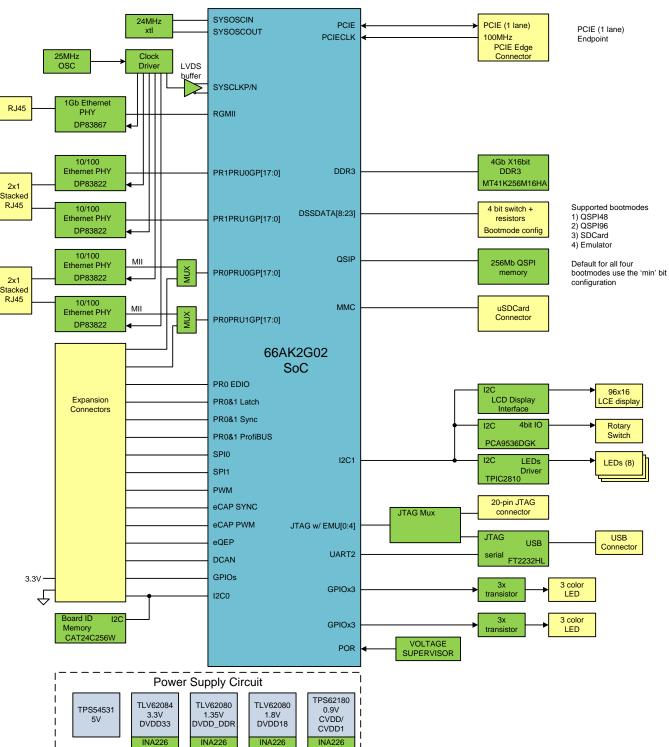

The functional block diagram of the K2G ICE is shown in Figure 1.

# Figure 1. Functional Block Diagram

3

Introduction

Introduction

# 1.4 Basic Operation

This guide provides the steps to setup and run the EtherCAT slave demo on K2G ICE. The EtherCAT slave demo is delivered with the K2G ICE board on the provided micron SDcard. Refer to this link for more details on TI's PRU-ICSS EtherCAT industrial software package.

An online version of these instructions can be found at http://processors.wiki.ti.com/index.php/Configuring\_TwinCAT\_For\_K2GICE\_EtherCAT\_Slave.

# 1.4.1 Running the EtherCAT Slave Demo on K2G ICE

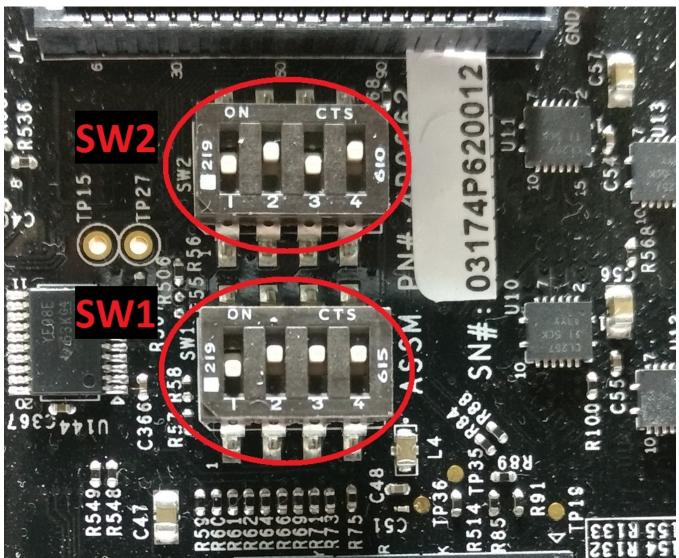

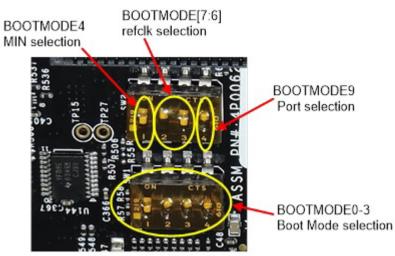

- 1. Confirm the boot switches are set to SD boot. Deliver the K2G ICE with the switches in this configuration, as shown in Figure 2:

- SW1 OFF ON ON ON

- SW2 OFF ON OFF ON

# Figure 2. Switch Configuration

2. Insert the microSD card with the EtherCAT slave demo binaries into the microSD slot (bottom side of the board).

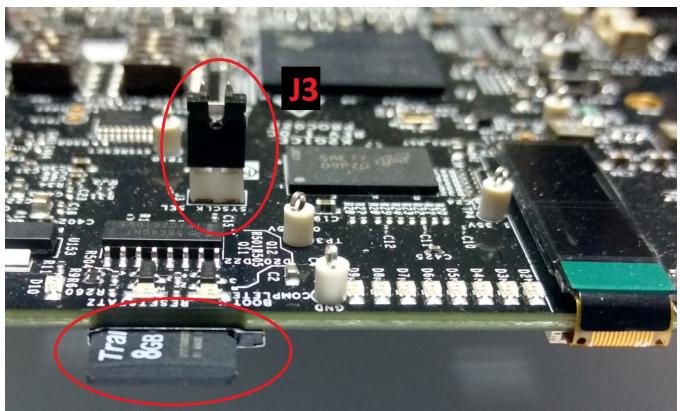

3. Select the 24-MHz crystal as the clock source for the K2G by shorting the pins jumper J3, using the shunt provided, as shown in Figure 3. The K2G ICE should be delivered with the shunt installed.

Figure 3. Short J3 Pin

4. Connect the Ethernet cable between the K2G ICE EtherCAT IN/Port0 (J8, lower RJ-45 port) and the PC with the TwinCAT installation, as shown in Figure 4.

#### Figure 4. Connect Ethernet Cable

Introduction

www.ti.com

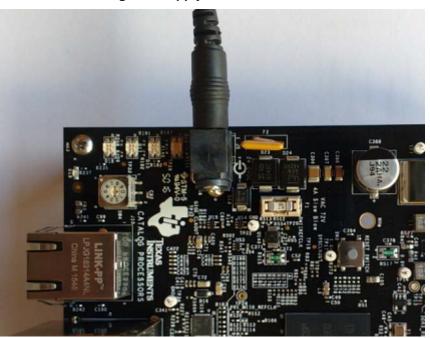

5. Apply +24 V to the K2G ICE with either a bench power supply or with a +24-V power supply purchased separately, as shown in Figure 5.

Figure 5. Apply +24 V to K2G ICE

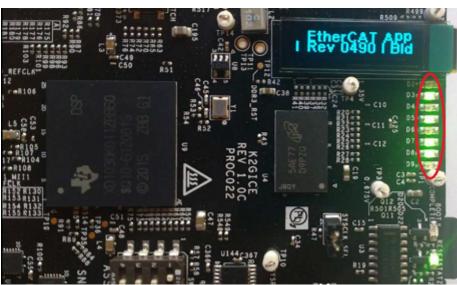

6. Observe that the message 'EtherCAT APP' appears on the OLED display. Also observe the LEDs for the pattern shown in Figure 6 to confirm that EtherCAT application has started.

Figure 6. LED Pattern

The K2G ICE is now acting as an EtherCAT slave, and the industrial LEDs can be lit using instructions from an EtherCAT master using the TwinCAT application. Instructions for installing and operating the TwinCAT application can be found in the K2G ICE User's Guide.

# 1.4.2 Setting Up the TwinCAT Application

- 1. Download and install the PRU-ICSS EtherCAT Industrial software package from http://softwaredl.ti.com/processor-industrial-sw/esd/PRU\_ICSS\_EtherCAT\_Slave/latest/index\_FDS.html. Refer to the documentation under {*EtherCAT\_package\_install\_path*}/docs for more details on PRU-ICSS EtherCAT industrial software package.

- 2. TwinCAT software setup:

- a. Install TwinCAT (evaluation version is available for download from http://www.beckhoff.co.in/english.asp?download/tc3-download-xae.htm. Select PLC mode for installation and check the IO drivers box).

- b. For EtherCAT Slave Demo application: copy {*EtherCAT\_package\_install\_path*}\examples\ethercat\_slave\esi\TiEtherCATLib.xml to the <*Drive*>:\TwinCAT\o\EtherCAT folder. If using TwinCAT 3.1, the folder path is <*Drive*>:\TwinCAT\3.1\Config\Io\EtherCAT.

- c. For EtherCAT Slave Full Mode application: copy {*EtherCAT\_package\_install\_path*}/protocols/ethercat\_slave/ecat\_appl/esi\TI\_ESC.xml to the <*Drive*>:\TwinCAT\Io\EtherCAT folder. If you are using TwinCAT 3.1, the folder path is <*Drive*>:\TwinCAT\3.1\Config\Io\EtherCAT.

- 3. Start TwinCAT XAE (VS 2010) from the Start menu. Create a new TwinCAT XAE Project (XML format), as shown in Figure 7 and Figure 8.

|      | Microsoft Visual Studio (Adr  | ministrator) |         |    |       |       |          |        |

|------|-------------------------------|--------------|---------|----|-------|-------|----------|--------|

| FILE | EDIT VIEW DEBUG               | TWINCAT      | TWINSA  | FE | PLC   | TOOLS | SCOPE    | WINDOW |

|      | New                           |              | •       | ïð | Proje | ct    | Ctrl+Shi | ft+N   |

|      | Open                          |              | •       |    | Web   | Site  | Shift+Al | t+N 🗸  |

|      | Close                         |              |         | õ  | File  |       | Ctrl+N   | _      |

| X    | Close Solution                |              |         |    |       |       |          |        |

|      | Save Selected Items           | Ctrl+S       | 5       |    |       |       |          |        |

|      | Save Selected Items As        |              |         |    |       |       |          |        |

| •    | Save All                      | Ctrl+S       | Shift+S |    |       |       |          |        |

|      | Export Template               |              |         |    |       |       |          |        |

| ₽    | Page Setup                    |              |         |    |       |       |          |        |

| -    | Print                         | Ctrl+F       | 0       |    |       |       |          |        |

|      | Recent Projects and Solutions | 5            | •       |    |       |       |          |        |

| ×    | Exit                          | Alt+F4       | 4       |    |       |       |          |        |

| _    |                               |              |         | 1  |       |       |          |        |

|      |                               |              |         |    |       |       |          |        |

|      |                               |              |         |    |       |       |          |        |

|      |                               |              |         |    |       |       |          |        |

# Figure 7. Create New Project

| New Project                                                               |                 |                        | 1 · · · · · · · · · · · · · · · · · · · |                  |                                                                                                                   | ? <mark>x</mark> |

|---------------------------------------------------------------------------|-----------------|------------------------|-----------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|------------------|

| Recent     Installed     Templates     Other Project T     F TwinCAT Meas |                 | .NET Framework 4.5     | Sort by: Default Project (XML format)   | TwinCAT Projects | Search Installed Templates (Ctrl+<br><b>Type:</b> TwinCAT Projects<br>TwinCAT XAE System Manager<br>Configuration |                  |

| TwinCAT Projet<br>Samples<br>D Online                                     | cts             |                        |                                         |                  |                                                                                                                   |                  |

|                                                                           |                 |                        |                                         |                  |                                                                                                                   |                  |

|                                                                           |                 |                        | lick here to go online and find t       | emplates.        |                                                                                                                   |                  |

| <u>N</u> ame:                                                             | iceK2GEtherCAT[ |                        |                                         |                  |                                                                                                                   |                  |

| Location:                                                                 |                 | strator\Documents\Visu | al Studio 2013\Projects                 | Browse           |                                                                                                                   |                  |

| Solution na <u>m</u> e:                                                   | iceK2GEtherCATE | Jemo                   |                                         |                  | Create directory for solution                                                                                     | Cancel           |

Figure 8. New TwinCAT XAE Project

4. On first occurance, the user must set the PC's Ethernet port, which is used as the EtherCAT port. Go to TwinCAT > Show Realtime Ethernet Compatible Devices, as shown in Figure 9.

#### Figure 9. Show Realtime Ethernet Compatible Devices

5. Select the Ethernet port from the list of compatible devices, and press Install. This installs a Beckhoff EtherCAT driver. When installed, the Ethernet port appears in Installed and ready to use devices, as shown in Figure 10.

| hernet Adapters                                                    |                                          | pdate List |

|--------------------------------------------------------------------|------------------------------------------|------------|

| Installed and ready to use devices Local Area Connection 2 - Twint | CAT-Intel PCI Ethernet Adapter (Gigabit) | Install    |

| 🗉 💽 Compatible devices                                             |                                          | Bind       |

| 🖳 💽 Incompatible devices                                           | 82579LM Gigabit Network Connection       | Unbind     |

| Disabled devices                                                   |                                          | Enable     |

|                                                                    |                                          | Disable    |

|                                                                    |                                          |            |

# Figure 10. Installed and Ready to Use Devices

Ţexas

www.ti.com

TRUMENTS

Introduction

- www.ti.com

- In Solution Explorer, go to the new TwinCAT project > I/0 > right click on Devices, and select Scan as shown in Figure 11. Press OK in the next dialog to start scanning for EtherCAT devices. If Scan Boxes is grayed out, select TWINCAT > Restart TwinCAT (Config Mode).

| · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CATDemo - Microsoft Visual St |              |            |     |       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|------------|-----|-------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               | EBUG TWINCA  |            | PLC | TOOLS | SC |

| G - O   17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 🗇 - 😩 💾 📲 🕺 🗗               | 自じ・ペ         | - 🕨 Attach | -   |       |    |

| ) iir 🖪 🔳 🗸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 👌 🔨 🎯 🏷 🕹 🕹                   |              | • • ·      |     | Ŧ     | ≥  |

| Solution Explorer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               | <b>▼</b> ₽ × |            |     |       |    |

| o ⊖ ☆ `o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 🗇 🖌 🗕                       |              |            |     |       |    |

| Search Solution Ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | plorer (Ctrl+;)               | <u>- م</u>   |            |     |       |    |

| reek20etr     index20etr     in | ON                            |              | _          |     |       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Add New Item                  | Ins          |            |     |       |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Add Existing Item             | Shift+Alt+A  |            |     |       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Export EAP Config File        |              |            |     |       |    |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Scan                          |              |            |     |       |    |

| م<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Paste                         | Ctrl+V       |            |     |       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Paste with Links              |              |            |     |       |    |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |            |     |       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |              |            |     |       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |              |            |     |       |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |              |            |     |       |    |

Figure 11. Select Scan

7. When an EtherCAT compatible device has been detected on this Ethernet port, the dialog shown in Figure 12 appears. There is a tick mark next to the adapter to which the K2G ICE board is connected. Press OK and confirm to start Scan for boxes.

#### Figure 12. I/O Devices Found

| 1 | new I/O devices found |                                                       | ×                                          |

|---|-----------------------|-------------------------------------------------------|--------------------------------------------|

|   | Device 2 (EtherCAT)   | [Local Area Connection 2 (TwinCAT-Intel PCI Ethernet] | OK<br>Cancel<br>Select All<br>Unselect All |

|   |                       |                                                       |                                            |

8. The TI device is listed Box n (TIESC-003). Press Yes to activate Free Run, as shown in Figure 13.

# Figure 13. Activate Free Run

| Microsoft Visual Studio |       |

|-------------------------|-------|

| Activate Free           | : Run |

| Yes                     | No    |

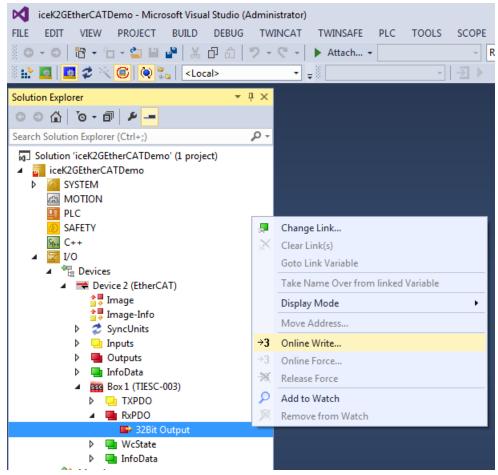

Expand the box to see Process Data Inputs (PDI) and Outputs (PDO). Right-click Box n > RxPDO > 32Bit Output and select Online Write, as shown in Figure 14.

Figure 14. Online Write

10. Enter the value in hexadecimal format, where each bit in the LSB represents an output, as shown in Figure 15.

| Set Value Dia | log             | <b>X</b> |

|---------------|-----------------|----------|

| Dec:          | 170             | ОК       |

| Hex:          | 0x0000004A      | Cancel   |

| Float:        | 2.3822074e-043  |          |

|               |                 |          |

| Bool:         | 0 1             | Hex Edit |

| Binary:       | AA 00 00 00     | 4        |

| Bit Size:     | ◎1 ◎8 ◎16 ⑧32 ◎ | 64 🔘 ?   |

#### Figure 15. Set Value Dialog

11. Changing the LED value sets and clears the appropriate industrial LEDs on the K2G ICE board.

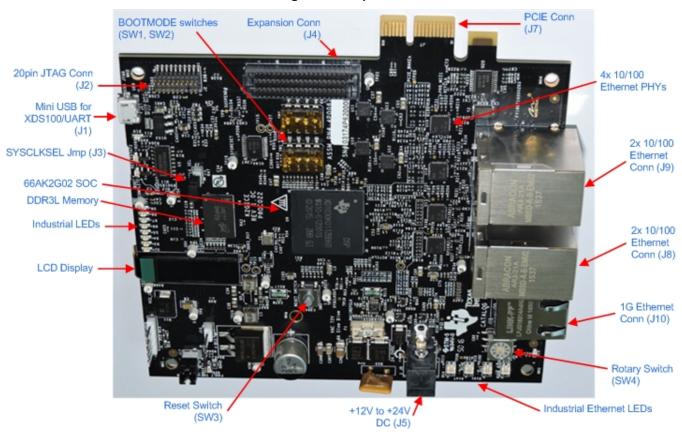

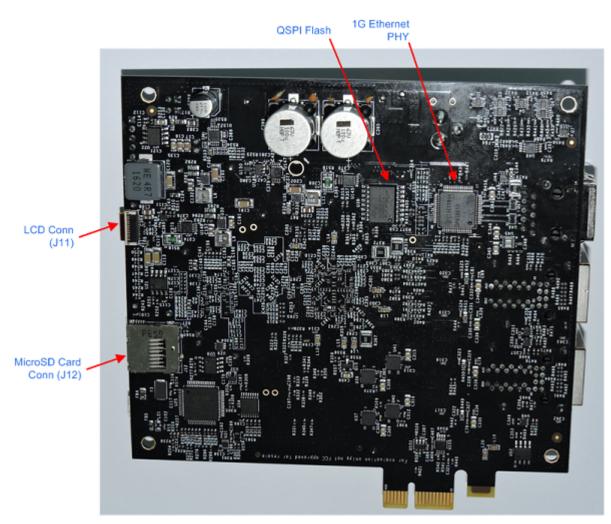

# 1.5 System Overview

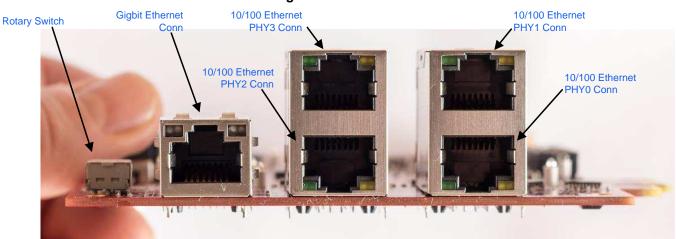

The top and the bottom pictorial views of the K2G ICE are shown in Figure 16 and Figure 17. The side view identifies the position of the Ethernet connectors.

#### Figure 16. Top View

Figure 17. Bottom View

Figure 18. Side View

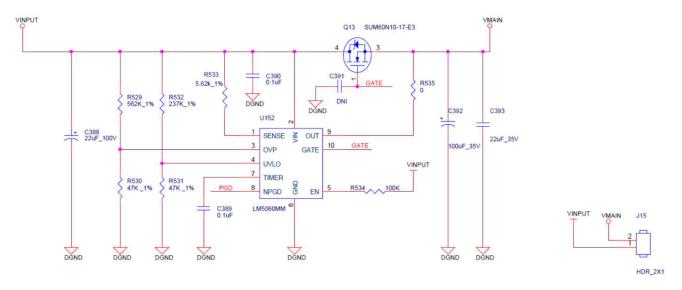

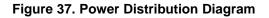

# 1.6 Power Supply

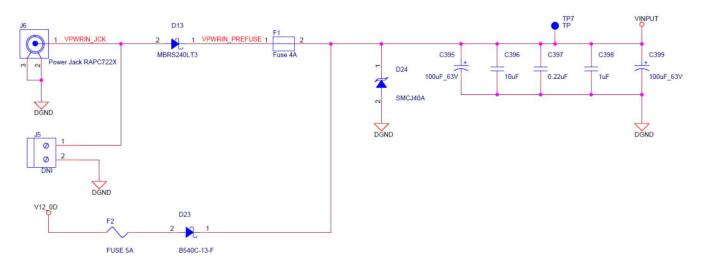

The K2G ICE can be powered from one of two sources: a single external power supply connected to the DC power jack (J6), or the 12-V supply pins on the PCIE edge connector. The power supply circuit is designed to allow the use of either a +24-V / 2.5-A DC (60-W) external power supply or a +12-V / 5-A DC (60-W) external power supply. A power ANDing circuit is included in the design, which prevents damage if a +24-V external supply is connected while the board is installed in a PCIE backplane. The +24-V supply is used to power the board in that condition.

Due to regulatory requirements, Texas Instruments cannot provide an external power supply. The K2G ICE has been tested with the CUI SDI65-24-U-P5 +24-V and the CUI SDI65-12-U-P5 +12-V power supplies, which can be purchased from distributors. Links to the supplies are shown below. A power cable can be used with a laboratory supply.

CUI SDI65-12-U-P5

http://www.digikey.com/product-detail/en/cui-inc/SDI65-12-U-P5/102-3417-ND/5277850

CUI SDI65-24-U-P5

http://www.digikey.com/product-detail/en/cui-inc/SDI65-24-U-P5/102-3418-ND/5277851

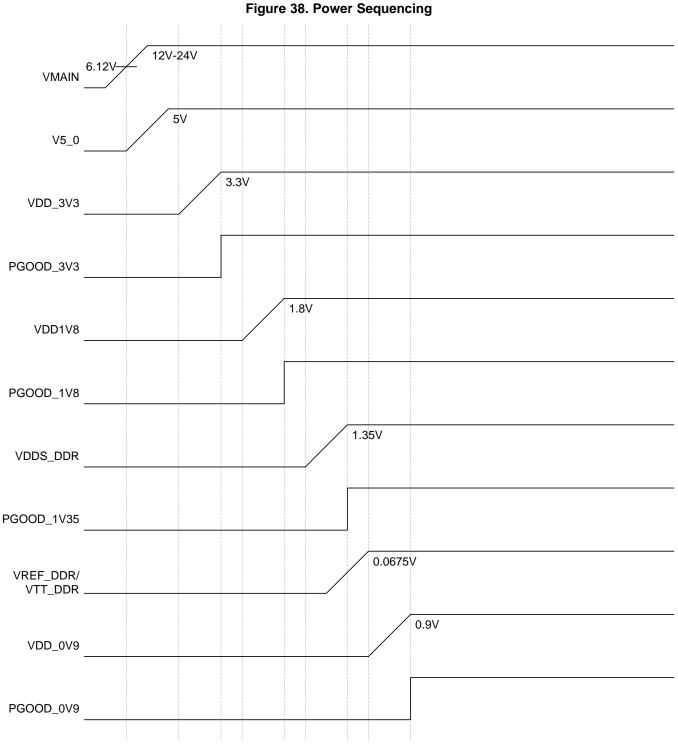

The input voltage is converted into required voltage levels using individual DC-DC converters. These are shown in Table 1.

| Regulator | Purpose             |

|-----------|---------------------|

| TPS54531  | 5V Generation       |

| TLV62084  | 3V3 Generation      |

| TLV62084  | 1V8 Generation      |

| TLV62080  | 1V35 Generation     |

| LP2996A   | DDR3 VTT Generation |

| TPS62180  | 0V9 Generation      |

| TPS22945  | LCD Backlight       |

#### Table 1. Voltage Rail Power Supplies

# 1.7 Instructions for Mechanical Assembly

The K2G ICE can be used with or without the mechanical standoffs provided with the board. Standoff mounting is described in the K2G ICE Mechanical Accessories Mounting Instructions.

# 2 Overview of the K2G ICE

This chapter provides an overview of the different interfaces and circuits on the K2G ICE.

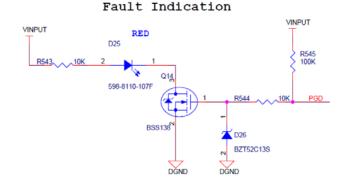

# 2.1 Voltage Protection Circuit

The voltage protection circuit on the K2G ICE protects the board from overvoltage, undervoltage, transient voltage, and reverse voltage input cases. The safe operation input voltage range is 11 V to 13 V. Any voltage not in this range is considered as fault, and the voltage protection circuit isolates the board from this input. A wide input voltage range is accepted to accommodate both the 24-V input and the 12-V PCIE supply voltage. LED D25 indicates if the DC input applied to board is in a safe input range.

#### Figure 19. Overvoltage Protection Circuit

# Figure 20. Overvoltage Fault Indicator

| Condition                     | LED Status(D25) |

|-------------------------------|-----------------|

| VINPUT between 11 to 26V      | OFF             |

| VINPUT above 26V or below 11V | ои              |

# 2.2 Voltage ANDing Circuit

Although it is not recommended, both the 12 V from the PCIE connector and 24 V from the power input may be present at the same time. To protect the board from power supply conflicts, the voltage ANDing circuit was included. If only the 12 V from the PCIE edge connector is present, D23 is forward biased, allowing current to flow. If 24 V is provided to J6, D13 is forward biased. If both 24 V on J6 and 12 V on the PCIE edge connector are both present. D13 is forward biased and D23 is reversed biased, allowing the 24 V to take precedence, and blocking any current flow back to the PCIE connector.

Overview of the K2G ICE

www.ti.com

# Figure 21. Voltage ANDing Circuit

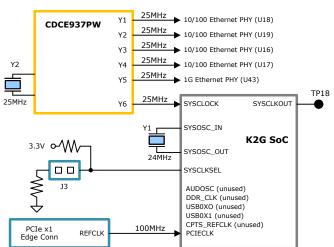

# 2.3 Clocking

The K2G ICE EVM derives all internal clocks, with the exception of the PCIE\_CLK, from a single clock input. That clock input can be either the internal oscillator using crystal Y1, or an external clock generator connected to SYS\_CLK\_P/N. The PCIE clock is only present if the K2G EVM is inserted into a PCIE backplane. Software should not attempt to access the PCIE subsystem unless the PCIECLK is present.

The source for the system clock can be sourced from the 24-MHz crystal connected to the SYSOSC pins, or from the 25 MHz provided by the CDCE937PW clock generator. J3 determine which clock is used as the source for the system clock. If a jumper is installed on J3, then SYSCLKSEL is low and the 24-Mhz crystal is used. If the jumper is not installed, then SYSCLKSEL is high and the 25-Mhz SYSCLKP/N input is used. PLL settings for all PLLs must be modified based on the system clock selected.

The DDR clock input to the DDR PLL is derived from the system clock selected, thus no clock is connected to the DDRCLK pins. The AUDOSC, USBOX0, USBOX1, and CPTS\_REFCLK clock inputs are not used in this design.

Crystals:

- Y1 24-MHz system clock

- Y2 25 MHz to CDCE937PW clock generator

Clock generator outputs:

- Y1 25-MHz PR0 MII0 PDP83822 10/100 Ethernet PHY

- Y2 25-MHz PR0 MII1 PDP83822 10/100 Ethernet PHY

- Y3 25-MHz PR1 MII0 PDP83822 10/100 Ethernet PHY

- Y4 25-MHz PR1 MII1 PDP83822 10/100 Ethernet PHY

- Y5 25-MHz RMII DP83867 Gbit Ethernet PHY

- Y6 25-MHz K2G SYS\_CLK\_P/N clock input

Figure 22. Clock Inputs

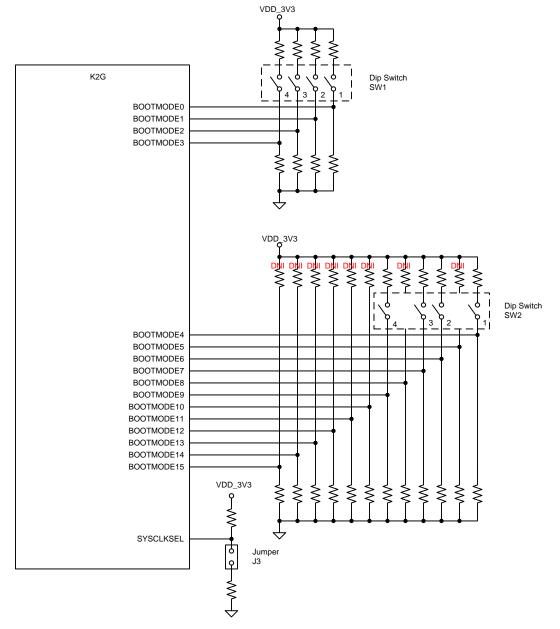

# 2.4 Bootmode Switches

The K2G ICE includes two dip switches, each with four individual switches. These are connected to eight of the sixteen bootmode signals. The K2G ICE is not designed to support all bootmodes available to the K2G, although all bootmodes may be selected with the available switches. Only the bootmodes defined in Table 2 have been tested with the K2G ICE. In addition to the bootmode bits, switches are provided for four additional bootmode pins used to defined specific conditions for each of the bootmodes available. For more information, see the BOOTMODE Pins Description section in the K2G TRM.

# Figure 23. Bootmode Selection Switches Schematic

The dip switches are located just above the expansion connector, as shown in Figure 24. Bootmode switches should be set before any expansion board is installed.

# Figure 24. Bootmode Selection Switches

Table 2. Supported Bootmodes

| Bestmede             | Clock |     | SW2 |     |     | SW1 |     |     |     | J3    | BOOTMODE value   |

|----------------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-------|------------------|

| Bootmode             | CIOCK | 4   | 3   | 2   | 1   | 4   | 3   | 2   | 1   | 33    | BOOTWODE value   |

| No<br>Boot/Emulation | 24MHz | off | off | on  | off | off | off | off | off | short | 000000001000000  |

| No<br>Boot/Emulation | 25MHz | off | on  | off | off | off | off | off | off | open  | 00000001000000   |

| PCIE endpoint        | 24MHz | off | off | on  | off | off | off | off | on  | short | 000000001000001  |

| PCIE endpoint        | 25MHz | off | on  | off | off | off | off | off | on  | open  | 00000001000001   |

| QSPI as 48MHz        | 24MHz | off | off | on  | off | on  | off | off | off | short | 000000001001000  |

| QSPI as 48MHz        | 25MHz | off | on  | off | off | on  | off | off | off | open  | 000000010001000  |

| QSPI as 96MHz        | 24MHz | off | off | on  | off | on  | off | off | on  | short | 000000001001001  |

| QSPI as 96MHz        | 25MHz | off | on  | off | off | on  | off | off | on  | open  | 000000010001001  |

| SDcard               | 24MHz | on  | off | on  | off | on  | on  | on  | off | short | 0000001001001110 |

| SDcard               | 25MHz | on  | on  | off | off | on  | on  | on  | off | open  | 0000001010001110 |

| UART                 | 24MHz | off | off | on  | off | on  | on  | on  | on  | short | 000000001001111  |

| UART                 | 25MHz | off | on  | off | off | on  | on  | on  | on  | open  | 000000010001111  |

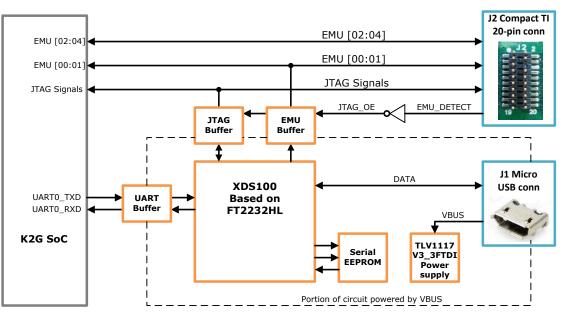

# 2.5 UART and JTAG Emulation Circuit

The K2G ICE provides support for two emulation solutions. An XDS100 circuit is included in the design of the board, which provides emulation capability without the use of external emulation pod. The XDS100 circuit connects directly to a computer using USB.

In addition, a compact TI 20-pin connector is included in the design. An external emulator pod may be connected to the 20-pin connector as an alternative method of JTAG connectivity. Connecting an external pod automatically disables the on-board XDS100 circuit.

More information on JTAG connections may be found on the JTAG Connectors page on TI.com.

# 2.5.1 2.5.1 XDS100 Circuit

The XDS100 emulation circuit is based on the FTDI dual high-speed USB to multipurpose IO device. The serial EEPROM contains the XDS100 configuration, which supports the JTAG emulation on one port and a UART connection on the second port. Connecting a USB cable between the computer and J1 allows a JTAG connection to Code Composer Studio and a UART connection using VCP. More information on the XDS100 can be found here.

The XDS100 section of the circuit is powered by the VBUS voltage provided by USB. Connection to both the JTAG and the UART is maintained even if the source voltage for the K2G ICE has been removed.

# 2.5.2 UART

The second port of the FT2232HL is used for a UART-to-USB interface. When the K2G ICE is connected to a computer using the provided USB cable, the computer can establish a Virtual Com Port which can be used with a terminal emulation program. The FT2232HL is powered from the VBUS voltage present on the USB connector. The UART remains connected even if the power is removed from the K2G ICE. The FT2232HL is connected to the K2G UART0 port through a voltage converter buffer.

# Figure 25. JTAG Circuit

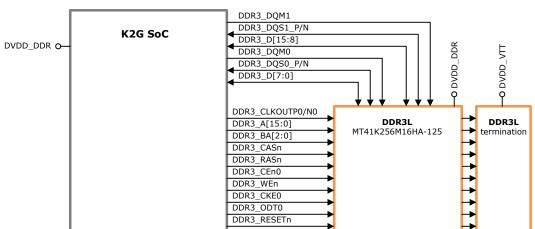

# 2.6 DDR3 Memory

K2G SoC supports x36 bit (32-bit data + 4-bit ECC) DDR3L; however, the K2G ICE uses 16-bit data. A single 4Gbit (256Mx16) DDR3L chip MT41K256M16HA from Micron is used to obtain a memory size of 512MByte.

The DDR3L chip is routed as a point-to-point connection with VTT termination for the data lines, as shown in Figure 26.

#### Figure 26. DDR3 Memory Circuit

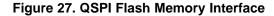

# 2.7 QSPI Flash

The K2G QSPI interface is connected to a Spansion S25FL256SAGMFIR01 flash memory component. QSPI CS0 is used to access this device. The QSPI flash reset signal is connected to the output of an AND gate. The AND gate inputs are connected to the PORn signal and a GPIO from the K2G. The GPIO is pulled high, allowing the QSPI flash to exit reset when the PORn signal goes high. This allows the QSPI flash to be used as a boot device. The GPIO connected to the second AND input allows the K2G to reset the QSPI flash if a forced reset is needed during operation.

# 2.8 SD Memory Card

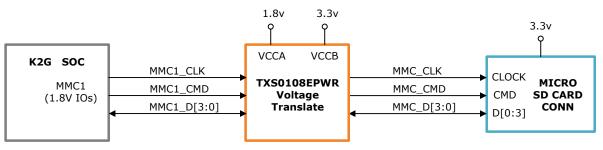

The K2G ICE includes a microSD card slot connected to the MMC1 interface of the K2G. MMC1 uses 1.8-V I/Os, while the microSD card operates at 3.3 V. A voltage translator is included to transition the signals between the two voltage domains. While the K2G includes the MMC0 interface, which uses 3.3-V I/Os, it is shared with the outputs of the industrial PRU, which is used in this design.

#### Figure 28. microSD Memory Card Interface

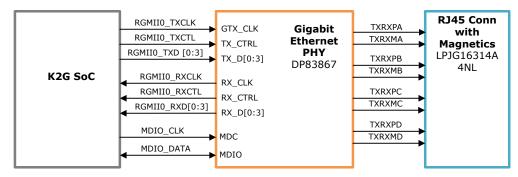

#### 2.9 Gigabit Ethernet

The K2G ICE includes an RGMII connection between the DP83867 Gigabit Ethernet PHY and the network subsystem (NSS) of the SoC using RGMII0. The default configuration of the DP83867 is determined using a number of resistor value pull-ups and pull-downs on specific pins of the PHY.

#### Figure 29. Gigabit Ethernet Interface

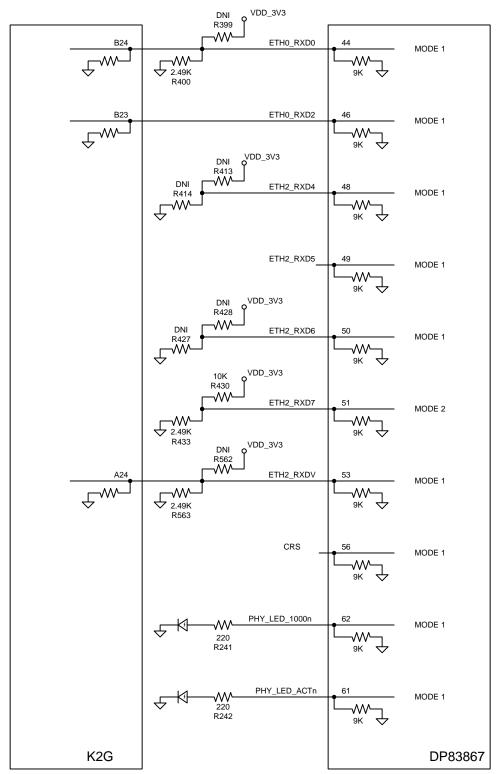

#### 2.9.1 Gigabit Ethernet PHY Default Configuration

The default configuration of the DP83867 is determined using a number of resistor pull-up and pull-down values on specific pins of the PHY. Depending on the values installed, each of the configuration pins can be set to one of four modes. A configuration pin or groups of configuration pins are used to set the configuration of the PHY after it is released from reset. Configuration settings differ depending on the package type selected for the PHY. The K2G ICE uses the 64-pin QFP package, designated with the PAP suffix, which supports both the GMII and RGMII interface. A 48-pin QFN package, designated with the RGZ suffix and which only supports RGMII, is also available.

#### 2.9.2 Gigabit Ethernet Resistor Strapping

The DP83867 PHY use a four-level configuration based on resistor strappings, which generate four distinct voltage ranges. These resistors are connected to the RX data and control pins, which are normally driven by the PHY and are inputs to the K2G. When 3.3-v I/O voltages are selected, the voltage ranges are shown below.

Mode 1 - 0 V to 0.3234 V

Mode 2 - 0.4884 V to 0.5973 V

Mode 3 - 0.7491 V to 0.9141 V

Mode 4 - 2.2902 V to 3.3 V

Mid-level voltages can result in high leakage currents and are detrimental to the long-term reliability of the K2G I/O cells connected to the strapping resistor. To avoid this situation, only pull-up and pull-down resistors are used to pull the I/O cells as close as possible to either 0 V or 3.3 V. This limits the selection of configurations to those that can be selected by using Mode 1 or Mode 4. Both the DP83867 and the K2G include internal pulling resistors. The value of the external pull resistors are selected to provide a voltage at the pins of the K2G as close to ground or 3.3 V as possible.

# Figure 30. Gigabit Ethernet Pulling Resistors

Consult the data manual of the DP83867 for more details on configuring the PHY. The DP83867 strapping can be read from the STRAP\_STS1 and STRAP\_STS2 registers. The strapping resistors on the K2G ICE configures the DP83867, as show in Table 3.

| Bit            | BIT NAME                | Value | Description                                                 |

|----------------|-------------------------|-------|-------------------------------------------------------------|

| STRAP_STS1.15  | STRAP_MIRROR_EN         | 0     | Port mirroring disabled                                     |

| STRAP_STS1.14  | STRAP_LINK_DOWNSHIFT_EN | 0     | Link downshift disabled                                     |

| STRAP_STS1.13  | STRAP_CLK_OUT_DIS       | 1     | Clock output disabled                                       |

| STRAP_STS1.12  | STRAP_RGMII_DIS         | 0     | RGMII enabled                                               |

| STRAP_STS1.10  | STRAP_AMDIX_DIS         | 0     | Auto-MDIX enabled                                           |

| STRAP_STS1.9   | STRAP_FORCE_MDI_X       | 0     | Force MDI (not used because auto-MDIX is enabled)           |

| STRAP_STS1.8   | STRAP_HD_EN             | 0     | Full duplex enabled (not used because auto-MDIX is enabled) |

| STRAP_STS1.7   | STRAP_ANEG_DIS          | 0     | Auto-negotiation enabled                                    |

| STRAP_STS1.6:5 | STRAP_SPEED_SEL         | 00    | Advertise 10/100/1000                                       |

| STRAP_STS1.4:0 | STRAP_PHY_ADD           | 00000 | PHY address = 0x00                                          |

| STRAP_STS2.10  | STRAP_FLD               | 0     | Fast link detect disabled                                   |

# Table 3. Gigabit PHY Configuration

# 2.9.3 Gigabit Ethernet Configuration

The DP83867 PHY must be configured using the MDIO register accesses for proper operation of the interface on the K2G ICE.

First, the value of 0x170 must be written to register 0x31 of the DP83867 for proper operation of the autonegotiation function.

Secondly, the DP83867 includes the ability to delay the RGMII TX clock and RX clock relative to the data signals, to compensate for delays introduced in the routing of the RGMII interface. An application note explaining this capability is included on the product page for the DP83867. After analyzing the layout of the RGMII on the K2G ICE, there is a delay of 2.25 nsec for the RX clock and 2.25 nsec for the TX clock. The TX clock delay consists of the 2 nsec of internal delay and 0.25 nsec of PCB delay. The TX clock delay is calculated assuming that the RGMII internal TX clock delay is enabled within the K2G. In the RGMIIDCTL register (0x86), the RGMII\_TX\_DELAY\_CTRL bit field should be set to 0b0000 and the RGMII\_RX\_DELAY\_CTRL field should be set to 0b1000. In the RGMIICTL register (0x32), the RGMII\_TX\_CLK\_DELAY bit should be set to 1 and the RGMII\_RX\_CLK\_DELAY bit should be set to 1 to enable the clock shift specified in the RGMIIDCTL register.

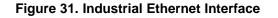

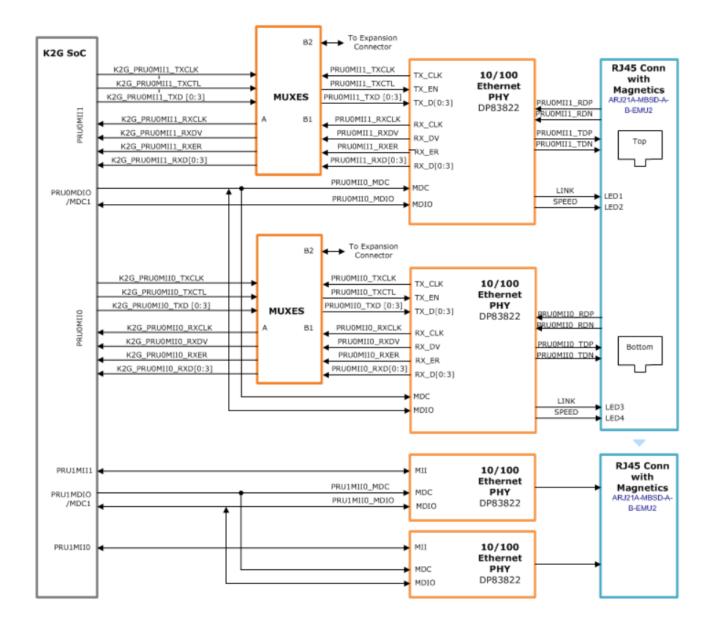

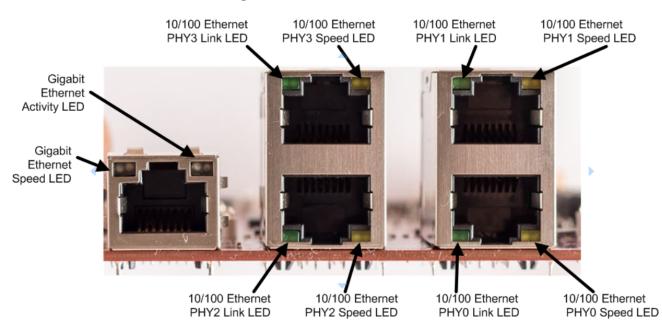

# 2.10 Industrial Ethernet

The K2G SoC includes two programmable real-time unit subsystems and industrial communications subsystems (PRU-ICSS), which can be configured to support numerous industrial protocols. Each PRU-ICSS unit can support two MII interfaces for connection to two 10/100 Ethernet PHYs. The K2G ICE includes four DP83822I 10/100 Industrial Ethernet PHYs providing four Ethernet connections. The signals for PRU0 are connected to muxes, allowing this interface to be connected to the expansion connector.

24 K2G Industrial Communications Engine (K2G ICE)

#### 2.10.1 Industrial Ethernet PHY Default Configuration

The default configuration of the DP83822 is determined using a number of resistor pull-up and pull-down values on specific pins of the PHY. Depending on the values installed, each of the configuration pins can be set to one of four modes. A configuration pin or groups of configuration pins are used to set the configuration of the PHY after it is released from reset. Configuration settings differ depending on the package type selected for the PHY.

#### 2.10.2 Industrial Ethernet Resistor Strapping

The DP83822 PHY use a four-level configuration based on resistor strappings, which generate four distinct voltages ranges. These resistors are connected to the RX data and control pins, which are normally driven by the PHY and are inputs to the K2G. These voltage ranges are shown below.

Mode 1 – 0 V to 0.3234 V

Mode 2 - 0.4884 V to 0.5973 V

Mode 3 – 0.7491 V to 0.9141 V

Mode 4 - 2.2902 V to 3.3 V

Mid-level voltages can result in high leakage currents and are detrimental to the long-term reliability of the K2G I/O cells connected to the strapping resistor. To avoid this situation, only pull-up and pull-down resistors are used to pull the I/O cells as close as possible to either 0 V or 3.3 V. This limits the selection of configurations to those that can be selected by using Mode 1 or Mode 4. Both the DP83822 and the K2G include internal pulling resistors. The value of the external pull resistors is selected to provide a voltage at the pins of the K2G as close to ground or 3.3 V as possible.

MODE 0 Rhi = 1.0K, Rlo = DNI MODE 0 Rhi = DNI, Rlo = 1.0K Rhi1 VDD\_3V3 R132 R141 VDD\_3V3 0 50K R396 R391 ÷~ PHY0 - MODE 1 -₩ PRUxMIIx\_COL 29 PHY1 - MODE 4 PHY2 - MODE 1 -₩ PHY3 - MODE 4  $\Leftrightarrow$ enabled Rhi2 R131 R140 VDD\_3V3 R397 R392 R154 R163 R409 R404 PHY0 - MODE 1 -₩ PRUxMIIx\_RXD0 30 PHY1 - MODE 1 PHY2 - MODE 4 Rid2 R153 R162 R410 R405 ₩-PHY3 - MODE 4 Ĵ £ enabled 9K DNI R130 R139 VDD\_3V3 R113 R117 -WV-PRUxMIIx\_RXD1 31 MODE 1 \_\_\_\_́У́2.49К -wv-∽₩ £ Ĵ 9K enabled VDD\_3V3 R129 R1380 R200 T R152 R161 R121 R125 R398 R393 PRUxMIIx\_RXD2 32 MODE 1 ↓ 2.49K ÷W £ enabled 9K ÷ DNI R128 R1370 VDD\_3V3 R112 R116 R151 R160 R411 R406 PRUxMIIx\_RXD3 MODE 1 -wv--w  $\sim$ £ √VV 2.49K Ŷ enabled 9K R150 R159 R120 R124 -0 VDD\_3V3 kł -//// w 1.0K DNI R136 R145 R443 R442 R445 R444 50K R394 R389 9 -WV--₩ w -₩ Ę. 17 MODE 4 PRUxMIIx\_LINKLED DNI R158 R167 enabled 1.0K R134 R143 VDD\_3V3 R395 R390 J R407 R402 50K ₩\_3 -₩ PRUxMIIx\_CRS 27 MODE 4 1.0K R133 R142 VDD\_3V3 R114 R118 R156 R165 50K R408 R403 q ₩~- $\sim$ PRUxMIIx\_RXER 28 MODE 4 -ww-Ŷ enabled R135 R144 VDD\_3V3 R115 R119 DNI R155 R164 R122 R126  $\sim$ PRUxMIIx\_RXDV 26 MODE 1 ~~~ ↓ v v v 2.49K -W ₩ Ĵ ӡ enabled 9K R157 R166 R123 R127 K2G DP83822

Figure 32. Industrial Ethernet Pulling Resistors

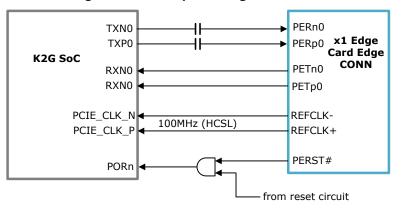

# 2.11 PCIE Edge Connector

The K2G ICE includes a PCIE x1 edge connector as defined by the PCI Express Electromechanical Specification, Rev 2.0. While the edge connector and the board thickness are compatible with that standard, the K2G ICE was not designed to meet all the requirements for the Electromechanical specification, and is not designed to fit into a standard PC chassis. No I/O bracket is available, and the EVM is not compliant with the PCB form factor or component height restrictions.

Although the K2G can be configured as a PCIE root-complex or endpoint, the K2G ICE only supports PCIE endpoint operations. The PCIE reference clock is only provided by the PCIE connector. No accesses to the PCIE portion of the K2G SOC should be performed unless a PCIE reference clock is present on the PCIE edge connector.

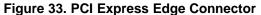

# 2.12 I2C

The K2G ICE uses two of the three available I2C interfaces: I2C0 and I2C1. I2C0 is connected to the clock generator and the expansion connector. I2C1 is used for the additional peripheral devices needed by the K2G ICE. The devices connected to these interfaces and their function are presented in the following sections.

#### Figure 34. I2C Connections

## 2.12.1 CDCE937PW 25-MHz Clock Generator

The CDCE937PW clock generator is preprogrammed to generate the 25-MHz clock outputs needed by the Ethernet PHYs, and for the external clock input to the K2G SoC. No additional programming is required.

#### 2.12.2 I2C on Expansion Connector

Additional I2C devices may be mounted on a daughtercard connected to the expansion connector. All addresses, with the exception of 0x6D, are available for devices on the expansion connector connected to I2C0.

# 2.12.3 CAT24C256W Board ID Memory

The K2G ICE board includes a CAT24C256W I2C EEPROM ID memory. The initial 72 bytes of the ID memory is preprogrammed with identification information for each board. The remaining 32696 is available to the user for data or code storage. **The initial 72 bytes of the ID memory should never be overwritten**.

| Name                      | Size<br>(bytes) | Contents                                 | Description                                                                                             |  |  |  |

|---------------------------|-----------------|------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Header                    | 4               | MSB 0xEE3355AA LSB                       | Start code                                                                                              |  |  |  |

| Board name                | 8               | 66AK2GIC                                 | Board name in ASCII                                                                                     |  |  |  |

| Version                   | 4               | 1.0B                                     | Hardware revision code in ASCII                                                                         |  |  |  |

| Serial number 1           |                 | WWYY4P62nnnn                             | WW – Week of production<br>YY – Year of production<br>4P62 – K2G ICE board code<br>nnnn – Serial number |  |  |  |

| Configuration option      | 32              |                                          | Reserved for board configuration codes                                                                  |  |  |  |

| Ethernet MAC address #0   | 6               | MSB to LSB - MAC-ID<br>70-FF-76-1C-xx-xx | This is the first of a block of six addresses available for the industrial interface ports              |  |  |  |

| Ethernet MAC address #5 6 |                 | MSB to LSB - MAC-ID<br>70-FF-76-1C-xx-xx | This is the last of a block of six addresses available for the industrial interface ports               |  |  |  |

| Available                 | 32696           |                                          | Available space for user data or code                                                                   |  |  |  |

# Table 4. ID Memory Header Information

#### 2.12.4 PCA9536DGK/ ND3FR10P Rotary Switch

The K2G ICE board includes a PCA9536DGK I2C 4-bit IO Expander connected to a ND3FR10P 10position rotary switch. Selecting a value on the switch presents a four-bit binary code to the PCA9536. This value can be read using the I2C interface.

#### 2.12.5 OSD9616P0992-10 LCD Display

The K2G ICE board includes a OSD9616P0992-10 96×16 pixel LCD display. The display is based on the SSD1606 controller. Communications with the controller uses two slave addresses, 0x3C and 0x3D, for I2C1.

#### 2.12.6 TPIC2810 LED Driver