**Features**

# **4-Channel Low Capacitance Dual-Voltage ESD Protection Array**

### ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM**

## CASE 517BC

30V = Specific Device Code = Date Code = Pb-Free Package

## • No Need for External Bypass Capacitors • Each I/O Pin Can Withstand Over 1000 ESD Strikes\*

• High Voltage Zener Diode Protects Supply Rail

±8 kV Contact Discharge (Pins 1–3) ±15 kV Contact Discharge (Pin 4)

• Low Channel Input Capacitance

• 3 Channels of Low Voltage ESD Protection • 1 Channel of High Voltage ESD Protection

• Provides ESD Protection to IEC61000-4-2 Level 4:

• These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

• Minimal Capacitance Change with Temperature and Voltage

V<sub>n</sub> (Internal) O Pin 4 CH1 O Pin CH2 O Pin 2 H۷ CH3 O Pin 3 Pins 6 - 8 ♥ Pin 5 GND

NOTE: Note: Pins 5, and 6 to 8 are connected to a common substrate.

Figure 1. Electrical Schematic

# **PINOUT** DAP **Bottom View** (Pins up View)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

<sup>\*</sup>Standard test condition is IEC61000-4-2 level 4 test circuit with each pin subjected to ±8 kV contact discharge for 1000 pulses. Discharges are timed at 1 second intervals and all 1000 strikes are completed in one continuous test run. The part is then subjected to standard production test to verify that all of the tested parameters are within spec after the 1000 strikes.

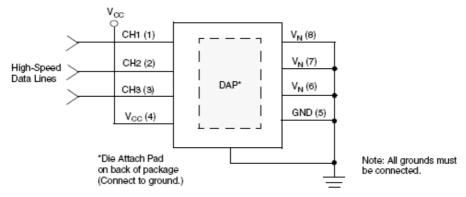

Figure 2. Typical Application

#### **PIN DESCRIPTIONS**

|     | 4-CHANNEL, 8-LEAD, uDFN-8 PACKAGE |                    |                                |  |  |

|-----|-----------------------------------|--------------------|--------------------------------|--|--|

| Pin | Name                              | Туре               | Description                    |  |  |

| 1   | CH1                               | I/O                | LV Low-capacitance ESD Channel |  |  |

| 2   | CH2                               | I/O                | LV Low-capacitance ESD Channel |  |  |

| 3   | CH3                               | I/O                | LV Low-capacitance ESD Channel |  |  |

| 4   | V <sub>CC</sub>                   | HV V <sub>DD</sub> | HV ESD Channel                 |  |  |

| 5   | GND                               |                    | Ground                         |  |  |

| 6   | V <sub>N</sub>                    |                    | Negative Voltage Supply Rail   |  |  |

| 7   | V <sub>N</sub>                    |                    | Negative Voltage Supply Rail   |  |  |

| 8   | V <sub>N</sub>                    |                    | Negative Voltage Supply Rail   |  |  |

| DAP | GND                               |                    | Die Attach Pad (Ground)        |  |  |

#### **ORDERING INFORMATION**

| Device (Note 1) | # of Channels | Leads | Part Marking | Package                     | Shipping <sup>†</sup> |

|-----------------|---------------|-------|--------------|-----------------------------|-----------------------|

| ESD7554MUT2G    | 4             | 8     | 30V          | uDFN-8, 0.4 mm<br>(Pb-Free) | Tape & Reel           |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>1.</sup> Parts are shipped in Tape and Reel form unless otherwise specified.

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                             | Rating      | Unit |

|-------------------------------------------------------|-------------|------|

| DC Voltage on Low-voltage Pins                        | 6           | V    |

| DC Voltage on High-voltage Pins (V <sub>CC</sub> pin) | 29          | V    |

| Operating Temperature Range                           | -40 to +85  | °C   |

| Storage Temperature Range                             | −65 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### STANDARD OPERATING CONDITIONS

| Parameter                   | Rating     | Unit |

|-----------------------------|------------|------|

| Operating Temperature Range | -40 to +85 | °C   |

#### **ELECTRICAL OPERATING CHARACTERISTICS** (See Note 2)

| Symbol               | Parameter                                                                                                                                      | Conditions                                                                          | Min                         | Тур                          | Max  | Unit   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|------------------------------|------|--------|

| V <sub>F</sub>       | LV Diode Reverse Voltage<br>(Positive Voltage)                                                                                                 | I <sub>F</sub> = 10 mA; T <sub>A</sub> = 25°C                                       | 6.8                         | 8.2                          | 9.2  | V      |

|                      | LV Diode Forward Voltage<br>(Negative Voltage)                                                                                                 | I <sub>F</sub> = 10 mA; T <sub>A</sub> = 25°C                                       | -1.05                       | -0.9                         | -0.6 | V      |

| I <sub>LEAK</sub>    | LV Channel Leakage Current<br>(Pins 1 and 2)                                                                                                   | $T_A = -30$ °C to 65°C; $V_{IN} = 3.3V$ , $V_N = 0V$                                |                             |                              | 100  | nA     |

|                      | LV Channel Leakage Current<br>(Pin 3 only)                                                                                                     | $T_A = -30^{\circ}\text{C}$ to 65°C; $V_{IN} = 3.3 \text{ V}$ , $V_N = 0 \text{ V}$ |                             |                              | 100  | nA     |

| C <sub>IN</sub>      | LV Channel Input Capacitance                                                                                                                   | At 1 MHz, V <sub>N</sub> = 0 V, V <sub>IN</sub> = 1.65 V                            |                             | 1.2                          | 1.5  | pF     |

| ΔC <sub>IN</sub>     | LV Channel Input Capacitance<br>Matching                                                                                                       | At 1 MHz, V <sub>N</sub> = 0 V, V <sub>IN</sub> = 1.65 V                            |                             | 0.02                         |      | pF     |

| I <sub>LEAK_HV</sub> | HV Channel Leakage Current                                                                                                                     | $T_A = 25^{\circ}C; V_{CC} = 28 \text{ V}, V_N = 0 \text{ V}$                       |                             | 0.1                          | 1.0  | mA     |

| C <sub>IN_HV</sub>   | HV Channel Input Capacitance                                                                                                                   | At 1 MHz, $V_N = 0V$ , $V_{IN} = 2.5 V$                                             |                             | 30                           |      | pF     |

| V <sub>F_HV</sub>    | HV Diode Breakdown Voltage<br>Positive Voltage                                                                                                 | I <sub>F</sub> = 10 mA; T <sub>A</sub> = 25°C                                       | 30                          |                              | 35   | ٧      |

| V <sub>ESD</sub>     | ESD Protection Peak Discharge Voltage at any channel input, in system Contact discharge per IEC 61000-4-2 standard                             | T <sub>A</sub> = 25°C                                                               | ±8 (Pin 1–3)<br>±15 (Pin 4) |                              |      | kV     |

| V <sub>CL</sub>      | LV Channel Clamp Voltage (Pin 1–3)<br>Positive Transients<br>Negative Transients                                                               | $T_A = 25^{\circ}C$ , $I_{PP} = 1$ A, $t_P = 8/20 \ \mu S$                          |                             | +9.64<br>-1.75               |      | V<br>V |

| R <sub>DYN</sub>     | Dynamic Resistance LV Channel Positive Transients LV Channel Negative Transients HV Channel Positive Transients HV Channel Negative Transients | $I_{PP}$ = 1 A, $t_P$ = 8/20 $\mu$ S Any I/O pin to Ground                          |                             | 0.72<br>0.59<br>4.00<br>0.20 |      | Ω      |

<sup>2.</sup> All parameters specified at  $T_A$  =  $-40^{\circ}C$  to +85°C unless otherwise noted.

#### PERFORMANCE INFORMATION

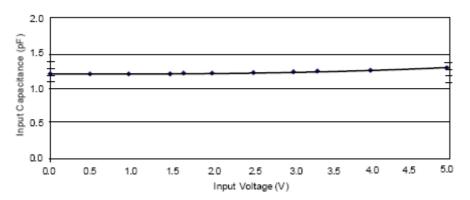

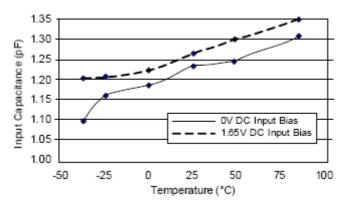

Input channel capacitance performance curves for low voltage pins

Figure 3. Typical Variation of  $C_{IN}$  vs.  $V_{IN}$  (Low Voltage Inputs, f = 1 MHz,  $V_{N}$  = 0 V)

Figure 4. Typical Variation of  $C_{IN}$  vs. Temp (Low Voltage Inputs, f = 1 MHz,  $V_N = 0$  V)

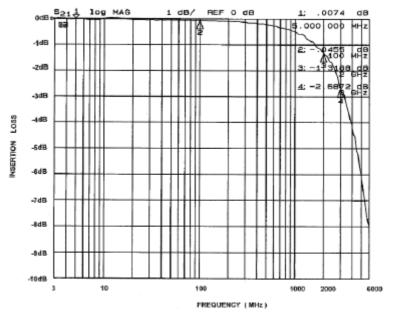

#### **PERFORMANCE INFORMATION**

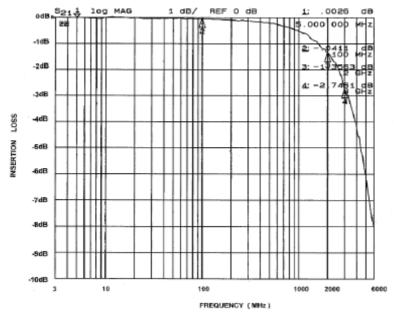

Typical filter performance for low voltage pins Nominal conditions unless specified; otherwise, 50  $\Omega$  environment

Figure 5. Channel 1 vs. All GND Pins (0 V DC Bias)

Figure 6. Channel 2 vs. All GND Pins (0 V DC Bias)

#### PERFORMANCE INFORMATION

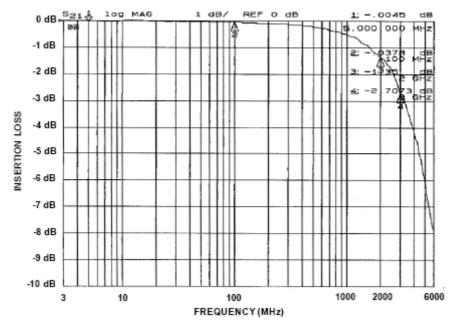

Typical filter performance for low voltage pins Nominal conditions unless specified; otherwise, 50  $\Omega$  environment

Figure 7. Channel 3 vs. All GND Pins (0 V DC Bias)

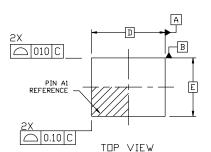

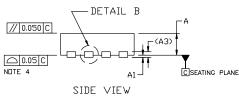

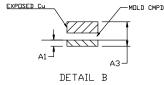

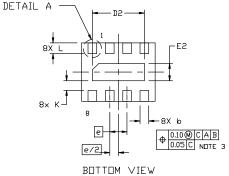

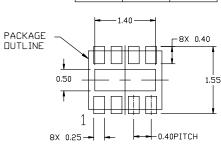

#### UDFN8, 1.7x1.35, 0.4P CASE 517BC **ISSUE A**

**DATE 11 AUG 2022**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2004.

- CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25MM FORM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PADS AS WELL AS THE TERMINALS.

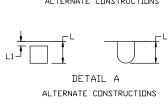

ALTERNATE CONSTRUCTIONS

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN.        | MAX. |  |

| Α   | 0.45        | 0.55 |  |

| A1  | 0.00        | 0.05 |  |

| АЗ  | 0.13 REF    |      |  |

| b   | 0.15        | 0.25 |  |

| D   | 1.70 BSC    |      |  |

| D2  | 1.10        | 1.30 |  |

| E   | 1.35        | BSC  |  |

| E2  | 0.30        | 0.50 |  |

| е   | 0.40        | BSC  |  |

| К   | 0.15        |      |  |

| L   | 0.20        | 0.30 |  |

| L1  |             | 0.05 |  |

|     |             |      |  |

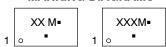

#### **GENERIC MARKING DIAGRAMS\***

XXX = Specific Device Code

= Date Code = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

RECOMMENDED MOUNTING FOOTPRINT\*

For additional information on our Pb-Free strategy and soldering details, please download the  $\ensuremath{\mathsf{IN}}$  Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

| DOCUMENT NUMBER: | 98AON47060E           | Electronic versions are uncontrolled except when accessed directly from Printed versions are uncontrolled except when stamped "CONTROLLED | , ,         |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | UDFN8, 1.7x1.35, 0.4P |                                                                                                                                           | PAGE 1 OF 1 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative