### HI-524

## 4-Channel Wideband and Video Multiplexer

FN3148 Rev 3.00 April 2002

The HI-524 is a 4-Channel CMOS analog multiplexer designed to process single-ended signals with bandwidths up to 10MHz. The chip includes a 1 of 4 decoder for channel selection and an enable input to inhibit all channels (chip select).

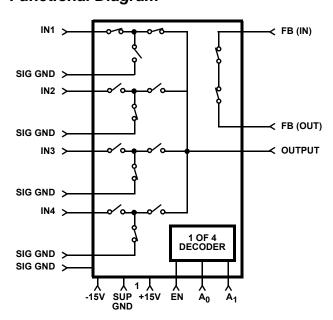

Three CMOS transmission gates are used in each channel, as compared to the single gate in more conventional CMOS multiplexers. This provides a double barrier to the unwanted coupling of signals from each input to the output. In addition, Dielectric Isolation (DI) processing helps to insure the Crosstalk is less than -60dB at 10MHz.

The HI-524 is designed to operate into a wideband buffer amplifier such as the Intersil HA-2541. The multiplexer chip includes two "ON" switches in series, for use as a feedback element with the amplifier. This feedback resistance matches and tracks the channel ON resistance, to minimize the amplifier  $V_{OS}$  and its variation with temperature.

The HI-524 is well suited to the rapid switching of video and other wideband signals in telemetry, instrumentation, radar and video systems.

## Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>(°C) | PACKAGE      | PKG. NO. |  |

|----------------|---------------------|--------------|----------|--|

| HI1-0524-5     | 0 to 75             | 18 Ld CERDIP | F18.3    |  |

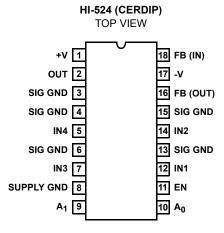

### **Pinout**

### **Features**

| • | Crosstalk (10MHz)  | -60dB |

|---|--------------------|-------|

| • | Fast Access Time   | 150ns |

| • | Fast Settling Time | 200ns |

TTL Compatible

## **Applications**

- · Wideband Switching

- Radar

- TV Video

- ECM

## Functional Diagram

### TRUTH TABLE

| A <sub>1</sub> | A <sub>0</sub> | EN | ON CHANNEL |

|----------------|----------------|----|------------|

| Х              | Х              | L  | None       |

| L              | L              | Н  | 1 (Note)   |

| L              | Н              | Н  | 2          |

| Н              | L              | Н  | 3          |

| Н              | Н              | Н  | 4          |

NOTE: Channel 1 is shown selected in the Functional Diagram.

### **Absolute Maximum Ratings** Thermal Information Thermal Resistance (Typical, Note 1) $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W) Digital Input Voltage (V<sub>EN</sub>, V<sub>A</sub>) . . . . . . . -6V to +6V CERDIP Package..... Analog Signal (V<sub>IN</sub>, V<sub>OUT</sub>) . . . . . . . . . . . . . . . . (V-) -2V to (V+) +2V Maximum Junction Temperature Maximum Storage Temperature. . . . . . . -65°C to 150°C **Operating Conditions** Maximum Lead Temperature (Soldering, 10s)............. 300°C Temperature Range ...... 0°C to 75°C HI-524-5 . . . . . . .

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications** Supplies = +15V, -15V;  $V_{AH}$  (Logic Level High) = 2.4V,  $V_{AL}$  (Logic Level Low) = 0.5V;  $V_{EN}$  = 2.4V, Unless Otherwise Specified

|                                                  | TEST<br>CONDITIONS | TEMP<br>( <sup>O</sup> C) | -5   |      |     |       |

|--------------------------------------------------|--------------------|---------------------------|------|------|-----|-------|

| PARAMETER                                        |                    |                           | MIN  | TYP  | MAX | UNITS |

| DYNAMIC CHARACTERISTICS                          |                    |                           |      |      |     |       |

| Access Time, t <sub>A</sub>                      | Note 5             | 25                        | -    | 150  | 300 | ns    |

| Break-Before-Make Delay, t <sub>OPEN</sub>       | Note 5             | 25                        | -    | 20   | -   | ns    |

| Enable Delay (ON), t <sub>ON (EN)</sub>          | $R_L = 500\Omega$  | 25                        | -    | 180  | -   | ns    |

| Enable Delay (OFF), t <sub>OFF</sub> (EN)        | $R_L = 500\Omega$  | 25                        | -    | 180  | -   | ns    |

| Settling Time (Note 5)                           | To 0.1%            | 25                        | -    | 200  | -   | ns    |

|                                                  | To 0.01%           | 25                        | -    | 600  | -   | ns    |

| Crosstalk                                        | Note 6             | 25                        | -    | -65  | -   | dB    |

| Channel Input Capacitance, C <sub>S(OFF)</sub>   |                    | 25                        | -    | 4    | -   | pF    |

| Channel Output Capacitance, C <sub>D(OFF)</sub>  |                    | 25                        | -    | 10   | -   | pF    |

| Digital Input Capacitance, CA                    |                    | 25                        | -    | 5    | -   | pF    |

| DIGITAL INPUT SPECIFICATIONS                     |                    |                           | - 11 |      | 1   |       |

| Input Low Threshold (TTL), V <sub>AL</sub>       |                    | Full                      | -    | -    | 0.8 | V     |

| Input High Threshold (TTL), V <sub>AH</sub>      |                    | Full                      | 2.4  | -    | -   | V     |

| Input Leakage Current (High), I <sub>AH</sub>    |                    | Full                      | -    | 0.05 | 1   | μА    |

| Input Leakage Current (Low), I <sub>AL</sub>     |                    | Full                      | -    | -    | 25  | μΑ    |

| ANALOG CHANNEL SPECIFICATIONS                    |                    |                           | - 11 |      | 1   |       |

| Analog Signal Range, V <sub>IN</sub>             |                    | Full                      | -10  | -    | +10 | V     |

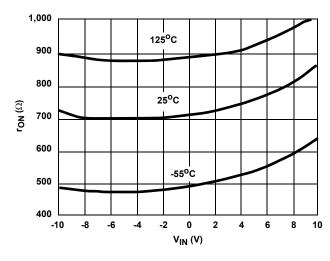

| On Resistance, r <sub>ON</sub>                   | Note 2             | 25                        | -    | 700  | -   | Ω     |

|                                                  |                    | Full                      | -    | -    | 1.5 | kΩ    |

| Off Input Leakage Current, I <sub>S (OFF)</sub>  | Note 3             | 25                        | -    | 0.2  | -   | nA    |

|                                                  |                    | Full                      | -    | -    | 50  | nA    |

| Off Output Leakage Current, I <sub>D (OFF)</sub> | Note 3             | 25                        | -    | 0.2  | -   | nA    |

|                                                  |                    | Full                      | -    | -    | 50  | nA    |

| On Channel Leakage Current, I <sub>D (ON)</sub>  | Note 3             | 25                        | -    | 0.7  | -   | nA    |

|                                                  |                    | Full                      | -    | -    | 50  | nA    |

| -3dB Bandwidth                                   | Note 4             | 25                        | -    | 8    | -   | MHz   |

# Electrical Specifications Supplies = +15V, -15V; V<sub>AH</sub> (Logic Level High) = 2.4V, V<sub>AL</sub> (Logic Level Low) = 0.5V; V<sub>EN</sub> = 2.4V, Unless Otherwise Specified (Continued)

|                                   | TEST       | TEMP | -5  |     |     |       |

|-----------------------------------|------------|------|-----|-----|-----|-------|

| PARAMETER                         | CONDITIONS | (°C) | MIN | TYP | MAX | UNITS |

| POWER SUPPLY CHARACTERISTICS      |            |      |     |     |     |       |

| Power Dissipation, P <sub>D</sub> |            | Full | -   | -   | 750 | mW    |

| Current, I+                       | Note 7     | Full | -   | -   | 25  | mA    |

| Current, I-                       | Note 7     | Full | -   | -   | 25  | mA    |

### NOTES:

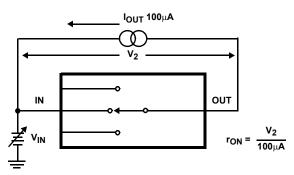

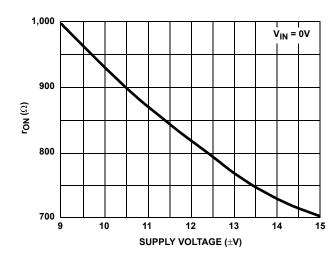

- 2.  $V_{IN}$  = 0V;  $I_{OUT}$  = 100 $\mu$ A (See Test Circuit section).

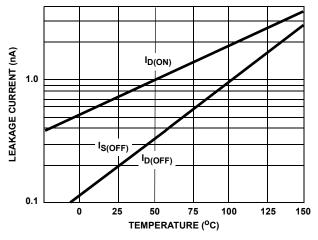

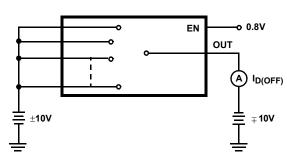

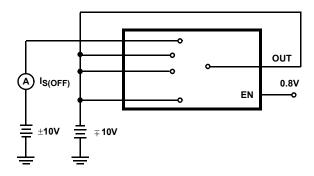

- 3.  $V_O = \pm 10V$ ;  $V_{IN} = \pm 10V$ . (See Test Circuit section).

- 4. MUX output is buffered with HA-5033 amplifier.

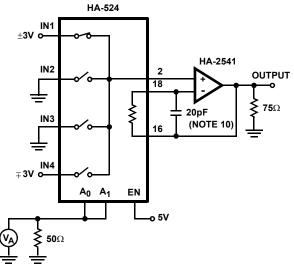

- 5. 6V Step,  $\pm 3V$  to  $\mp 3V$ , See Test Circuit section.

- 6.  $V_{IN}$  = 10MHz,  $3V_{P-P}$  on one channel, with any other channel selected. (Worst case is channel 3 selected with input on channel 4.) MUX output is buffered with HA-2541 as shown in Applications section. Terminate all channels with  $75\Omega$ .

- 7. Supply currents vary less than 0.5mA for switching rates from DC to 2MHz.

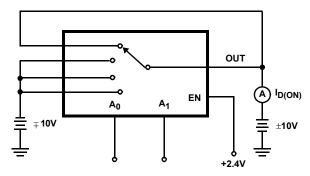

## $\textbf{\textit{Test Circuits}} \quad \textbf{\textit{and Waveforms}} \quad \textbf{\textit{T}}_{A} = 25^{o} \text{C}, \ \textbf{\textit{V}}_{SUPPLY} = \pm 15 \text{V}, \ \textbf{\textit{V}}_{AH} = 2.4 \text{V}, \ \textbf{\textit{V}}_{AL} = 0.8 \text{V}, \ \textbf{\textit{Unless Otherwise Specified Spec$

FIGURE 1A. TEST CIRCUIT

FIGURE 1B. ON RESISTANCE vs ANALOG INPUT VOLTAGE

FIGURE 1C. ON RESISTANCE vs SUPPLY VOLTAGE

Page 3 of 6

FIGURE 1. ON RESISTANCE

# $\textbf{\textit{Test Circuits}} \quad \textbf{\textit{and Waveforms}} \quad \textbf{\textit{T}}_{A} = 25^{o} \text{C}, \ \textbf{\textit{V}}_{SUPPLY} = \pm 15 \text{V}, \ \textbf{\textit{V}}_{AH} = 2.4 \text{V}, \ \textbf{\textit{V}}_{AL} = 0.8 \text{V}, \ \textbf{\textit{Unless Otherwise Specified}} \quad \textbf{\textit{(Continued)}}$

FIGURE 2A. LEAKAGE CURRENT vs TEMPERATURE

FIGURE 2B. I<sub>D(OFF)</sub> TEST CIRCUIT (NOTE 8)

FIGURE 2C. IS(OFF) TEST CIRCUIT (NOTE 8)

FIGURE 2D.  $I_{D(ON)}$  TEST CIRCUIT (NOTE 8)

**FIGURE 2. LEAKAGE CURRENTS**

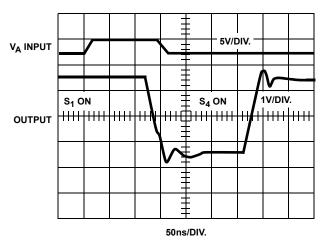

ADDRESS DRIVE (V<sub>A</sub>)

+3V

ACCESS TIME, t<sub>A</sub>

SETTLING TIME, t<sub>S</sub>

HA-2541

OUTPUT

10%

-3V

(OR ±0.1% OF FULL SCALE (OR ±0.01%)

FIGURE 3A. TEST CIRCUIT

FIGURE 3B. MEASUREMENT POINTS

FIGURE 3. SETTLING TIME, ACCESS TIME, BREAK-BEFORE-MAKE DELAY (NOTE 9)

### NOTES:

- 8. Two measurements per channel:  $\pm 10V$  and  $\mp 10V$ . (Two measurements per device for  $I_{D(OFF)} \pm 10V$  and  $\mp 10V$ .)

- 9. The Break-Before-Make test requires inputs 1 and 4 at the same voltage.

- 10. Capacitor value may be selected to optimize AC performance.

**Test Circuits and Waveforms**  $T_A = 25^{\circ}C$ ,  $V_{SUPPLY} = \pm 15V$ ,  $V_{AH} = 2.4V$ ,  $V_{AL} = 0.8V$ , Unless Otherwise Specified (Continued)

FIGURE 4. ACCESS TIME WAVEFORMS

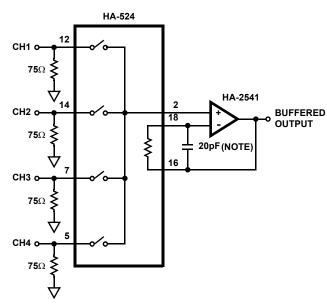

## Application Information

Often it is desirable to buffer the HI-524 output, to avoid loading errors due to the channel "ON" resistance:

NOTE: Capacitor value may be selected to optimize AC performance.

FIGURE 5.

The buffer amplifier should offer sufficient bandwidth and slew rate to avoid degradation of the anticipated signals. For video switching, the HA-5033 and HA-2542 offer good performance plus  $\pm 100$ mA output current for driving coaxial cables. For general wideband applications, the HA-2541 offers the convenience of unity gain stability plus 90ns settling (to  $\pm 0.1\%$ ) and  $\pm 10$ V output swing. Also, the HI-524 includes a feedback resistance for use with the HA-2541. This resistance matches and tracks the channel "ON" resistance, to minimize offset voltage due to the buffer's bias currents.

Note that the on-chip feedback element between pins 16 and 18 includes two switches in series, to simulate a channel resistance. These switches open for  $V_{EN}$  = Low. This allows two or more HI-524s to operate into one HA-2541, with their feedback elements connected in parallel. Thus, only the selected multiplexer provides feedback, and the amplifier remains stable.

All HI-524 pins labeled 'SIG GND' (pins 3, 4, 6, 13, 15) should be externally connected to signal ground for best crosstalk performance.

Bypass capacitors  $(0.1\mu F)$  to  $1\mu F$ ) are recommended from each HI-524 supply pin to power ground (pins 1 and 17 to pin 8). Locate the buffer amplifier near the HI-524 so the two capacitors may bypass both devices.

If an analog input 1V or greater is present when supplies are off, a low resistance is seen from that input to a supply line. (For example, the resistance is approximately  $160\Omega$  for an input of -3V.) Current flow may be blocked by a diode in each supply line, or limited by a resistor in series with each channel. The best solution, of course, is to arrange that no digital or analog inputs are present when the power supplies are off.

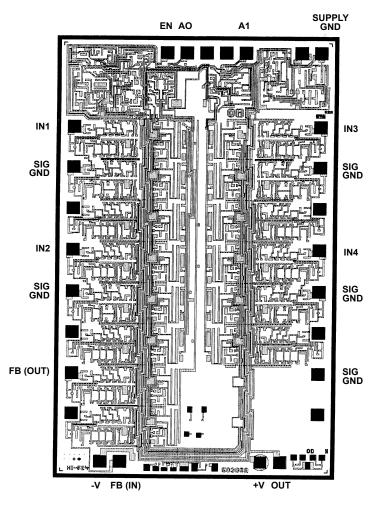

### Die Characteristics

**DIE DIMENSIONS:**

2250µm x 3720µm x 485µm

**METALLIZATION:**

Type: CuAl

Thickness: 16kÅ ±2kÅ

### **PASSIVATION:**

Type: Nitride Over Silox Nitride Thickness: 3.5kÅ ±1kÅ Silox Thickness: 12kÅ ±2kÅ

### **WORST CASE CURRENT DENSITY:**

$1.58 \times 10^5 \text{ A/cm}^2$

## Metallization Mask Layout

HI-524

© Copyright Intersil Americas LLC 2002. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>