Product

Brief

Optically S First

C Bus Repeaters

**CPC5902**

Optically Coupled I<sup>2</sup>C Bus Repeater Providing 3750V<sub>rms</sub> Input-to-Output Galvanic Isolation

#### Features:

- Low EM and RF Generation No Internal Clock

- Bidirectionally Buffers Both I<sup>2</sup>C Signals

- Extends and Isolates I<sup>2</sup>C Interfaces

- Supports Standard and Fast-mode I<sup>2</sup>C (400kbps)

- Supports Direct Static-State Buffering Without Refresh

- Operates on 2.7V to 5.5V

- Glitch-Free Operation

- Translates Voltage Levels

## **Robust:**

- Immune to External EMI and RFI

- High Voltage Isolation Tested Above 6kV<sub>pk</sub> for Adverse Environments

# **Example Applications:**

- Power Over Ethernet

- I<sup>2</sup>C Bus Length Extender

- Isolated Signal Monitoring and Control

- Power Supply High-Side Interface

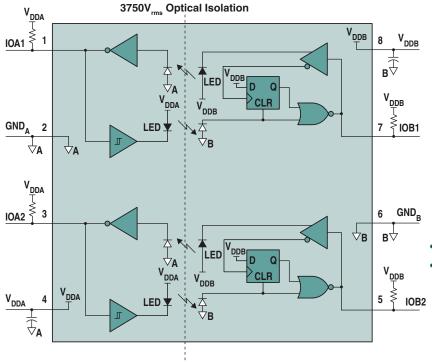

## **CPC5902 Functional Block Diagram**

- UL 1577 Certified Component: File E76270

- EN/IEC 60950 Certified Component: TUV Certificate: B 11 10 49410 007

Download IXYS Integrated Circuits Division's Technical Brief, TB-101 "Optically Isolating an I<sup>2</sup>C Interface:

http://www.ixysic.com/home/pdfs.nsf/www/TB-101.pdf/\$file/TB-101.pdf

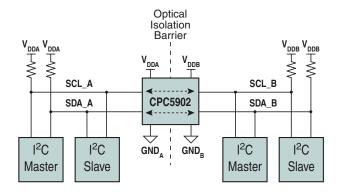

## CPC5902 Optically Coupled Bus Repeater: I<sup>2</sup>C Bus Application

- Replaces Multiple Logic Optoisolators

- 3750V<sub>rms</sub> Galvanic Isolation

- Multiple Masters and Slaves on Same Bus

- I<sup>2</sup>C Fast-mode Operation up to 400kbps

- Bidirectionally Buffers Two I<sup>2</sup>C Signals

- Supports I<sup>2</sup>C Clock Stretching

- Internal Glitch Suppression Circuitry

- Supports Bus Level Translation: 2.7V to 5.5V

- Passes DC Signals No Refresh Needed

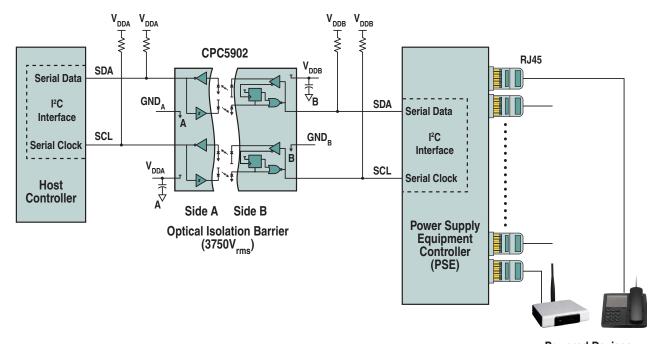

## **CPC5902 Optically Coupled Bus Repeater: Power-over-Ethernet (PoE) Application**

- Provides Communications Interface Between Host Controller and PSE Controller

- Provides 3750V<sub>ms</sub> Galvanic Isolation Between Host Controller and PSE Controller

- Protects Host Controller During Power Supply Surge Tests

- · Bidirectionally Buffers Clock and Data Signals Between Host Controller and PSE Controller

- Simplifies Bus Design by Replacing Multiple Logic Optoisolators

- Provides any Necessary Bus Level Translation Between Host Controller and PSE Controller

Powered Devices

For more information about IXYS Integrated Circuits Division's CPC5902, please visit:

http://www.ixysic.com/Products/OptBusRepBiDi.htm

For additional information, contact your IXYS IC Division Representative: http://www.ixysic.com/home/pages.nsf/locate.rep

Or visit IXYS IC Division's web site: http://www.ixysic.com