# iW-RainboW-G24M Arria10 SoC/FPGA SOM Hardware User Guide

#### **Document Revision History**

| Document Number |                           | iW-PRFAZ-UM-01-R3.0-REL0.2-Hardware |  |

|-----------------|---------------------------|-------------------------------------|--|

| Revision Date   |                           | Description                         |  |

| 0.1             | 01 <sup>st</sup> Oct 2019 | Draft Release Version               |  |

| 0.2             | 02 <sup>nd</sup> Mar 2020 | Updated Release Version             |  |

PROPRIETARY NOTICE: This document contains proprietary material for the sole use of the intended recipient(s). Do not read this document if you are not the intended recipient. Any review, use, distribution or disclosure by others is strictly prohibited. If you are not the intended recipient (or authorized to receive for the recipient), you are hereby notified that any disclosure, copying distribution or use of any of the information contained within this document is STRICTLY PROHIBITED. Thank you. "iWave Systems Tech. Pvt. Ltd."

#### Disclaimer

iWave Systems reserves the right to change details in this publication including but not limited to any Product specification without notice.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by iWave Systems, its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CPU and other major components used in this product may have several silicon errata associated with it. Under no circumstances, iWave Systems shall be liable for the silicon errata and associated issues.

#### **Trademarks**

All registered trademarks, product names mentioned in this publication are the property of their respective owners and used for identification purposes only.

#### Certification

iWave Systems Technologies Pvt. Ltd. is an ISO 9001:2015 Certified Company.

#### Warranty & RMA

Warranty support for Hardware: 1 Year from iWave or iWave's EMS partner.

For warranty terms, go through the below web link,

http://www.iwavesystems.com/support/warranty.html

For Return Merchandise Authorization (RMA), go through the below web link,

http://www.iwavesystems.com/support/rma.html

#### **Technical Support**

iWave Systems technical support team is committed to provide the best possible support for our customers so that our Hardware and Software can be easily migrated and used.

For assistance, contact our Technical Support team at,

Email : support.ip@iwavesystems.com

Website : <u>www.iwavesystems.com</u>

Address : iWave Systems Technologies Pvt. Ltd.

# 7/B, 29<sup>th</sup> Main, BTM Layout 2<sup>nd</sup> Stage,

Bangalore, Karnataka,

India - 560076

## **Table of Contents**

| 1. | INTR  | RODUCTION                                                     | 7  |

|----|-------|---------------------------------------------------------------|----|

|    | 1.1   | Purpose                                                       | 7  |

|    | 1.2   | Overview                                                      |    |

|    | 1.3   | List of Acronyms                                              | 7  |

|    | 1.4   | Terminlogy Description                                        | 8  |

|    | 1.5   | References                                                    | 8  |

| 2. | ARCI  | HITECTURE AND DESIGN                                          | 9  |

|    | 2.1   | Arria10 SoC/FPGA SOM Block Diagram                            | q  |

|    |       | Arria10 SoC/FPGA SOM Features                                 |    |

|    |       | Arria10 SoC/FPGA                                              |    |

|    |       | 1 Arria10 SoC/FPGA Power                                      |    |

|    | 2.3.2 |                                                               |    |

|    | 2.3.3 |                                                               |    |

|    | 2.3.4 |                                                               |    |

|    | 2.3.5 | ·                                                             |    |

|    |       | PMIC                                                          |    |

|    |       | Memory                                                        |    |

|    | 2.5.1 | ·                                                             |    |

|    | 2.5.2 |                                                               |    |

|    | 2.5.3 | 3 MicroSD Connector for HPS booting                           | 18 |

|    | 2.5.4 | 4 eMMC Flash for HPS booting (Optional)                       | 19 |

|    | 2.5.5 |                                                               |    |

|    | 2.6   | On-SOM Features                                               | 20 |

|    | 2.6.1 | 1 JTAG Header                                                 | 20 |

|    | 2.6.2 | 2 Fan Header                                                  | 22 |

|    | 2.6.3 | 3 FPGA AS Header                                              | 23 |

|    | 2.7   | Board to Board Connector1 Interfaces                          | 25 |

|    | 2.7.1 | 1 FPGA High Speed Transceivers                                | 29 |

|    | 2.7.2 | 2 FPGA IOs & General Purpose Clocks – Bank2A                  | 33 |

|    | 2.7.3 | 3 FPGA IOs & General Purpose Clocks – Bank3A                  | 36 |

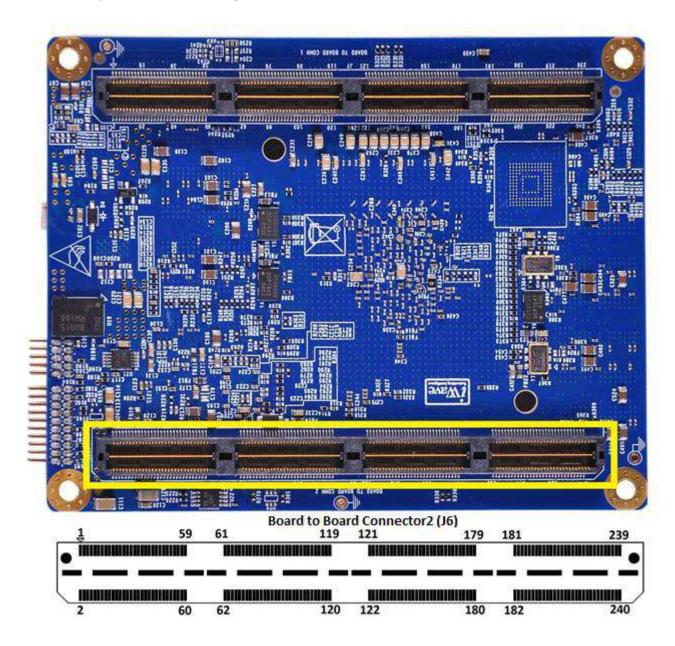

|    | 2.8   | Board to Board connector2 Interfaces                          | 41 |

|    | 2.8.1 | 1 HPS Interfaces                                              | 45 |

|    | 2.8.2 | 2 FPGA Interfaces                                             | 51 |

|    | 2.9   | Arria10 SoC HPS Pin Multiplexing on Board to Board Connector2 | 62 |

| 3. | TECH  | HNICAL SPECIFICATION                                          | 65 |

|    | 3.1   | Electrical Characteristics                                    | 65 |

|    | 3.1.1 | 1 Power Input Requirement                                     | 65 |

|    | 3.1.2 | 2 Power Input Sequencing                                      | 66 |

|    | 3.1.3 | Power Consumption                                             | 67 |

|    | 3.2   | Environmental Characteristics                                 | 68 |

|    |       |                                                               |    |

|    | 3.2.1 | Environmental Specification                                      | 68 |

|----|-------|------------------------------------------------------------------|----|

|    | 3.2.1 | RoHS2 Compliance                                                 | 68 |

|    | 3.2.2 | Electrostatic Discharge                                          | 68 |

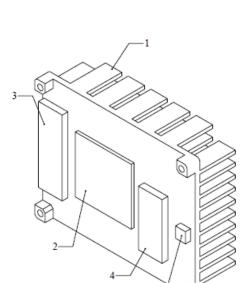

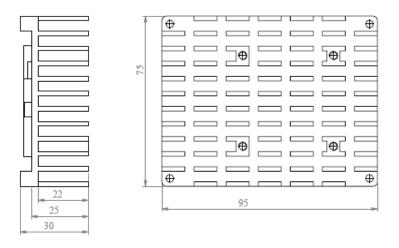

|    | 3.2.3 | Heat Sink                                                        | 68 |

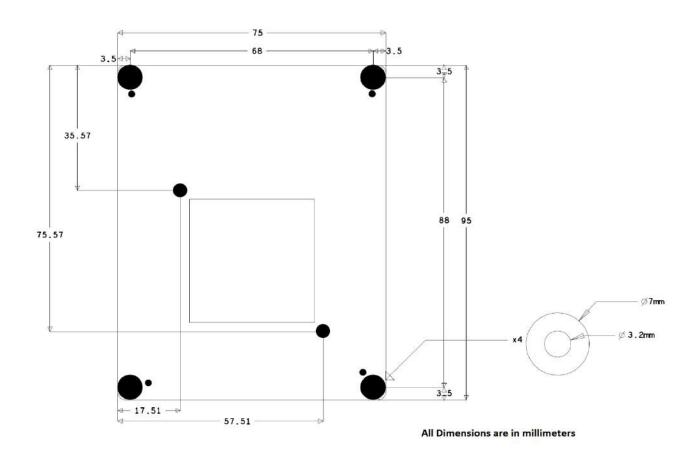

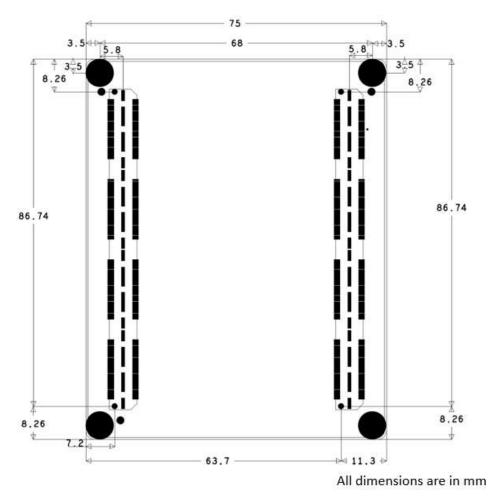

| 3  | .3 N  | 1echanical Characteristics                                       | 70 |

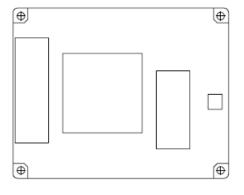

|    | 3.3.1 | Arria10 SoC/FPGA SOM Mechanical Dimensions                       | 70 |

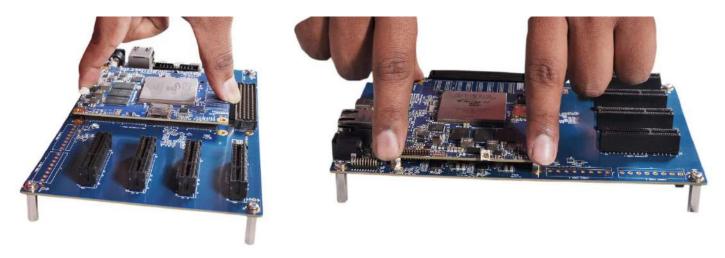

|    | 3.3.2 | Guidelines to insert the Arria10 SoC/FPGA SOM into Carrier board | 72 |

| 4. | ORDEF | RING INFORMATION                                                 | 73 |

| 5. | APPEN | IDIX I                                                           | 74 |

| 5  | .1 A  | rria10 SoC/FPGA SOM Development Platform                         | 74 |

# **List of Figures**

| Figure 1: Arria10 SoC/FPGA SOM Block Diagram                         | 9  |  |  |

|----------------------------------------------------------------------|----|--|--|

| Figure 2: Arria10 SoC Simplified Block Diagram                       | 12 |  |  |

| Figure 3 Arria10 Family Device Comparison                            | 13 |  |  |

| Figure 4: Micro SD Connector                                         | 19 |  |  |

| Figure 5: JTAG Header                                                | 20 |  |  |

| Figure 6: Fan Header                                                 | 22 |  |  |

| Figure 7: FPGA AS Header                                             | 23 |  |  |

| Figure 8: Board to Board Connector1                                  | 25 |  |  |

| Figure 9: Board to Board Connector2                                  | 41 |  |  |

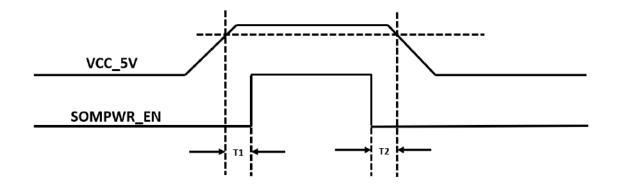

| Figure 11: Power Input Sequencing                                    | 66 |  |  |

| Figure 10: Heat Sink Dimensions                                      | 69 |  |  |

| Figure 12: Mechanical dimension of Arria10 SoC/FPGA SOM- Top View    | 70 |  |  |

| Figure 13: Mechanical dimension of Arria10 SoC/FPGA SOM- Bottom View | 71 |  |  |

| Figure 14: Mechanical dimension of Arria10 SoC/FPGA SOM- Side View   | 71 |  |  |

| Figure 15: Arria10 SoC/FPGA SOM Insertion procedure                  | 72 |  |  |

| Figure 16: Arria10 SoC/FPGA SOM Development Platform                 | 74 |  |  |

|                                                                      |    |  |  |

| List of Tables                                                       |    |  |  |

| Table 1: Acronyms & Abbreviations                                    | 7  |  |  |

| Table 2: Terminology                                                 | 8  |  |  |

| Table 3: Arria10 SoC/FPGA SOM Reference Clocks                       |    |  |  |

| Table 4: Configuration Selection Switch Truth Table                  | 16 |  |  |

| Table 5: Arria10 SoC/FPGA Transceiver data rate performance          | 17 |  |  |

| Table 6: JTAG Header Pin Assignment                                  | 21 |  |  |

| Table 7: FAN Header Pin Assignment                                   | 22 |  |  |

| Table 8: FPGA AS Header Pin Assignment                               | 23 |  |  |

| Table 9 Board to Board Connector1 Pinout                             | 26 |  |  |

| Table 10: Board to Board Connector2 Pinout                           | 42 |  |  |

| Table 11: Arria10 SoC HPS IOMUX on Board to Board Connector2         | 62 |  |  |

| Table 12: Power Input Requirement                                    | 65 |  |  |

| Table 13: Power Sequence Timing                                      | 66 |  |  |

| Table 14: Power Consumption                                          | 67 |  |  |

| Table 15: Environmental Specification                                | 68 |  |  |

| Table 16: Orderable Product Part Numbers                             |    |  |  |

#### 1. INTRODUCTION

#### 1.1 Purpose

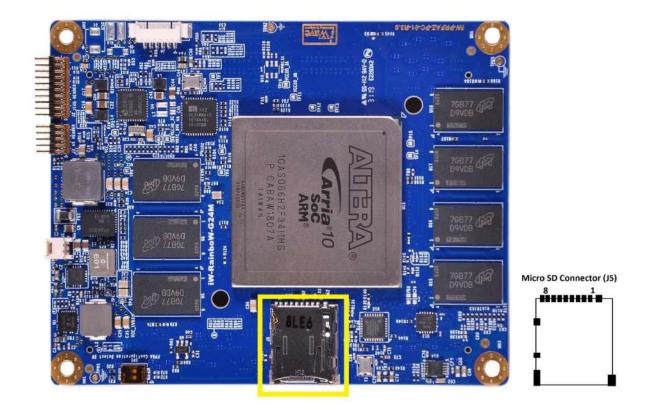

This document is the Hardware User Guide for the Arria10 SoC/FPGA System On Module based on the Intel's Arria10 SoC or FPGA. This board is fully supported by iWave Systems Technologies Pvt. Ltd. This Guide provides detailed information on the overall design and usage of the Arria10 SoC/FPGA SOM from a Hardware Systems perspective.

#### 1.2 Overview

The Arria10 SoC/FPGA SOM is an extension of Arria10 SoC/FPGA. The Arria10 SoC/FPGA SOM has a form factor of 95mm x 75mm and provides the functional requirements for an embedded application. Two 240pin high speed ruggedized terminal strip connectors provide the carrier board interface to carry all the I/O signals to and from the Arria10 SoC/FPGA SOM.

#### 1.3 List of Acronyms

The following acronyms is used throughout this document.

Table 1: Acronyms & Abbreviations

| Acronyms   | Abbreviations                                                               |  |  |

|------------|-----------------------------------------------------------------------------|--|--|

| ARM        | Advanced RISC Machine                                                       |  |  |

| AS         | Active serial                                                               |  |  |

| CPU        | Central Processing Unit                                                     |  |  |

| DDR4 SDRAM | Double Data Rate fourth-generation Synchronous Dynamic Random Access Memory |  |  |

| DMA        | Direct Memory Access                                                        |  |  |

| FPGA       | Field Programmable Gate Array                                               |  |  |

| FPP        | Fast Passive Parallel                                                       |  |  |

| GB         | Giga Byte                                                                   |  |  |

| Gbps       | Gigabits per sec                                                            |  |  |

| GHz        | Giga Hertz                                                                  |  |  |

| GPIO       | General Purpose Input Output                                                |  |  |

| HPS        | Hard Processor System                                                       |  |  |

| I2C        | Inter-Integrated Circuit                                                    |  |  |

| JTAG       | Joint Test Action Group                                                     |  |  |

| Kbps       | Kilobits per second                                                         |  |  |

| MAC        | Media Access Controller                                                     |  |  |

| MB         | Mega Byte                                                                   |  |  |

| Mbps       | Megabits per sec                                                            |  |  |

| MHz        | Mega Hertz                                                                  |  |  |

| PCB        | Printed Circuit Board                                                       |  |  |

| PMIC       | Power Management Integrated IC                                              |  |  |

| Acronyms | Abbreviations                               |  |

|----------|---------------------------------------------|--|

| PS       | Passive Serial                              |  |

| ROHS     | Restriction of Hazardous Substances         |  |

| SPI      | Serial Peripheral Interface                 |  |

| SD       | Secure Digital                              |  |

| SoC      | System On Chip                              |  |

| SOM      | System On Module                            |  |

| UART     | Universal Asynchronous Receiver/Transmitter |  |

| USB      | Universal Serial Bus                        |  |

| USB OTG  | USB On The Go                               |  |

#### 1.4 Terminlogy Description

In this document, wherever Signal Type is mentioned, below terminology is used.

**Table 2: Terminology**

| Terminology | Description                                                |  |

|-------------|------------------------------------------------------------|--|

| T           | Input Signal                                               |  |

| 0           | Output Signal                                              |  |

| 10          | Bidirectional Input/output Signal                          |  |

| CMOS        | Complementary Metal Oxide Semiconductor Signal             |  |

| DIFF        | Differential Signal                                        |  |

| LVCMOS      | Low Voltage Complementary Metal Oxide Semiconductor Signal |  |

| LVDS        | Low Voltage Differential Signal                            |  |

| OD          | Open Drain Signal                                          |  |

| OC          | Open Collector Signal                                      |  |

| Power       | Power Pin                                                  |  |

| PU          | Pull Up                                                    |  |

| PD          | Pull Down                                                  |  |

| NA          | Not Applicable                                             |  |

| NC          | Not Connected                                              |  |

Note: Signal Type does not include internal pull-ups or pull-downs implemented by the chip vendors and only includes the pull-ups or pull-downs implemented On-SOM.

#### 1.5 References

- Arria10 Device Handbook

- Arria10 Device Overview

#### 2. ARCHITECTURE AND DESIGN

This section provides detailed information about the Arria10 SoC/FPGA SOM features and Hardware architecture with high level block diagram. Also this section provides detailed information about two Board to Board connector's pin assignment and usage.

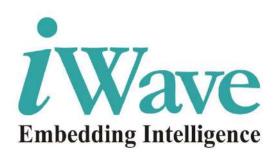

#### 2.1 Arria10 SoC/FPGA SOM Block Diagram

Figure 1: Arria10 SoC/FPGA SOM Block Diagram

#### 2.2 Arria10 SoC/FPGA SOM Features

The Arria10 SoC/FPGA SOM supports the following features.

#### SoC/FPGA

- Intel's Arria10 SoC/FPGA

- Compatible Arria10 SoC Family SX270, SX320, SX480, SX570, SX660

With upto 660K Logic Elements, 24 High Speed Transceivers and integrated Dual Core ARM

Cortex –A9 @ upto 1.5 GHz/Core Hard Processor System (HPS).

- Compatible Arria10 FPGA Family GX270, GX320, GX480, GX570, GX660, GX900, GX1150

With upto 1150K Logic Elements and 24 High Speed transceivers

- FPGA Configuration Selection Switch

#### Memory

- 2GB DDR4 SDRAM (32bit) with ECC for HPS (Expandable) 1,2

- 4GB DDR4 RAM (64bit) from FPGA <sup>3</sup>

- MicroSD Connector for HPS booting <sup>1, 4</sup>

- eMMC Flash for HPS booting (Optional) 1,4

- Configuration Flash for FPGA

#### **Other On-SOM Features**

- JTAG Header

- FAN Header

- FPGA AS Header

#### **Board to Board Connector1 Interfaces**

- FPGA High Speed Transceivers (upto 17.4Gbps) x 16

- FPGA IOs & General Purpose Clocks Bank2A

- Upto 21 LVDS/46SE IOs

- One General Purpose Clock Input LVDS Pair/Single Ended

- Two General Purpose Clock Output LVDS Pairs/Single Ended

- FPGA IOs & General Purpose Clocks Bank3A

- Upto 22 LVDS/47SE IOs

- > Two General Purpose Clock Input LVDS Pairs/Single Ended

- Two General Purpose Clock Output LVDS Pairs/Single Ended

#### **Board to Board Connector2 Interfaces**

#### From HPS Block: 1,5

- Gigabit Ethernet x 1 Port (through On-SOM Gigabit Ethernet PHY)

- USB OTG x 1 Port (through On-SOM USB ULPI PHY)

- HPS Dedicated Debug UART (UART1) x 1 Port

- SPI x 1 Port

- I2C x 1 Port

- HPS GPIOs

- HPS Warm Reset

#### From FPGA Block:

- FPGA High Speed Transceivers (upto 17.4Gbps) x 8

- FPGA IOs & General Purpose Clocks Bank3B

- Upto 24 LVDS IOs

- > Two General Purpose Clock Input LVDS Pairs/Single Ended

- Two General Purpose Clock Output LVDS Pairs/Single Ended

- FPGA IOs & General Purpose Clocks Bank3C

- Upto 24 LVDS IOs

- Two General Purpose Clock Input LVDS Pairs/Single Ended

- Two General Purpose Clock Output LVDS Pairs/Single Ended

- JTAG Interface

#### **General Specification**

- Power Supply : 5V

- Form Factor : 95mm x 75mm

- <sup>1</sup> In Arria10 SoC/FPGA SOM, these interfaces can be supported only if Arria10 "SoC" family devices are used which supports Hard Processor System (HPS).

- <sup>2</sup> In Arria10 SoC/FPGA SOM, if Arria10 SoC family device is not used and FPGA family device is used, then also 32bit DDR4 can be supported from FPGA fabric.

- <sup>3</sup> This FPGA DDR4 interface is not supported in lower device configurations of Arria10 SoC/FPGA devices (SX270, GX270, SX320 and GX320) based SOM.

- <sup>4</sup> In Arria10 SoC/FPGA SOM, these interfaces can be supported only if Arria10 "SoC" family devices are used because these interfaces are supported through Dedicated I/O pins of Hard Processor System (HPS).

- <sup>5</sup> In Arria10 SoC/FPGA SOM, if Arria10 "SoC" family device is not used and "FPGA" only family device is used, then these Shared I/O interfaces cannot be used. But the same pins can be used as FPGA Bank2L from FPGA fabric.

#### 2.3 Arria10 SoC/FPGA

The Arria10 SoC/FPGA SOM is based on Intel's Arria10 family devices with F34 package (1,152 pins, 35 mm x 35 mm). Intel's Arria10 family devices comes with FPGA alone devices and FPGA + HPS supported devices (which is called as SoC). The Arria10 SoC/FPGA comes with three different FPGA fabric speed grade supported devices and different power options. Also its high speed transceivers comes with four different speed grade supported devices.

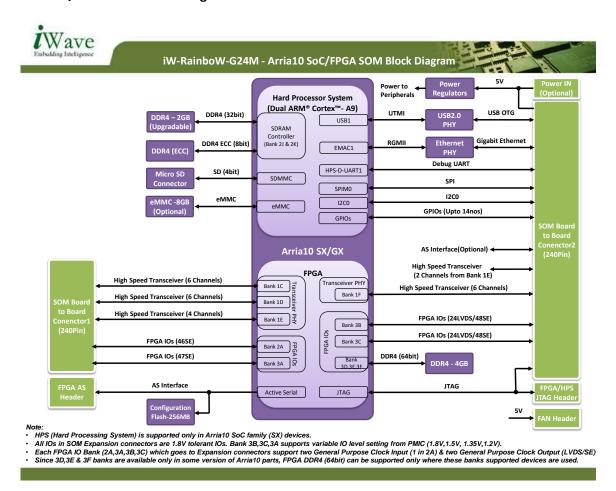

The Arria10 SoC devices supports Dual Core ARM Cortex-A9 core up to 1.5 GHz speed/core. The Dual ARM Cortex-A9 core with FPGA fabric allows greater flexibility for the system designers and helps lower the system cost and power consumption. This improved logic integration with a rich feature set of embedded peripherals, hardened floating point variable precision DSP blocks, embedded high speed transceivers, hard memory controllers and protocol intellectual property controllers which is ideal for cost-sensitive high end applications. The Block Diagram of Arria10 SoC from the datasheet is shown below for reference.

Figure 2: Arria10 SoC Simplified Block Diagram

Note: Please refer the latest Arria10 SoC/FPGA datasheet from Intel website for Electrical & Switching characteristics which may be revised from time to time.

The Arria10 SoC/FPGA SOM is compatible to SX270 SX480, and SX660 devices and feature comparison between these devices are shown below.

| PRODUCT LINE                                        |                                                                                            | SX270                              | SX480          | SX660          |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|

|                                                     | LEs (K)                                                                                    | 270                                | 480            | 660            |

|                                                     | System logic elements (K)                                                                  | 354                                | 629            | 865            |

|                                                     | Adaptive logic modules (ALMs)                                                              | 101,620                            | 181,790        | 250,540        |

|                                                     | Registers                                                                                  | 406,480                            | 727,160        | 1,002,160      |

| S                                                   | M20K memory blocks                                                                         | 750                                | 1,438          | 2,133          |

| uro                                                 | M20K memory (Mb)                                                                           | 15                                 | 28             | 42             |

| Resources                                           | MLAB memory (Mb)                                                                           | 2.4                                | 4.3            | 5.7            |

| R                                                   | Hardened single-precision floating-point multiplers/adders                                 | 830/830                            | 1,368/1,368    | 1,688/1,688    |

|                                                     | 18 x 19 multipliers                                                                        | 1,660                              | 2,736          | 3,376          |

|                                                     | Peak fixed-point performance (GMACS) <sup>1</sup> Peak floating-point performance (GFLOPS) | 1,826<br>747                       | 3,010<br>1,231 | 3,714<br>1,519 |

| pc                                                  | Global clock networks                                                                      | 32                                 | 32             | 32             |

| S, al                                               | Regional clocks                                                                            | 8                                  | 8              | 16             |

| I/O Pins, and<br>Features                           | Hard processor system<br>(available in SX devices only)                                    | Dual-core Arm Cortex-A9 MPCore pro |                | ore processo   |

| al F                                                | Maximum LVDS channels (1.6 G)                                                              | 168                                | 222            | 270            |

| Clocks, Maximum I/O Pins,<br>Architectural Features | Maximum user I/O pins                                                                      | 384                                | 492            | 696            |

|                                                     | Transceiver count (17.4 Gbps)                                                              | 24                                 | 36             | 48             |

|                                                     | Transceiver count (25.78 Gbps)                                                             | -                                  | -              | -              |

|                                                     | PCIe* hardened IP blocks (Gen3 x8)2                                                        | 2                                  | 2              | 2              |

| ŏ                                                   | Maximum 3 V I/O pins                                                                       | 48                                 | 48             | 96             |

Figure 3 Arria10 Family Device Comparison

#### 2.3.1 Arria10 SoC/FPGA Power

The Arria10 SoC/FPGA SOM uses discrete power regulators along with DA9062 PMIC from Dialog Semiconductor for MPSoC power management. In Arria10 SoC/FPGA SOM, Core voltage & Periphery circuitry power supply of Arrai10 HPS & FPGA (VCC, VCCP, VCCERAM & VCCL\_HPS) is fixed to 0.95V. The HPS I/O voltage (VCCIO\_HPS) is fixed to 1.8V. The I/O voltage details of each FPGA Bank & High speed transceiver is mentioned in the corresponding section.

The I/O voltage of Bank3B,3C & 3A which are connected to Board to Board Connectors are generated from PMIC LDO2, LOD3, LDO4 and by default set to 1.8V. I/O voltage is configurable through software after bootup.

#### 2.3.2 Arria10 SoC/FPGA Reset

The Arria10 SoC/FPGA SOM uses PMIC's Reset output (nRESET) for HPS block POR for power on reset and the same POR is connected to FPGA Bank3A AN7 pin for FPGA fabric usage if needed. And this same signal is optionally connected to BANK2A AE17 through resistor and default not populated. By default, standard POR delay is supported in Arria10 SoC/FPGA SOM. Also it supports warm reset input from Board to Board Connector2 pin35 and connected to HPS nRST pin of Arria10 SoC/FPGA.

#### 2.3.3 Arria10 SoC/FPGA Reference Clocks

The Arria10 SoC/FPGA SOM supports on board clock oscillators for reference clock input to different blocks of Arria10 SoC/FPGA. These reference clock details are mentioned in the below table.

Table 3: Arria10 SoC/FPGA SOM Reference Clocks

| SI | On-SOM Oscillator | Arrai10 Ball Name/ | Signal Type/ | Description                                  |

|----|-------------------|--------------------|--------------|----------------------------------------------|

| No | Frequency         | Pin Number         | Termination  | Description                                  |

| 1  | 25MHz             | HPS_CLK1/          | 1.8V, LVCMOS | 25Mhz single ended reference clock for HPS.  |

|    |                   | B16                |              |                                              |

| 2  | 200Mhz/           | CLK_2K_1p/E23 &    | 1.8V, LVDS   | LVDS reference clock for HPS DDR4.           |

|    | 267MHz/           | CLK_2K_1n/E24      |              | -3 Speed Grade for 200 Mhz.                  |

|    | 300MHz            |                    |              | -2 Speed Grade for 267 Mhz.                  |

|    |                   |                    |              | -1 Speed Grade for 300 Mhz.                  |

| 3  | 50MHz             | CLK_2A_1p/         | 1.8V, LVCMOS | 50Mhz single ended reference clock for FPGA. |

|    |                   | AM15               |              | This is connected to Bank2A General Purpose  |

|    |                   |                    |              | Clock Input pin.                             |

| 4  | 100MHz            | CLKUSR/            | 1.8V, LVCMOS | 100Mhz single ended reference clock for FPGA |

|    |                   | AK16               |              | High Speed Transceiver. This is connected to |

|    |                   |                    |              | Bank2A CLKUSR pin.                           |

| 5  | 200Mhz/           | CLK_3E_1p/F6 &     | 1.8V, LVDS   | LVDS reference clock for FPGA DDR4. This is  |

|    | 267MHz/           | CLK_3E_1n/F5       |              | connected to Bank3E General Purpose Clock    |

|    | 300MHz            |                    |              | Input pin.                                   |

|    |                   |                    |              | -3 Speed Grade for 200 Mhz.                  |

|    |                   |                    |              | -2 Speed Grade for 267 Mhz.                  |

|    |                   |                    |              | -1 Speed Grade for 300 Mhz.                  |

#### 2.3.4 Arria10 SoC/FPGA Configuration Scheme

The Arria10 SoC/FPGA supports different configuration schemes JTAG-based configuration, AS Fast or Standard POR configuration and PS/FPP Fast or Standard POR configuration. These configuration schemes are selected using the MSEL pin setting.

The Arria10 SoC/FPGA SOM supports FPGA Configuration Selection Switch (SW1) to set the required FPGA configuration scheme. This Configuration Selection Switch features are shown below.

**Table 4: Configuration Selection Switch Truth Table**

| Arria10 SoC/FPGA                                   |               | SW1 (2 Position Switch) |                 |                                                             |

|----------------------------------------------------|---------------|-------------------------|-----------------|-------------------------------------------------------------|

| Configuration Scheme                               | POR Delay     | POS1<br>(MSEL0)         | POS2<br>(MSEL1) | Image                                                       |

| AS (x1 and x4)                                     | Fast          | OFF                     | ON              | ON CTS                                                      |

| AS (x1 and x4)                                     | Standard      | ON                      | ON              | ON CTS  612  2  A  A  A  A  A  A  A  A  A  A  A  A          |

| PS and<br>FPP (x8, x16, and x32)                   | Fast          | OFF                     | OFF             | ON CTS  6 N  2  A  A  B  C  C  C  C  C  C  C  C  C  C  C  C |

| PS and FPP<br>(Configuration Via HPS)<br>(Default) | Standard      | ON                      | OFF             | ON CTS  612  Q  Q  Q  Q  Q                                  |

| JTAG-based configuration                           | -             | -                       | -               | Use any of the above valid MSEL pin settings                |

| OFF – Low (C                                       | ON – High (1) |                         |                 |                                                             |

Note: MSEL2 pin is fixed to 0 (Low) in the Arria10 SoC/FPGA SOM hardware.

#### 2.3.5 Arria10 SoC/FPGA High Speed Transceivers

The Arria10 SoC/FPGA SOM supports 24 high speed transceivers on Board to Board connectors from Arria10 FPGA fabric. The Arria10 SoC/FPGA has four high speed transceiver banks (1C, 1D, 1E & 1F) and each transceiver bank has six high speed transmit and receive channels. Also, each high-speed transceiver bank supports two reference clock input pairs. Transceiver data rate performance is based on the transceiver speed grade of the Arria10 SoC/FPGA as mentioned in the below table.

Table 5: Arria10 SoC/FPGA Transceiver data rate performance

| Description  | Transceiver<br>Speed Grade 1<br>(Gbps) | Transceiver<br>Speed Grade 2<br>(Gbps) | Transceiver<br>Speed Grade 3<br>(Gbps) | Transceiver<br>Speed Grade 4<br>(Gbps) |

|--------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| Chip-to-Chip | 17.4                                   | 15                                     | 14.2                                   | 12.5                                   |

| Backplane    | 12.5                                   | 12.5                                   | 12.5                                   | 10.3125                                |

The Arria10 SoC/FPGA SOM supports 16 high speed transceiver channels (6 from Bank1C, 6 from Bank1D & 4 from Bank1E) along with two reference clock input pairs of each bank (Bank1C, Bank1D & Bank1E) on Board to Board connector1 and 8 high speed transceiver channels (2 from Bank1E & 6 from Bank1F) along with two reference clock input pairs of Bank1F on Board to Board conenctor2. In Arria10 SoC/FPGA SOM, on board termination and AC coupling capacitor are not supported on transceiver lines. So it has to be taken care in the carrier board if required.

In Arria10 SoC/FPGA SOM, Transceiver power to Arria10 SoC/FPGA is fixed to 1.03V. Also it supports 100MHz Oscillator on board for transceiver reference clock and connected to Bank2A AK16 CLKUSR pin. This CLKUSR pin can be used for configuration and transceiver calibration simultaneously. For transceiver calibration, CLKUSR must be a free-running clock running between 100 MHz to 125 MHz at power-up for PS/FPP configuration scheme. Transceiver calibration starts utilizing the CLKUSR during device configuration and may continue to use it even when the device enters user mode.

#### **2.4 PMIC**

The Arria10 SoC/FPGA SOM supports Dialog semiconductor DA9062 PMIC. The I2C0 module of Arria10 SoC/FPGA SoC HPS is used for PMIC interface through I2C address 0x58.

PMIC's LDO2, LDO3, LDO4 output regulators are connected to I/O voltage of concern Banks (Bank 3B for LDO2, Bank3C for LDO3 & Bank3A for LDO4) and by default set to 1.8V. The I/O voltages are configurable through software after bootup.

#### 2.5 Memory

#### 2.5.1 DDR4 SDRAM with ECC for HPS/FPGA

The Arria10 SoC SOM supports 32bit, 2GB DDR4 SDRAM from HPS. Two 16bit, 1GB DDR4 SDRAM ICs are used to support a total on board RAM memory of 2GB for HPS. Also Arria10 SoC SOM supports 8bit ECC for RAM memory. In Arria10 SoC SOM, Bank2J & Bank2K is used for HPS DDR4 interface. DDR4 devices operates at 1.2V voltage level and so I/O voltage for Bank2J & Bank2K is fixed to 1.2V. The Arria10 SoC SOM supports LVDS Oscillator on board for HPS DDR4 reference clock. DDR4-SDRAM ICs are physically located on top side of the SOM. In Arria10 FPGA only SOM (where HPS is not available), DDR4 can still be used from FPGA fabric through Bank2J & Bank2K.

Note: The RAM size can be expandable in Arria10 SoC/FPGA SOM and contact iWave for more details.

#### 2.5.2 DDR4 SDRAM for FPGA

The Arria10 SoC/FPGA SOM supports 64bit DDR4 SDRAM through FPGA fabric. Four 16bit DDR4 SDRAM ICs are used to support RAM memory. These DDR4-SDRAM ICs are physically located on top side of the SOM. The Arria10 SoC/FPGA SOM supports LVDS Oscillator on board for FPGA DDR4 reference clock and connected to Bank3E F5 & F6 dedicated clock input pins.

These DDR4 ICs are connected to FPGA Banks 3D, 3E & 3F of Arria10 SoC/FPGA and hence are only supported in higher device configurations of Arria10 SoC/FPGA devices (SX480/GX480, SX570/GX570, SX660/GX660, GX900, GX1150). The DDR4 SDRAM devices operates at 1.2V voltage level and so I/O voltage for Banks 3D, 3E & 3F is fixed to 1.2V.

#### 2.5.3 MicroSD Connector for HPS booting

The Arria10 SoC has dedicated I/O pins for boot devices and other commonly-used peripherals from HPS. The Arria10 SoC SOM uses these dedicated I/O pins to connect MicroSD connector for default boot device. If Micro SD is not required as boot media, then same dedicated pins can be used to connect the eMMC Flash for boot.

MicroSD Card connector (J5) is connected to SD Controller of the Arria10 SoC through dedicated pins. It also supports card detect feature using HPS Dedicated IO "GPIOO\_IO2". The main power to MicroSD Connector is 3.3V Voltage. A voltage Level translator is used to translate the SoC compatible 1.8V signals to 3.3V signals on MicroSD connector. Micro SD connector is physically located on topside of the SOM as shown below.

Figure 4: Micro SD Connector

#### 2.5.4 eMMC Flash for HPS booting (Optional)

The Arria10 SoC SOM supports eMMC Flash as an optional boot device. This is connected to SD/MMC controller of the Arria10 SoC through dedicated pins and operates at 1.8V Voltage level. The eMMC Flash memory is physically located on the bottom side of the SOM. This is the optional feature and will not be populated in the default configuration.

#### 2.5.5 Configuration Flash for FPGA

The Arria10 SoC/FPGA SOM supports Serial Flash for FPGA configuration. This configuration Flash is connected to Active Serial (AS) memory interface of the Arria10 SoC/FPGA and operating at 1.8V Voltage level. It supports AS x1 and AS x4 modes and can be programmed using the AS programming interface or JTAG interface.

Using the AS programming interface, the configuration data is programmed into the configuration Flash by the Quartus Prime software or any supported third-party software. Using the JTAG interface, an Altera IP called the SFL IP core must be downloaded into the Arria10 device to form a bridge between the JTAG interface and the configuration Flash which allows the configuration Flash to be programmed directly using the JTAG interface. The configuration Flash is physically located on bottom of the SOM.

#### 2.6 On-SOM Features

#### 2.6.1 JTAG Header

The Arria10 SoC/FPGA SOM supports a customized 20-pin ARM JTAG connector for JTAG debug interface. Arria10 SoC/FPGA's JTAG interface pins are 1.8V tolerant and so 1.8V reference power is provided to pin1 of the JTAG connector. This allows the JTAG tool to automatically configure the logic signals to the right voltage.

The Arria10 HPS and FPGA share a common set of JTAG pins and each have their own TAP controller which are chained together inside the Arria10 device. During power on-reset, the JTAG and all debug fuses are read by the Configuration subsystem to determine if the JTAG to the FPGA or HPS is bypassed. These JTAG interface signals are also connected to Board to Board Connector2 to access from carrier board. The JTAG connector (J2) is physically located on topside of the SOM as shown below.

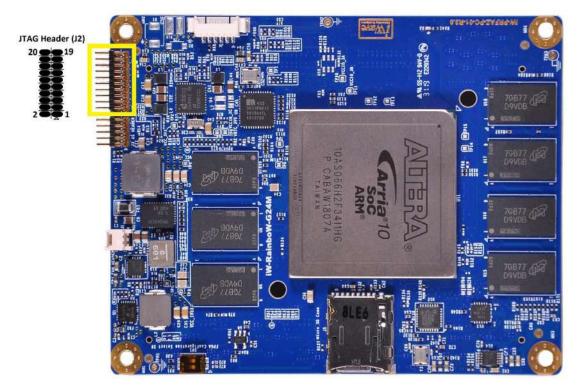

Figure 5: JTAG Header

Number of Pins - 20

Connector Part - GRPB102MWCN-RC from Sullins Connector Solutions

Mating Connector - LPPB102CFFN-RC from Sullins Connector Solutions

Table 6: JTAG Header Pin Assignment

| Pin | o           | Signal Type/  | Description              |  |

|-----|-------------|---------------|--------------------------|--|

| No  | Signal Name | Termination   |                          |  |

| 1   | VCC_1V8     | O, 1.8V Power | VTREF Voltage Reference. |  |

| 2   | VCC_1V8     | O, 1.8V Power | Supply Voltage.          |  |

| 3   | CSS_TRST    | I, 1.8V CMOS/ | JTAG test reset signal.  |  |

|     |             | 10K PU        |                          |  |

| 4   | GND         | Power         | Ground.                  |  |

| 5   | CSS_TDI     | I, 1.8V CMOS/ | JTAG test data input.    |  |

|     |             | 10K PU        |                          |  |

| 6   | GND         | Power         | Ground.                  |  |

| 7   | CSS_TMS     | I, 1.8V CMOS/ | JTAG test mode select.   |  |

|     |             | 10K PU        |                          |  |

| 8   | GND         | Power         | Ground.                  |  |

| 9   | CSS_TCK     | I, 1.8V CMOS  | JTAG test Clock.         |  |

| 10  | GND         | Power         | Ground.                  |  |

| 11  | -           | -             | NC.                      |  |

| 12  | GND         | Power         | Ground.                  |  |

| 13  | CSS_TDO     | O, 1.8V CMOS  | JTAG test data output.   |  |

| 14  | GND         | Power         | Ground.                  |  |

| 15  | -           | -             | NC.                      |  |

| 16  | GND         | Power         | Ground.                  |  |

| 17  | -           | -             | NC.                      |  |

| 18  | GND         | Power         | Ground.                  |  |

| 19  | -           | -             | NC.                      |  |

| 20  | GND         | Power         | Ground.                  |  |

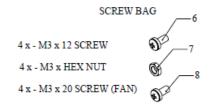

#### 2.6.2 Fan Header

The Arria10 SoC/FPGA SOM supports a Fan Header to connect cooling Fan if required. Also in SOM there are mounting holes in either side of the Arria10 SoC/FPGA device which can be used to fix the Fan. This Fan Header (J1) is physically located at the top of the board as shown below.

Figure 6: Fan Header

Number of Pins - 2

Connector Part - 0530480210 from Molex

Mating Connector - 51021-0200 from Molex

Compatible FAN (Example) - AFB0505MB from Delta Electronics

**Table 7: FAN Header Pin Assignment**

| Pin<br>No | Signal Name | Signal Type/<br>Termination | Description              |

|-----------|-------------|-----------------------------|--------------------------|

| 1         | VCC_5V      | O, Power                    | +5V Power output to FAN. |

| 2         | GND         | Power                       | Ground.                  |

#### 2.6.3 FPGA AS Header

The Arria10 SoC/FPGA SOM supports FPGA AS header for Active Serial Interface. This Active Serial Interface can be used to program the FPGA configuration Flash. Using this AS header, the external programmer serially transmits the operation commands and configuration bits to the configuration flash on Data0 using the download cable. During the verification, DATA1 transfers the programming data back to the download cable. Also the same AS interface signals are optionally connected to Board to Board connector 244, 62, 64, 66, 68, 69, 71, 72. This FPGA AS Header (J3) is physically located at the top of the board as shown below.

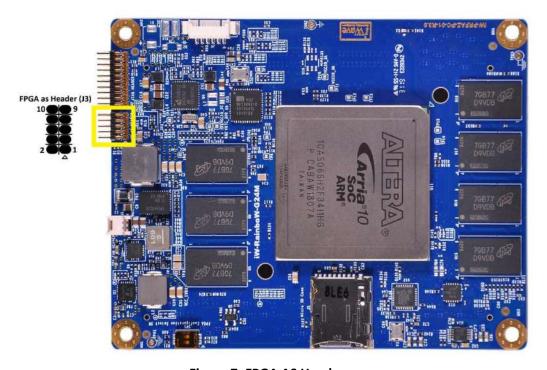

Figure 7: FPGA AS Header

Number of Pins - 10

Connector Part - GRPB052MWCN-RC from Sullins Connector Solutions

Mating Connector - LPPB052CFFN-RC from Sullins Connector Solutions

**Table 8: FPGA AS Header Pin Assignment**

| Pin<br>No | Signal Name    | Signal Type/<br>Termination | Description                                                                                                                                        |

|-----------|----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | CSS_DCLK       | I, 1.8V CMOS/10K PD         | Dedicated Serial clock to configure flash.  Note: This Same signal is optionally connected to 62 <sup>nd</sup> pin of Board to Board connector2.   |

| 2         | GND            | Power                       | Ground.  Note: AS_STATUS signal is optionally connected to this pin.                                                                               |

| 3         | AS_CONFIG_DONE | IO, 1.8V OD/10K PU          | Configuration status IO to Arria10 SoC/FPGA.  Note: This Same signal is optionally connected to 64 <sup>th</sup> pin of Board to Board connector2. |

| 4  | VCC_1V8      | O,1.8V Power        | Supply Voltage.                                       |

|----|--------------|---------------------|-------------------------------------------------------|

| 5  | AS_CONFIG    | I, 1.8V CMOS/10K PU | Configuration input to Arria10 SoC/FPGA.              |

|    |              |                     | Note: This Same signal is optionally connected        |

|    |              |                     | to 66 <sup>th</sup> pin of Board to Board connector2. |

| 6  | CSS_nCE      | I, 1.8V CMOS/10K PD | Chip Enable input to Arria10 SoC/FPGA.                |

|    |              |                     | Note: This Same signal is optionally connected        |

|    |              |                     | to 44 <sup>th</sup> pin of Board to Board connector2. |

| 7  | CSS_AS_DATA0 | I, 1.8V CMOS        | Serial Data input to Configuration flash.             |

|    |              |                     | Note: This Same signal is optionally connected        |

|    |              |                     | to 71st pin of Board to Board connector2.             |

| 8  | CSS_NCSO0    | I, 1.8V CMOS/10K PU | Chip select input to configuration flash.             |

|    |              |                     | Note: This Same signal is optionally connected        |

|    |              |                     | to 69 <sup>th</sup> pin of Board to Board connector2. |

| 9  | CSS_AS_DATA1 | O, 1.8V CMOS        | Serial Data output from configuration flash.          |

|    |              |                     | Note: This Same signal is optionally connected        |

|    |              |                     | to 72 <sup>nd</sup> pin of Board to Board connector2. |

| 10 | GND          | Power               | Ground.                                               |

Note: In iWave Arria10 SoC/FPGA SOM, DATA0 signal is connected to 7<sup>th</sup> pin & DATA1 Signal is connected to 9<sup>th</sup> pin of FPGA AS Header(J3).

#### 2.7 Board to Board Connector1 Interfaces

The Arria10 SoC/FPGA SOM supports two 240pin High speed ground plane ruggedized terminal strip connectors for interfaces expansion. All the effort is made in Arria10 SoC/FPGA SOM design to provide the maximum interfaces of Arria10 SoC/FPGA to the carrier board by adding these two Board to Board connectors.

The interfaces which are available at Board to Board Connector1 are explained in following sections.

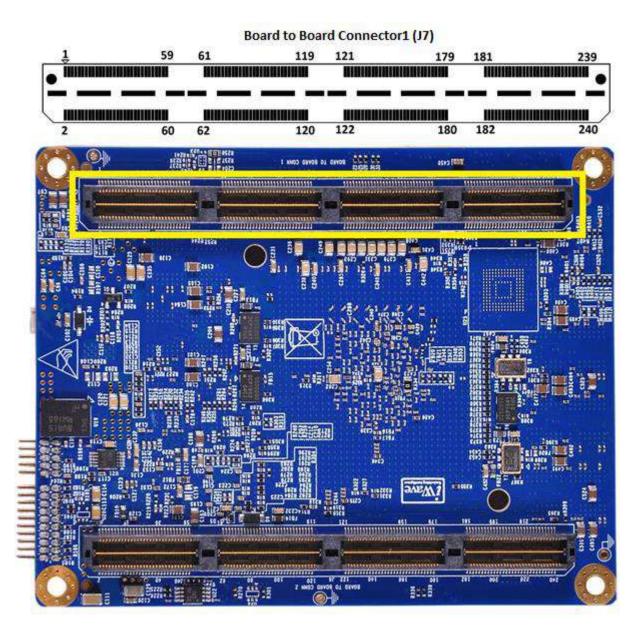

Figure 8: Board to Board Connector1

Number of Pins - 240

Connector Part Number - QTH-120-01-L-D-A

Mating Connector - QSH-120-01-L-D-A from Samtech

Staking Height - 5mm

Table 9 Board to Board Connector1 Pinout

| Signal Name         | B2B-1 Pin | B2B-1 Pin | Signal Name                   |

|---------------------|-----------|-----------|-------------------------------|

| GND                 | 1         | 2         | GND                           |

| GXBL1C_TX_CH0P      | 3         | 4         | REFCLK_GXBL1C_CHTP            |

| GXBL1C_TX_CH0N      | 5         | 6         | REFCLK_GXBL1C_CHTN            |

| GND                 | 7         | 8         | GND                           |

| GXBL1C_TX_CH1P      | 9         | 10        | FPGA_AM7_LVDS3A_24N           |

| GXBL1C_TX_CH1N      | 11        | 12        | FPGA_AM1_LVDS3A_16P           |

| GND                 | 13        | 14        | FPGA_AM2_LVDS3A_16N           |

| GXBL1C_RX_CH1N      | 15        | 16        | FPGA_AP4_LVDS3A_18P           |

| GXBL1C_RX_CH1P      | 17        | 18        | FPGA_AN4_LVDS3A_18N           |

| GND                 | 19        | 20        | GND                           |

| GXBL1C_RX_CH0N      | 21        | 22        | FPGA_AL3_LVDS3A_15N/CLKOUT_0N |

| GXBL1C_RX_CH0P      | 23        | 24        | FPGA_AM3_LVDS3A_15P/CLKOUT_0P |

| GND                 | 25        | 26        | GND                           |

| FPGA_AM6_LVDS3A_17P | 27        | 28        | FPGA_AP6_LVDS3A_20N           |

| FPGA_AM5_LVDS3A_17N | 29        | 30        | FPGA_AP7_LVDS3A_20P           |

| FPGA_AP5_LVDS3A_19P | 31        | 32        | FPGA_AL6_LVDS3A_14P           |

| FPGA_AN5_LVDS3A_19N | 33        | 34        | FPGA_AK6_LVDS3A_14N           |

| GND                 | 35        | 36        | GND                           |

| GXBL1C_TX_CH2P      | 37        | 38        | FPGA_AK7_LVDS3A_9P            |

| GXBL1C_TX_CH2N      | 39        | 40        | FPGA_AK8_LVDS3A_9N            |

| GND                 | 41        | 42        | FPGA_AJ6_LVDS3A_11N           |

| GXBL1C_TX_CH3P      | 43        | 44        | FPGA_AJ7_LVDS3A_11P           |

| GXBL1C_TX_CH3N      | 45        | 46        | FPGA_AH7_LVDS3A_8P            |

| GND                 | 47        | 48        | FPGA_AG7_LVDS3A_8N            |

| GXBL1C_RX_CH3N      | 49        | 50        | FPGA_AH8_LVDS3A_7P            |

| GXBL1C_RX_CH3P      | 51        | 52        | FPGA_AG8_LVDS3A_7N            |

| GND                 | 53        | 54        | GND                           |

| GXBL1C_RX_CH2N      | 55        | 56        | FPGA_AL4_LVDS3A_13N/CLKIN_0N  |

| GXBL1C_RX_CH2P      | 57        | 58        | FPGA_AL5_LVDS3A_13P/CLKIN_0P  |

| GND                 | 59        | 60        | GND                           |

|                     |           |           |                               |

| GND                 | 61        | 62        | GND                           |

| GXBL1C_TX_CH4P      | 63        | 64        | REFCLK_GXBL1C_CHBP            |

| GXBL1C_TX_CH4N      | 65        | 66        | REFCLK_GXBL1C_CHBN            |

| GND                 | 67        | 68        | GND                           |

| GXBL1C_TX_CH5P      | 69        | 70        | FPGA_AG10_LVDS3A_4P           |

| GXBL1C_TX_CH5N      | 71        | 72        | FPGA_AF10_LVDS3A_4N           |

| GND                 | 73        | 74        | FPGA_AN8_LVDS3A_21P           |

| GXBL1C_RX_CH5N      | 75        | 76        | FPGA_AM8_LVDS3A_21N           |

| GXBL1C_RX_CH5P      | 77        | 78        | FPGA_AL9_LVDS3A_23P           |

| GND                 | 79        | 80        | GND                           |

| Signal Name          | B2B-1 Pin | B2B-1 Pin | Signal Name                    |

|----------------------|-----------|-----------|--------------------------------|

| GXBL1C_RX_CH4N       | 81        | 82        | FPGA_AK9_LVDS3A_12N/CLKIN_1N   |

| GXBL1C_RX_CH4P       | 83        | 84        | FPGA_AJ9_LVDS3A_12P/CLKIN_1P   |

| GND                  | 85        | 86        | GND                            |

| FPGA_AF9_LVDS3A_1P   | 87        | 88        | FPGA_AN9_LVDS3A_22N            |

| FPGA_AE9_LVDS3A_1N   | 89        | 90        | FPGA_AP9_LVDS3A_22P            |

| FPGA_AF8_LVDS3A_2P   | 91        | 92        | FPGA_AH10_LVDS3A_3P            |

| FPGA_AE8_LVDS3A_2N   | 93        | 94        | FPGA_AH9_LVDS3A_3N             |

| GND                  | 95        | 96        | GND                            |

| GXBL1D_TX_CH0P       | 97        | 98        | REFCLK_GXBL1D_CHTP             |

| GXBL1D_TX_CH0N       | 99        | 100       | REFCLK_GXBL1D_CHTN             |

| GND                  | 101       | 102       | GND                            |

| GXBL1D_TX_CH1P       | 103       | 104       | FPGA_AL8_LVDS3A_23N            |

| GXBL1D_TX_CH1N       | 105       | 106       | FPGA_AG11_LVDS3A_5N            |

| GND                  | 107       | 108       | FPGA_AF11_LVDS3A_5P            |

| GXBL1D_RX_CH1N       | 109       | 110       | FPGA_AE11_LVDS3A_6N            |

| GXBL1D_RX_CH1P       | 111       | 112       | FPGA_AE12_LVDS3A_6P            |

| GND                  | 113       | 114       | GND                            |

| GXBL1D_RX_CH0N       | 115       | 116       | FPGA_AH5_LVDS3A_10N/CLKOUT_1N  |

| GXBL1D_RX_CH0P       | 117       | 118       | FPGA_AJ5_LVDS3A_10P/CLKOUT_1P  |

| GND                  | 119       | 120       | GND                            |

|                      |           |           |                                |

| GND                  | 121       | 122       | GND                            |

| GXBL1D_TX_CH2P       | 123       | 124       | FPGA_AG17_LVDS2A_15P/CLKOUT_0P |

| GXBL1D_TX_CH2N       | 125       | 126       | FPGA_AH17_LVDS2A_15N/CLKOUT_0N |

| GND                  | 127       | 128       | FPGA_AD19_LVDS2A_21P           |

| GXBL1D_TX_CH3P       | 129       | 130       | FPGA_AH18_LVDS2A_13P/CLKIN_0P  |

| GXBL1D_TX_CH3N       | 131       | 132       | FPGA_AH19_LVDS2A_13N/CLKIN_0N  |

| GND                  | 133       | 134       | FPGA_AE18_LVDS2A_21N           |

| GXBL1D_RX_CH3N       | 135       | 136       | FPGA_AJ17_LVDS2A_16P           |

| GXBL1D_RX_CH3P       | 137       | 138       | FPGA_AK17_LVDS2A_16N           |

| GND                  | 139       | 140       | GND                            |

| GXBL1D_RX_CH2N       | 141       | 142       | FPGA_AM16_LVDS2A_10N/CLKOUT_0N |

| GXBL1D_RX_CH2P       | 143       | 144       | FPGA_AL16_LVDS2A_10P/CLKOUT_0P |

| GND                  | 145       | 146       | GND                            |

| FPGA_AP16_LVDS2A_2P  | 147       | 148       | FPGA_AP12_LVDS2A_5N            |

| FPGA_AP17_LVDS2A_2N  | 149       | 150       | FPGA_AN12_LVDS2A_5P            |

| FPGA_AL18_LVDS2A_11N | 151       | 152       | FPGA_AH15_LVDS2A_17N           |

| FPGA_AK18_LVDS2A_11P | 153       | 154       | FPGA_AJ15_LVDS2A_17P           |

| GND                  | 155       | 156       | GND                            |

| GXBL1D_TX_CH4P       | 157       | 158       | REFCLK_GXBL1D_CHBP             |

| GXBL1D_TX_CH4N       | 159       | 160       | REFCLK_GXBL1D_CHBN             |

| GND                  | 161       | 162       | GND                            |

| Signal Name         | B2B-1 Pin | B2B-1 Pin | Signal Name          |

|---------------------|-----------|-----------|----------------------|

| GXBL1D_TX_CH5P      | 163       | 164       | FPGA_AG16_LVDS2A_20P |

| GXBL1D_TX_CH5N      | 165       | 166       | FPGA_AF16_LVDS2A_20N |

| GND                 | 167       | 168       | FPGA_AE17_LVDS2A_19n |

| GXBL1D_RX_CH5N      | 169       | 170       | FPGA_AE16_LVDS2A_19P |

| GXBL1D_RX_CH5P      | 171       | 172       | FPGA_AC17_LVDS2A_24P |

| GND                 | 173       | 174       | GND                  |

| GXBL1D_RX_CH4N      | 175       | 176       | FPGA_AH14_LVDS2A_14N |

| GXBL1D_RX_CH4P      | 177       | 178       | FPGA_AJ14_LVDS2A_14P |

| GND                 | 179       | 180       | GND                  |

|                     |           |           |                      |

| GND                 | 181       | 182       | GND                  |

| GXBL1E_TX_CH0P      | 183       | 184       | REFCLK_GXBL1E_CHTP   |

| GXBL1E_TX_CH0N      | 185       | 186       | REFCLK_GXBL1E_CHTN   |

| GND                 | 187       | 188       | GND                  |

| GXBL1E_TX_CH1P      | 189       | 190       | FPGA_AD17_LVDS2A_24N |

| GXBL1E_TX_CH1N      | 191       | 192       | FPGA_AE19_LVDS2A_22N |

| GND                 | 193       | 194       | FPGA_AF19_LVDS2A_22P |

| GXBL1E_RX_CH1N      | 195       | 196       | FPGA_AF18_LVDS2A_23P |

| GXBL1E_RX_CH1P      | 197       | 198       | FPGA_AG18_LVDS2A_23N |

| GND                 | 199       | 200       | GND                  |

| GXBL1E_RX_CH0N      | 201       | 202       | FPGA_AN17_LVDS2A_8N  |

| GXBL1E_RX_CH0P      | 203       | 204       | FPGA_AM17_LVDS2A_8P  |

| GND                 | 205       | 206       | GND                  |

| FPGA_AP15_LVDS2A_3N | 207       | 208       | FPGA_AP14_LVDS2A_6N  |

| FPGA_AN15_LVDS2A_3P | 209       | 210       | FPGA_AN14_LVDS2A_6P  |

| FPGA_AM18_LVDS2A_7P | 211       | 212       | FPGA_AL14_LVDS2A_9P  |

| FPGA_AN18_LVDS2A_7N | 213       | 214       | FPGA_AK14_LVDS2A_9N  |

| GND                 | 215       | 216       | GND                  |

| GXBL1E_TX_CH2P      | 217       | 218       | REFCLK_GXBL1E_CHBP   |

| GXBL1E_TX_CH2N      | 219       | 220       | REFCLK_GXBL1E_CHBN   |

| GND                 | 221       | 222       | GND                  |

| GXBL1E_TX_CH3P      | 223       | 224       | FPGA_AL15_LVDS2A_12N |

| GXBL1E_TX_CH3N      | 225       | 226       | FPGA_AK13_LVDS2A_1N  |

| GND                 | 227       | 228       | FPGA_AL13_LVDS2A_1P  |

| GXBL1E_RX_CH3N      | 229       | 230       | FPGA_AJ16_LVDS2A_18P |

| GXBL1E_RX_CH3P      | 231       | 232       | SOMPWR_EN            |

| GND                 | 233       | 234       | GND                  |

| GXBL1E_RX_CH2N      | 235       | 236       | FPGA_AM13_LVDS2A_4N  |

| GXBL1E_RX_CH2P      | 237       | 238       | FPGA_AN13_LVDS2A_4P  |

| GND                 | 239       | 240       | GND                  |

#### 2.7.1 FPGA High Speed Transceivers

The Arria10 SoC/FPGA SOM supports 16 high speed transceiver channels (6 from 1C bank, 6 from 1D bank & 4 from 1E bank) on Board to Board connector1. In Arria10 SoC/FPGA SOM, Transceiver power to Arria10 SoC/FPGA is fixed to 1.03V. Also it supports 100MHz Oscillator on board for transceiver reference clock and connected to Bank2A AK16 CLKUSR pin.

For more details on High Speed transceiver pinouts on Board to Board Connector1, refer the below table.

| B2B-1  | B2B Connector1   | SoC Ball Name/  | Signal Type/ | Donasistics.                       |  |  |  |

|--------|------------------|-----------------|--------------|------------------------------------|--|--|--|

| Pin No | Pin Name         | Pin Number      | Termination  | Description                        |  |  |  |

|        | BANK-1C Channels |                 |              |                                    |  |  |  |

| 3      | GXBL1C_TX_CH0p   | GXBL1C_TX_CH0P/ | O, DIFF      | Bank1C channel0 High speed         |  |  |  |

|        |                  | AP32            |              | differential transmitter positive. |  |  |  |

| 5      | GXBL1C_TX_CH0n   | GXBL1C_TX_CH0N/ | O, DIFF      | Bank1C channel0 High speed         |  |  |  |

|        |                  | AP31            |              | differential transmitter Negative. |  |  |  |

| 23     | GXBL1C_RX_CH0p   | GXBL1C_RX_CH0P/ | I, DIFF      | Bank1C channel0 High speed         |  |  |  |

|        |                  | AL30            |              | differential receiver positive.    |  |  |  |

| 21     | GXBL1C_RX_CH0n   | GXBL1C_RX_CH0N/ | I, DIFF      | Bank1C channel0 High speed         |  |  |  |

|        |                  | AL29            |              | differential receiver Negative.    |  |  |  |

| 9      | GXBL1C_TX_CH1p   | GXBL1C_TX_CH1P/ | O, DIFF      | Bank1C channel1 High speed         |  |  |  |

|        |                  | AM32            |              | differential transmitter positive. |  |  |  |

| 11     | GXBL1C_TX_CH1n   | GXBL1C_TX_CH1N/ | O, DIFF      | Bank1C channel1 High speed         |  |  |  |

|        |                  | AM31            |              | differential transmitter Negative. |  |  |  |

| 17     | GXBL1C_RX_CH1p   | GXBL1C_RX_CH1P/ | I, DIFF      | Bank1C channel1 High speed         |  |  |  |

|        |                  | AJ30            |              | differential receiver positive.    |  |  |  |

| 15     | GXBL1C_RX_CH1n   | GXBL1C_RX_CH1N/ | I, DIFF      | Bank1C channel1 High speed         |  |  |  |

|        |                  | AJ29            |              | differential receiver Negative.    |  |  |  |

| 37     | GXBL1C_TX_CH2p   | GXBL1C_TX_CH2P/ | O, DIFF      | Bank1C channel2 High speed         |  |  |  |

|        |                  | AK32            |              | differential transmitter positive. |  |  |  |

| 39     | GXBL1C_TX_CH2n   | GXBL1C_TX_CH2N/ | O, DIFF      | Bank1C channel2 High speed         |  |  |  |

|        |                  | AK31            |              | differential transmitter Negative. |  |  |  |

| 57     | GXBL1C_RX_CH2p   | GXBL1C_RX_CH2P/ | I, DIFF      | Bank1C channel2 High speed         |  |  |  |

|        |                  | AG30            |              | differential receiver positive.    |  |  |  |

| 55     | GXBL1C_RX_CH2n   | GXBL1C_RX_CH2N/ | I, DIFF      | Bank1C channel2 High speed         |  |  |  |

|        |                  | AG29            |              | differential receiver Negative.    |  |  |  |

| 43     | GXBL1C_TX_CH3p   | GXBL1C_TX_CH3P/ | O, DIFF      | Bank1C channel3 High speed         |  |  |  |

| a-     | CVDIAC TV CUC    | AH32            | 0.0155       | differential transmitter positive. |  |  |  |

| 45     | GXBL1C_TX_CH3n   | GXBL1C_TX_CH3N/ | O, DIFF      | Bank1C channel3 High speed         |  |  |  |

|        | CVDIAC DV CUC    | AH31            | 1 5155       | differential transmitter Negative. |  |  |  |

| 51     | GXBL1C_RX_CH3p   | GXBL1C_RX_CH3P/ | I, DIFF      | Bank1C channel3 High speed         |  |  |  |

|        | 0/2/40 5/: 5/:5  | AF32            | . 5.5-       | differential receiver positive.    |  |  |  |

| 49     | GXBL1C_RX_CH3n   | GXBL1C_RX_CH3N/ | I, DIFF      | Bank1C channel3 High speed         |  |  |  |

|        |                  | AF31            |              | differential receiver Negative.    |  |  |  |

| B2B-1  | B2B Connector1     | SoC Ball Name/      | Signal Type/ |                                    |

|--------|--------------------|---------------------|--------------|------------------------------------|

| Pin No | Pin Name           | Pin Number          | Termination  | Description                        |

| 63     | GXBL1C_TX_CH4p     | GXBL1C_TX_CH4P/     | O, DIFF      | Bank1C channel4 High speed         |

|        |                    | AN34                | ,            | differential transmitter positive. |

| 65     | GXBL1C_TX_CH4n     | GXBL1C_TX_CH4N/     | O, DIFF      | Bank1C channel4 High speed         |

|        |                    | AN33                |              | differential transmitter Negative. |

| 83     | GXBL1C_RX_CH4p     | GXBL1C_RX_CH4P/     | I, DIFF      | Bank1C channel4 High speed         |

|        |                    | AE30                |              | differential receiver positive.    |

| 81     | GXBL1C_RX_CH4n     | GXBL1C_RX_CH4N/     | I, DIFF      | Bank1C channel4 High speed         |

|        |                    | AE29                |              | differential receiver Negative.    |

| 69     | GXBL1C_TX_CH5p     | GXBL1C_TX_CH5P/     | O, DIFF      | Bank1C channel5 High speed         |

|        |                    | AL34                |              | differential transmitter positive. |

| 71     | GXBL1C_TX_CH5n     | GXBL1C TX CH5N/     | O, DIFF      | Bank1C channel5 High speed         |

|        |                    | AL33                | ,            | differential transmitter Negative. |

| 77     | GXBL1C_RX_CH5p     | GXBL1C_RX_CH5P/     | I, DIFF      | Bank1C channel5 High speed         |

|        |                    | AD32                |              | differential receiver positive.    |

| 75     | GXBL1C_RX_CH5n     | GXBL1C_RX_CH5N/     | I, DIFF      | Bank1C channel5 High speed         |

|        |                    | AD31                |              | differential receiver Negative.    |

| 64     | REFCLK_GXBL1C_CHBp | REFCLK_GXBL1C_CHBP/ | I, DIFF      | Bank1C differential Bottom         |

|        |                    | AF28                |              | reference clock positive.          |

| 66     | REFCLK_GXBL1C_CHBn | REFCLK_GXBL1C_CHBN/ | I, DIFF      | Bank1C differential Bottom         |

|        |                    | AF27                |              | reference clock Negative.          |

| 4      | REFCLK_GXBL1C_CHTp | REFCLK_GXBL1C_CHTP/ | I, DIFF      | Bank1C differential Top reference  |

|        |                    | AD28                |              | clock positive.                    |

| 6      | REFCLK_GXBL1C_CHTn | REFCLK_GXBL1C_CHTN/ | I, DIFF      | Bank1C differential Top reference  |

|        |                    | AD27                |              | clock Negative.                    |

|        |                    | BANK-1D Char        | nnels        |                                    |

| 97     | GXBL1D_TX_CH0P     | GXBL1D_TX_CH0p/     | O, DIFF      | Bank1D channel0 High speed         |

|        |                    | AJ34                |              | differential transmitter positive. |

| 99     | GXBL1D_TX_CH0N     | GXBL1D_TX_CH0n/     | O, DIFF      | Bank1D channel0 High speed         |

|        |                    | AJ33                |              | differential transmitter Negative. |

| 117    | GXBL1D_RX_CH0P     | GXBL1D_RX_CH0p/     | I, DIFF      | Bank1D channel0 High speed         |

|        |                    | AC30                |              | differential receiver positive.    |

| 115    | GXBL1D_RX_CH0N     | GXBL1D_RX_CH0n/     | I, DIFF      | Bank1D channel0 High speed         |

|        |                    | AC29                |              | differential receiver Negative.    |

| 103    | GXBL1D_TX_CH1P     | GXBL1D_TX_CH1p/     | O, DIFF      | Bank1D channel1 High speed         |

| 4.05   | CVDIAD TV CUIT     | AG34                | 0.5:55       | differential transmitter positive. |

| 105    | GXBL1D_TX_CH1N     | GXBL1D_TX_CH1n/     | O, DIFF      | Bank1D channel1 High speed         |

| 444    | CVDIAD DV CUAD     | AG33                | I DIEE       | differential transmitter Negative. |

| 111    | GXBL1D_RX_CH1P     | GXBL1D_RX_CH1p/     | I, DIFF      | Bank1D channel1 High speed         |

| 400    | CVDIAD BY CHAN     | AB32                | I DIEE       | differential receiver positive.    |

| 109    | GXBL1D_RX_CH1N     | GXBL1D_RX_CH1n/     | I, DIFF      | Bank1D channel1 High speed         |

|        |                    | AB31                |              | differential receiver Negative.    |

| B2B-1  | B2B Connector1        | SoC Ball Name/         | Signal Type/ |                                                             |  |

|--------|-----------------------|------------------------|--------------|-------------------------------------------------------------|--|

| Pin No | Pin Name              | Pin Number             | Termination  | Description                                                 |  |

| 123    | GXBL1D_TX_CH2P        | GXBL1D_TX_CH2p/        | O, DIFF      | Bank1D channel2 High speed                                  |  |

|        |                       | AE34                   |              | differential transmitter positive.                          |  |

| 125    | GXBL1D_TX_CH2N        | GXBL1D_TX_CH2n/        | O, DIFF      | Bank1D channel2 High speed                                  |  |

|        |                       | AE33                   |              | differential transmitter Negative.                          |  |

| 143    | GXBL1D_RX_CH2P        | GXBL1D_RX_CH2p/        | I, DIFF      | Bank1D channel2 High speed                                  |  |

|        |                       | AA30                   |              | differential receiver positive.                             |  |

| 141    | GXBL1D_RX_CH2N        | GXBL1D_RX_CH2n/        | I, DIFF      | Bank1D channel2 High speed                                  |  |

|        |                       | AA29                   |              | differential receiver Negative.                             |  |

| 129    | GXBL1D_TX_CH3P        | GXBL1D_TX_CH3p/        | O, DIFF      | Bank1D channel3 High speed                                  |  |

|        |                       | AC34                   |              | differential transmitter positive.                          |  |

| 131    | GXBL1D_TX_CH3N        | GXBL1D_TX_CH3n/        | O, DIFF      | Bank1D channel3 High speed                                  |  |

|        |                       | AC33                   |              | differential transmitter Negative.                          |  |

| 137    | GXBL1D_RX_CH3P        | GXBL1D_RX_CH3p/        | I, DIFF      | Bank1D channel3 High speed                                  |  |

|        |                       | Y32                    |              | differential receiver positive.                             |  |

| 135    | GXBL1D_RX_CH3N        | GXBL1D_RX_CH3n/        | I, DIFF      | Bank1D channel3 High speed                                  |  |

|        |                       | Y31                    |              | differential receiver Negative.                             |  |

| 157    | GXBL1D_TX_CH4P        | GXBL1D_TX_CH4p/        | O, DIFF      | Bank1D channel4 High speed                                  |  |

|        | 0/0/10 7/ 0//         | AA34                   | 2 5:         | differential transmitter positive.                          |  |

| 159    | GXBL1D_TX_CH4N        | GXBL1D_TX_CH4n/        | O, DIFF      | Bank1D channel4 High speed                                  |  |

| 477    | CVDIAD DV CHAD        | AA33                   | I DIEE       | differential transmitter Negative.                          |  |

| 177    | GXBL1D_RX_CH4P        | GXBL1D_RX_CH4p/        | I, DIFF      | Bank1D channel4 High speed                                  |  |

| 175    | CYPLID BY CHAN        | W30                    | I DIEE       | differential receiver positive.  Bank1D channel4 High speed |  |

| 175    | GXBL1D_RX_CH4N        | GXBL1D_RX_CH4n/<br>W29 | I, DIFF      | Bank1D channel4 High speed differential receiver Negative.  |  |

| 163    | GXBL1D_TX_CH5P        | GXBL1D TX CH5p/        | O, DIFF      | Bank1D channel5 High speed                                  |  |

| 103    | GVPTID_IV_CU25        | W34                    | O, DIFF      | differential transmitter positive.                          |  |

| 165    | GXBL1D_TX_CH5N        | GXBL1D_TX_CH5n/        | O, DIFF      | Bank1D channel5 High speed                                  |  |

| 103    | GADLID_TA_CITSIN      | W33                    | 0, 5111      | differential transmitter Negative.                          |  |

| 171    | GXBL1D RX CH5P        | GXBL1D_RX_CH5p/        | I, DIFF      | Bank1D channel5 High speed                                  |  |

| 1/1    | GVPFID_IVY_CITSF      | V32                    | 1, 0111      | differential receiver positive.                             |  |

| 169    | GXBL1D RX CH5N        | GXBL1D_RX_CH5n/        | I, DIFF      | Bank1D channel5 High speed                                  |  |

| 103    | GABEID_NA_CHSIV       | V31                    | 1, 5111      | differential receiver Negative.                             |  |

| 158    | REFCLK GXBL1D CHBP    | REFCLK_GXBL1D_CHBp/    | I, DIFF      | Bank1D differential Bottom                                  |  |

|        |                       | AB28                   | ,            | reference clock positive.                                   |  |

| 160    | REFCLK_GXBL1D_CHBN    | REFCLK_GXBL1D_CHBn/    | I, DIFF      | Bank1D differential Bottom                                  |  |

|        | _=======              | AB27                   | '            | reference clock Negative.                                   |  |

| 98     | REFCLK_GXBL1D_CHTP    | REFCLK_GXBL1D_CHTp/    | I, DIFF      | Bank1D differential Top reference                           |  |

|        |                       | Y28                    | '            | clock positive.                                             |  |

| 100    | REFCLK_GXBL1D_CHTN    | REFCLK_GXBL1D_CHTn/    | I, DIFF      | Bank1D differential Top reference                           |  |

|        |                       | Y27                    |              | clock Negative.                                             |  |

|        | I                     | BANK-1E Char           | nels         | Š                                                           |  |

|        | Driving 12 Girdinicio |                        |              |                                                             |  |

| B2B-1  | B2B Connector1     | SoC Ball Name/      | Signal Type/ |                                    |

|--------|--------------------|---------------------|--------------|------------------------------------|

| Pin No | Pin Name           | Pin Number          | Termination  | Description                        |

| 183    | GXBL1E_TX_CH0P     | GXBL1E_TX_CH0p/     | O, DIFF      | Bank1E channel0 High speed         |

|        |                    | U34                 |              | differential transmitter positive. |

| 185    | GXBL1E_TX_CH0N     | GXBL1E_TX_CH0n/     | O, DIFF      | Bank1E channel0 High speed         |

|        |                    | U33                 |              | differential transmitter Negative. |

| 203    | GXBL1E_RX_CH0P     | GXBL1E_RX_CH0p/     | I, DIFF      | Bank1E channel0 High speed         |

|        |                    | U30                 |              | differential receiver positive.    |

| 201    | GXBL1E_RX_CH0N     | GXBL1E_RX_CH0n/     | I, DIFF      | Bank1E channel0 High speed         |

|        |                    | U29                 |              | differential receiver Negative.    |

| 189    | GXBL1E_TX_CH1P     | GXBL1E_TX_CH1p/     | O, DIFF      | Bank1E channel1 High speed         |

|        |                    | R34                 |              | differential transmitter positive. |

| 191    | GXBL1E_TX_CH1N     | GXBL1E_TX_CH1n/     | O, DIFF      | Bank1E channel1 High speed         |

|        |                    | R33                 |              | differential transmitter Negative. |

| 197    | GXBL1E_RX_CH1P     | GXBL1E_RX_CH1p/     | I, DIFF      | Bank1E channel1 High speed         |

|        |                    | T32                 |              | differential receiver positive.    |

| 195    | GXBL1E_RX_CH1N     | GXBL1E_RX_CH1n/     | I, DIFF      | Bank1E channel1 High speed         |

|        |                    | T31                 |              | differential receiver Negative.    |

| 217    | GXBL1E_TX_CH2P     | GXBL1E_TX_CH2p/     | O, DIFF      | Bank1E channel2 High speed         |

|        |                    | N34                 |              | differential transmitter positive. |

| 219    | GXBL1E_TX_CH2N     | GXBL1E_TX_CH2n/     | O, DIFF      | Bank1E channel2 High speed         |

|        |                    | N33                 |              | differential transmitter Negative. |

| 237    | GXBL1E_RX_CH2P     | GXBL1E_RX_CH2p/     | I, DIFF      | Bank1E channel2 High speed         |

|        |                    | R30                 |              | differential receiver positive.    |

| 235    | GXBL1E_RX_CH2N     | GXBL1E_RX_CH2n/     | I, DIFF      | Bank1E channel2 High speed         |

|        |                    | R29                 |              | differential receiver Negative.    |

| 223    | GXBL1E_TX_CH3P     | GXBL1E_TX_CH3p/     | O, DIFF      | Bank1E channel3 High speed         |

|        |                    | L34                 |              | differential transmitter positive. |

| 225    | GXBL1E_TX_CH3N     | GXBL1E_TX_CH3n/     | O, DIFF      | Bank1E channel3 High speed         |

|        |                    | L33                 |              | differential transmitter Negative. |

| 231    | GXBL1E_RX_CH3P     | GXBL1E_RX_CH3p/     | I, DIFF      | Bank1E channel3 High speed         |

|        | 0/2/45 5// 0//0/   | P32                 |              | differential receiver positive.    |

| 229    | GXBL1E_RX_CH3N     | GXBL1E_RX_CH3n/     | I, DIFF      | Bank1E channel3 High speed         |

| 40-    | DEECH CYDIAT CHT   | P31                 | I DIES       | differential receiver Negative.    |

| 184    | REFCLK_GXBL1E_CHTP | REFCLK_GXBL1E_CHTp/ | I, DIFF      | Bank1E differential Top reference  |

| 400    | DEECH CYPLAS CUTY  | T28                 | I DIEE       | clock positive.                    |

| 186    | REFCLK_GXBL1E_CHTN | REFCLK_GXBL1E_CHTn/ | I, DIFF      | Bank1E differential Top reference  |

| 240    | DEECLY CANAT CHES  | T27                 | I DIEC       | clock Negative.                    |

| 218    | REFCLK_GXBL1E_CHBP | REFCLK_GXBL1E_CHBp/ | I, DIFF      | Bank1E differential Bottom         |

| 222    | DEECH CYDIAE CHES  | V28                 | I DIEE       | reference clock positive.          |