# PCIe X1 IP Core - Lattice Radiant Software

**User Guide**

FPGA-IPUG-02091-1.3

December 2020

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## **Contents**

| Acronyms in   | This Document                                       | 6  |

|---------------|-----------------------------------------------------|----|

| 1. Introdu    | ction                                               | 7  |

|               | uick Facts                                          |    |

|               | atures                                              |    |

| 1.3. Co       | onventions                                          | 9  |

| 1.3.1.        | Nomenclature                                        | 9  |

| 1.3.2.        | Signal Names                                        | 9  |

| 2. Function   | nal Description                                     | 10 |

| 2.1. Oʻ       | <i>v</i> erview                                     | 10 |

| 2.1.1.        | Block Diagram                                       |    |

| 2.1.2.        | Endpoint/Root Port Configurations                   |    |

| 2.1.3.        | ECC and Parity Data Path Protection                 |    |

| 2.1.4.        | LTSSM State Definitions                             |    |

| 2.1.5.        | Multi-Function Support                              | 17 |

| 2.1.6.        | Root Port Operation                                 |    |

| 2.1.7.        | Root Port Configuration                             |    |

| 2.1.8.        | Error Handling                                      |    |

| 2.1.9.        | Power Management                                    |    |

| 2.1.10.       | PCIe X1 Core Buffers                                |    |

|               | User Interface Options                              |    |

|               | DMA Support                                         |    |

|               | gnal Description                                    |    |

| 2.2.1.        | Clock and Reset                                     |    |

| 2.2.2.        | PHY Interface                                       |    |

| 2.2.3.        | Transaction Layer Interface                         |    |

| 2.2.4.        | Lattice Memory Mapped Interface (LMMI)              |    |

| 2.2.5.        | Legacy Interrupt Interface                          |    |

| 2.2.6.        | Power Management Interface                          |    |

| 2.2.7.        | Configuration Space Register Interface (UCFG)       |    |

| 2.2.8.        | AHB-Lite Data Interface                             |    |

| 2.2.9.        | AHB-Lite Configuration Interface                    |    |

|               | APB Configuration Interface                         |    |

|               | AXI4-Stream Data Interface                          |    |

|               | DMA Interrupt Interface                             |    |

|               | tribute Summary                                     |    |

|               | gister Description                                  |    |

|               | Hard IP Core Configuration and Status Registers     |    |

| 2.4.2.        | PCI Express Configuration Space Registers           |    |

| 2.4.3.        | Soft IP Configuration, Control and Status Registers |    |

|               | ration                                              |    |

|               | censing the IP Core                                 |    |

|               | etting Started                                      |    |

|               | onfiguring the IP Core                              |    |

|               | stantiating the IP Core                             |    |

| -             | inthesizing and Implementing the IP Core            |    |

|               | Inning Functional Simulation                        |    |

|               | ardware Evaluation                                  |    |

|               | g Part Number                                       |    |

|               | Resource Utilization                                |    |

|               |                                                     |    |

| -             | oport Assistance                                    |    |

| REVISION HIST | ory                                                 |    |

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Figures

| Figure 2.1. Lattice PCIe X1 Core Block Diagram                                                 | 10  |

|------------------------------------------------------------------------------------------------|-----|

| Figure 2.2. Lattice PCIe X1 Core Hard IP                                                       | 10  |

| Figure 2.3. Endpoint and Root Port Applications                                                | 12  |

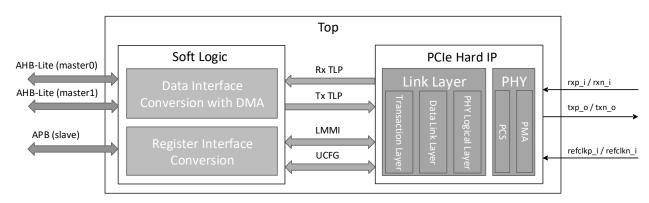

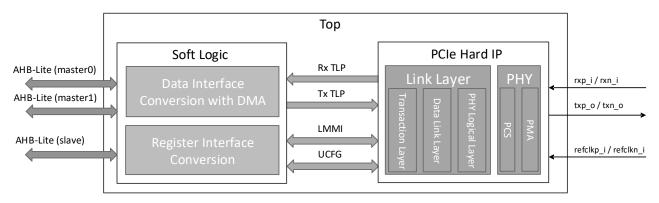

| Figure 2.4. AHB-Lite Data Interface, APB Register Interface                                    | 25  |

| Figure 2.5. AHB-Lite Data Interface, AHB-Lite Register Interface                               | 26  |

| Figure 2.6. AHB-Lite Data Interface shared with Register Interface                             | 26  |

| Figure 2.7. AHB-Lite Data Interface with DMA, APB Register Interface                           | 26  |

| Figure 2.8. AHB-Lite Data Interface with DMA, AHB-Lite Register Interface                      | 27  |

| Figure 2.9. AXI4-Stream Data Interface, APB Register Interface                                 | 27  |

| Figure 2.10. AXI4-Stream Data Interface, AHB-Lite Register Interface                           |     |

| Figure 2.11. AHB-Lite to PCIe Data Transfer                                                    |     |

| Figure 2.12. PCIe to AHB-Lite Data Transfer                                                    |     |

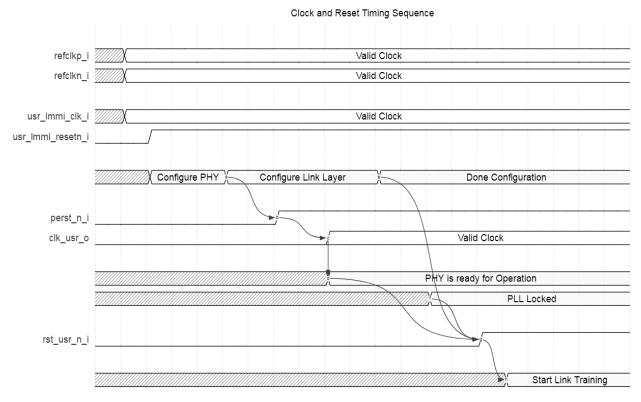

| Figure 2.13. Clock and Reset Sequence Diagram                                                  |     |

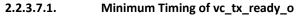

| Figure 2.14. Transmit Interface Example Transactions – Minimum vc_tx_ready_o Timing            | 44  |

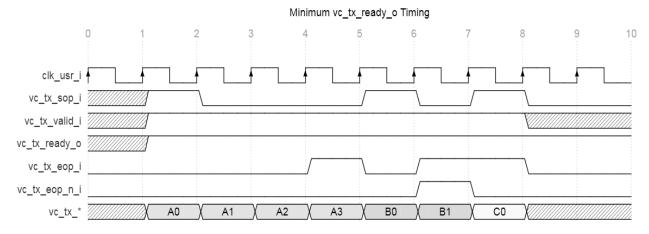

| Figure 2.15. Transmit Interface Example Transactions – Example Wait State vc_tx_ready_o Timing | 45  |

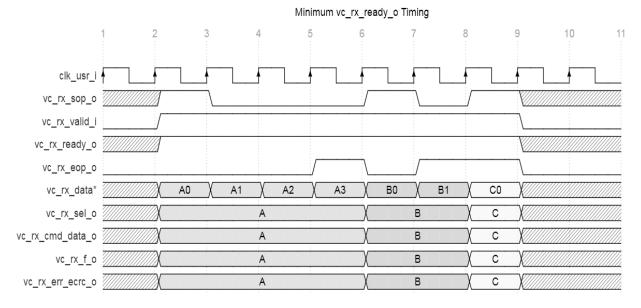

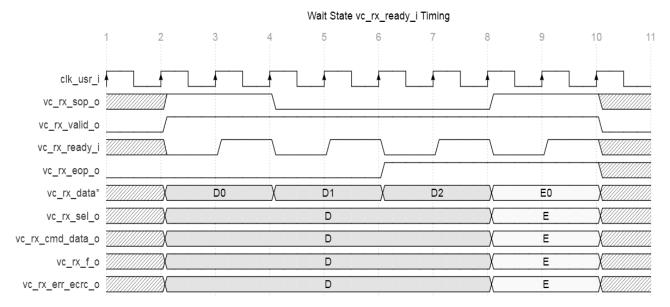

| Figure 2.16. Receive Interface – Minimum vc_rx_ready_i Timing                                  |     |

| Figure 2.17. Receive Interface – Wait State vc_rx_ready_i Timing                               | 47  |

| Figure 3.1. Select PCIe X1 IP                                                                  |     |

| Figure 3.2. Configure Module/IP Block Wizard                                                   |     |

| Figure 3.3. Lattice PCIe X1 Core Configuration User Interface (General Tab)                    | 222 |

| Figure 3.4. Lattice PCIe X1 Core Configuration Interface (Flow Control Tab)                    | 223 |

| Figure 3.5. Lattice PCIe X1 Core Configuration User Interface (Function 0 Tab)                 |     |

| Figure 3.6. Check Generated IP                                                                 | 224 |

| Figure 3.7. Generated IP Core Directory Structure                                              |     |

| Figure 3.8. Generated IP Core Directory Structure                                              |     |

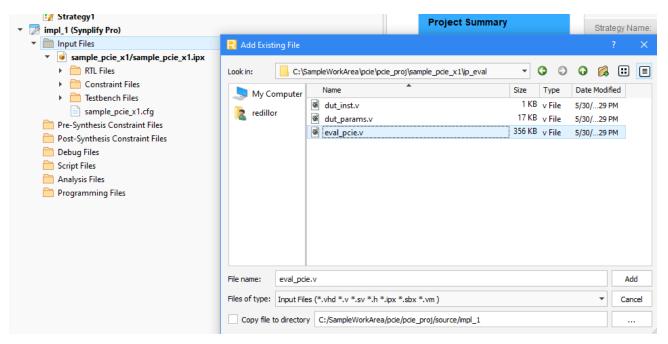

| Figure 3.9. Include eval_pcie.v top Design Module                                              |     |

| Figure 3.10. Run Synthesis Flow                                                                |     |

| Figure 3.11. Synthesis Flow Status                                                             |     |

| Figure 3.12. Include tb_top.v as Testbench File                                                | 227 |

| Figure 3.13. Simulation Wizard                                                                 | 227 |

## Tables

| Table 1.1. Lattice PCIe X1 IP Core Quick Facts | 7  |

|------------------------------------------------|----|

| Table 2.1. LTSSM State Definitions             | 14 |

| Table 2.2. Single-Ended I/O Standards          | 17 |

| Table 2.3. General PCI Express Error List      | 20 |

| Table 2.4. Physical Layer Error List           |    |

| Table 2.5. Data Link Layer Error List          | 20 |

| Table 2.6. Transaction Layer Error List        | 20 |

| Table 2.7. Descriptor Entry Format             | 29 |

| Table 2.8. Clock and Reset Port Descriptions   | 32 |

| Table 2.9. PHY Interface                       | 35 |

| Table 2.10. Transmit Interface                 | 37 |

| Table 2.11. Transmit Credit Interface          | 38 |

| Table 2.12. Receive Interface                  | 39 |

|                                                |    |

| Table 2.13. Receive Credit  | t Interface                           | 42  |

|-----------------------------|---------------------------------------|-----|

|                             | t Interface                           |     |

| Table 2.15. Lattice Memo    | ry Mapped interface (LMMI)            |     |

| Table 2.16. Legacy Interru  | ıpt Interface                         | 49  |

| Table 2.17. Power Manage    | ement Interface                       | 50  |

| Table 2.18. UCFG Interfac   | e Port Description                    | 51  |

| Table 2.19. UCFG Address    | Space                                 | 52  |

| Table 2.20. AHB-Lite Mast   | ter 0 Interface Port Descriptions     | 58  |

| Table 2.21. AHB-Lite Mast   | ter 1 Interface Port Descriptions     | 59  |

| Table 2.22. AHB-Lite Slave  | e Interface Port Descriptions         | 60  |

| Table 2.23. AHB-Lite Conf   | iguration Interface Port Descriptions | 61  |

| Table 2.24. APB Configura   | tion Interface Port Descriptions      | 63  |

| Table 2.25. AXI4-Stream N   | Master Interface Port Descriptions    | 64  |

| Table 2.26. AXI4-Stream S   | lave Interface Port Descriptions      | 65  |

| Table 2.27. DMA Interrupt   | t Interface Port Descriptions         | 65  |

|                             | Attribute Descriptions                |     |

| Table 2.29. CSR Values V f  | for EP and RP Applications            | 77  |

| Table 2.30. Type 00 Config  | guration Header                       |     |

| Table 2.31. Type 01 Config  | guration Header                       |     |

| Table 2.32. Capability and  | l Extended Capability Items           |     |

| Table 2.33. Type 00 Config  | guration Registers                    |     |

| Table 2.34. PCI Express Ca  | apability                             |     |

| Table 2.35. Power Manage    | ement Capability                      |     |

| Table 2.36. MSI-X Capabili  | ity                                   |     |

|                             | l                                     |     |

| Table 2.38. Advanced Erro   | or Reporting Extended Capability      |     |

| Table 2.39. ARI Extended    | Capability                            |     |

| Table 2.40. Vendor-Specif   | ic Extended Capability                |     |

| Table 2.41. Secondary PCI   | I Express Extended Capability         |     |

| Table 2.42. ATS Extended    | Capability                            |     |

| Table 2.43. DSN Extended    | l Capability                          |     |

| Table 2.44. Resizable BAR   | Capability                            |     |

|                             | ing Capability                        |     |

|                             | er Allocation (DPA) Capability        |     |

|                             | tes Extended Capability               |     |

|                             | ance Reporting (LTR) Capability       |     |

| Table 4.1. Resource Utiliza | ation                                 | 230 |

# Acronyms in This Document

| A list of acrony | ms used in this document. |

|------------------|---------------------------|

|------------------|---------------------------|

| Acronym | Definition                                |

|---------|-------------------------------------------|

| APB     | Advanced Peripheral Bus                   |

| AHB     | Advanced High-Performance Bus             |

| AXI     | Advanced Extensible Interface             |

| ASPM    | Active State Power Management             |

| BAR     | Base Address Register                     |

| DLLP    | Data Link Layer Packet                    |

| DMA     | Direct Memory Access                      |

| EP      | Endpoint                                  |

| FIFO    | First In First Out                        |

| LMMI    | Lattice Memory Mapped Interface           |

| LTSSM   | Link Training and Status State Machine    |

| MSI     | Message Signaled Interrupt                |

| RTL     | Register Transfer Language                |

| PCIE    | Peripheral Component Interconnect Express |

| PCS     | Physical Coding Sublayer                  |

| PMA     | Physical Medium Attachment                |

| PM      | Power Mangagement                         |

| RC      | Root Complex                              |

| RP      | Root Port                                 |

| TLP     | Transaction Layer Packet                  |

| UCFG    | User Configuration Interface              |

# 1. Introduction

PCI Express is a high performance, fully scalable, well defined standard for a wide variety of computing and communications platforms. Being a packet based serial technology, PCI Express greatly reduces the number of required pins and simplifies board routing and manufacturing. PCI Express is a point-to-point technology, as opposed to the multi-drop bus in PCI. Each PCI Express device has the advantage of full duplex communication with its link partner to greatly increase overall system bandwidth. The basic data rate for a single lane is double that of the 32 bit/33 MHz PCI bus. A four lane link has eight times the data rate in each direction of a conventional bus.

The Lattice PCIe X1 Core provides a flexible, high-performance, easy-to-use Transaction Layer Interface to the PCI Express<sup>®</sup> Bus. The Lattice PCIe X1 Core implementation is a hardened IP with soft logic provided for interface conversion options. The hardened IP is an integration of PHY and Link Layer blocks from third party vendors (Analog Bits Inc., and Northwest Logic Inc.). Throughout this document, the Link Layer block refers to the entire logical block that consists of three sub layers namely, PHY logical layer (that is, LTSSM, PIPE, and other related function), Data Link Layer, and Transaction Layer. The PHY block refers to the PMA and PCS.

The Lattice PCIe X1 IP Core is supported in CrossLink<sup>™</sup>-NX and Certus<sup>™</sup>-NX FPGA device families and is available in Lattice Radiant<sup>™</sup> Software.

## 1.1. Quick Facts

Table 1.1 provides quick facts about the Lattice PCIe X1 IP core.

| IP Requirements             | Supported FPGA Families   | CrossLink-NX, Certus-NX                                                             |

|-----------------------------|---------------------------|-------------------------------------------------------------------------------------|

|                             | Targeted Devices          | LIFCL-40, LFD2NX-40                                                                 |

| <b>Resource Utilization</b> | Supported User Interfaces | APB, AHB-Lite, AXI4-Stream                                                          |

|                             | Resources                 | See Table 4.1.                                                                      |

|                             | Lattice Implementation    | IP Core v1.1.x –Lattice Radiant Software 2.1                                        |

|                             | Synthesis                 | Lattice Synthesis Engine                                                            |

| Design Tool Support         |                           | Synopsys <sup>®</sup> Synplify Pro <sup>®</sup> for Lattice                         |

|                             | Simulation                | For a list of supported simulators, see the Lattice Radiant<br>Software User Guide. |

## Table 1.1. Lattice PCIe X1 IP Core Quick Facts

## 1.2. Features

Hard IP PHY Key features include:

- Transmitter

- Configurable driver impedance, amplitude and 3-tap pre-emphasis

- Receiver

- Configurable receiver impedance, Continuous Time Linear Equalizer (CTLE)gain, 1-Tap Decision Feedback Equalization (DFE), and support for equalizer adaptation.

- Baud rate Eye Monitoring capability to map eye density at receiver post equalization

- Bit skip feature to allow for adjusting received byte clock alignment

- PCS

- Rate negotiation support

- Selectable parallel data widths such as 5, 10 and 16

- 8b/10b encoding at 2.5 Gbps and 5 Gbps

- Test support features such as near-end loopback, PLL bypass modes, etc.

- Protocol-compatible features such as LOS, squelch, power modes, etc

- L1-substates and Special L1P2 support for PCIe2.0

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

Hard IP Link Layer Key features include:

- PCI Express<sup>™</sup> Base Specification Revision 3.0 compliant including compliance with earlier PCI Express Specifications.

- Backward compatible with PCI Express 2.x, 1.x

- x1 PCI Express Lane only

- 5.0 GT/s, and 2.5 GT/s line rate support

- Comprehensive application support:

- Endpoint

- Root Port

- Multi-Function support with 1-4 Physical Functions

- ECC RAM and Parity Data Path Protection

- 32-bit Core Data Width

- Complete error-handling support

- AER, ECRC generation/checking, recovery from Parity and ECC errors

- Supports detection of numerous optional errors, embedded simulation error checks/assertions

- Simulation and hardware error injection features enable error testing

- Flexible core options allow for design complexity/feature tradeoffs:

- Configurable Receive, Transmit, and Replay Buffer sizes

- Supports Polarity Inversion, Up/Down-configure, Autonomous Link Width/Speed changes

- Power Management

- Supports L1, ASPM L0s, & ASPM L1

- L1 PM Substates with CLKREQ

- Power Budgeting

- Dynamic Power Allocation

- Latency Tolerance Reporting

- Implements Type 0 Configuration Registers in Endpoint Mode

- Implements Type 1 Configuration Registers in Root Port Mode

- Complete Root Port Configuration Register implementation

- Dual mode design supports EP or RP via register changes

- Easy to use

- Decodes received packets to provide key routing information (BAR hits, Tag, and others.)

- Implements all aspects of the required PCIe Configuration Space

- Optionally consumes PCI Express Message TLPs or leaves them in band

- Interfaces have consistent timing and function over all modes of operation

- Provides a wealth of diagnostic information for superior system-level debug and link monitoring

- Implements all 3 PCI Express Layers (Transaction, Data Link, Physical)

Soft IP features include:

- AHB-Lite Data Interface Option

- AHB-Lite Data Interface Option with DMA support

- AXI4-Stream Data Interface Option

- APB Register Interface Option

- AHB-Lite Register Interface Option

## 1.3. Conventions

## 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- \_*o* are output signals

# 2. Functional Description

## 2.1. Overview

## 2.1.1. Block Diagram

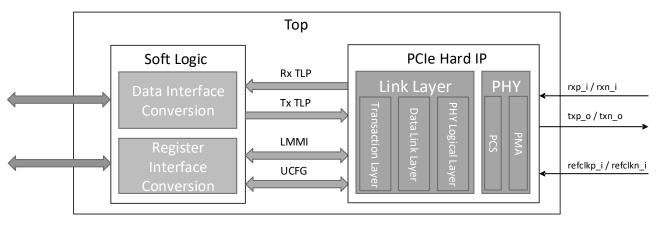

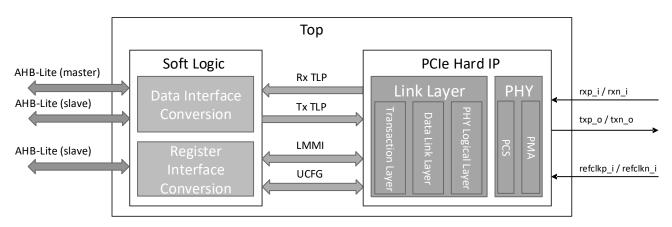

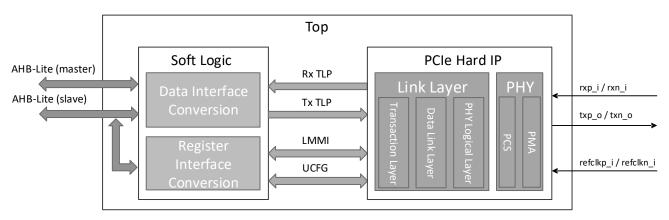

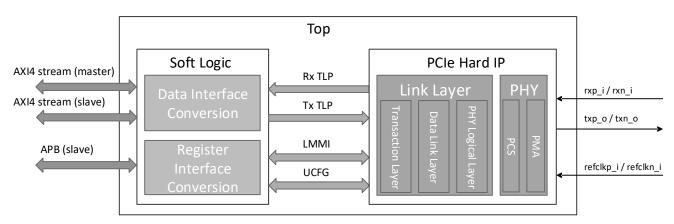

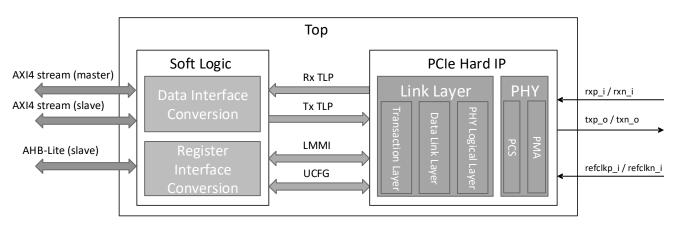

Figure 2.1. Lattice PCIe X1 Core Block Diagram

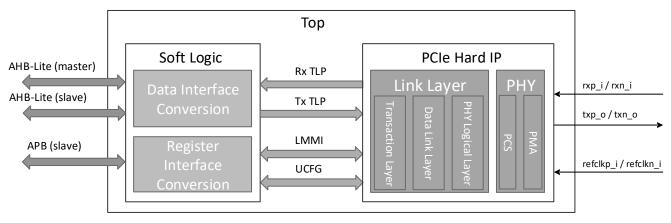

The Lattice PCIe X1 Core implements all three layers defined by the PCI Express Specification: Physical, Data Link, and Transaction. A soft logic is provided for optional interface conversion such as AHB-Lite, AXI4-stream, and APB. Details of the optional interface conversion are discussed in the section 2.1.10 and 0.

The Lattice PCIe X1 Core Hard IP implementation integrates the Northwest Logic's Expresso Core (Link Layer), and AnalogBits' PMA and PCS Core (PHY).

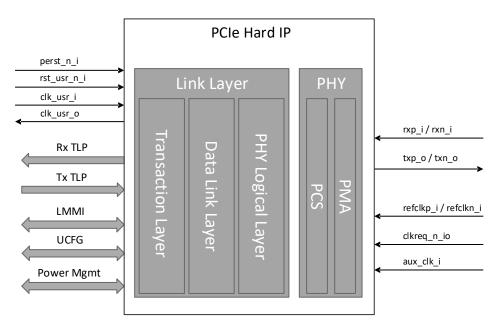

The Lattice PCIe X1 Hard IP has the following interfaces as shown in Figure 2.2. The details of each interface are discussed in the succeeding sections.

#### Figure 2.2. Lattice PCIe X1 Core Hard IP

- Clock and Reset Interface

- The user domain interface can be clocked using the PHY PCLK output (clk\_usr\_i=clk\_usr\_o) or by user generated clock. The fundamental reset (perst\_n\_i) resets the core (PHY and Link layer blocks) except for the core configuration registers. Another reset (rst\_usr\_n\_i) is provided to reset only the Link layer block.

- PHY Interface

- High Speed Serial Interface supports maximum rate of 5GTs

- TLP Receive Interface

- Receive TLPs from the PCIe link partner

- High bandwidth interface

- TLP Transmit Interface

- Transmit TLPs to the PCIe link partner

- High bandwidth interface

- Power Management Interface

- Ports for implementing power management capabilities

- UCFG User Configuration Space Register Interface

- Enables customers to access the PCIe Configuration Space Registers

- LMMI Configuration and Status Register (CSR) Interface

- This interface is used to write and read the Core configuration and status registers. A typical customer application requires changing only a small number of the default values such as Vendor ID, Device ID, and BAR configuration.

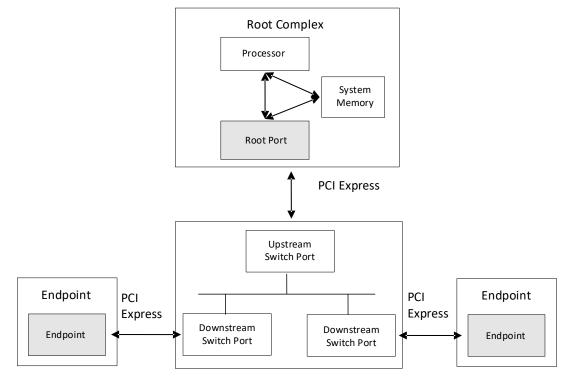

## 2.1.2. Endpoint/Root Port Configurations

The Lattice PCIe X1 Core supports Endpoint and Root Port applications:

- Endpoint

- PCI Express Interface for an I/O device (network/storage/data capture/etc.)

- Root Port

- Implements the top node of a PCI Express hierarchy; part of the Root Complex

- For use with an embedded processor running an Operating System

Root Port operation is detailed in Section 2.1.6.

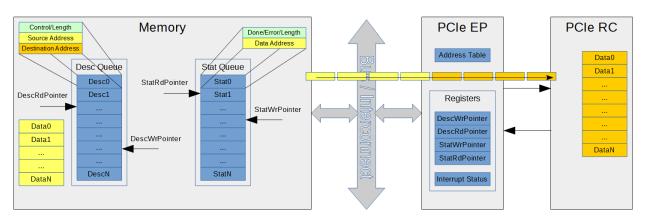

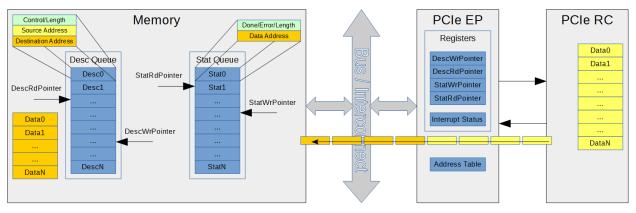

The different applications supported by the Lattice PCIe X1 Core (gray blocks) are shown in Figure 2.3.

Figure 2.3. Endpoint and Root Port Applications

## 2.1.3. ECC and Parity Data Path Protection

The Lattice PCIe X1 Core protects the TLP data path with ECC and Parity Protection. This is implemented in the Hard IP block.

ECC is used to protect TLP data in the following data path RAMs:

- Replay Buffer

- Receive Buffer

- Transmit Buffer

The ECC implementation enables correction for 1-bit errors and detection for 2-bit errors. 8-bits of ECC information are included in the RAMs for each 64 (or fraction thereof) data bits.

Even (XOR) Parity (parity[i] =  $^(data[((i+1)*8)-1:(i*8)])$  is used to protect the data path. Parity provides detection for 1bit errors (and other odd-bit errors). To enable continuous parity protection coverage, parity is passed through RAMs that are also protected by ECC.

For the receive data path, parity is generated for received TLPs prior to the removal and validation of the Link CRC (LCRC). Parity protection is thus overlapped with LCRC protection. Received TLP parity is passed with the associated received TLP (header and payload) bytes through the Receive Buffer and onto the user Transaction Layer Receive Interface. It is expected that parity is checked, and errors are handled, by the ultimate TLP consumer. Because TLP can have parity errors on any byte (toward the end of a longer TLP for instance), it is generally not possible to avoid processing the error TLP because the earlier portion of the TLP may already have been processed by the time that the error is detected. Applications that don't want to process TLPs with errors need to store and forward the TLP for processing only after inspecting the parity of all data bytes. If the core Transaction Layer detects a parity error while it is consuming a received TLP (Type 0 Configuration Read/Write, Malformed TLP, Message, etc.), the error is reported as an Uncorrectable Error (in AER capability) and the core discards the TLP without processing it.

For the transmit data path, parity is generated by the TLP source. For user TLPs (for example those transmitted on the core's Transaction Layer Transmit Interface), you provded parity along with the associated TLP (header and payload) bytes. The provided parity is kept with the associated data as it traverses the core. The parity is checked and discarded just after the TLP PCIe LCRC is generated. Parity protection is thus overlapped with LCRC protection including

the associated PCIe replay mechanism. If the core detects a parity or uncorrectable ECC error during transmission of a TLP, the error is reported and the associated TLP is nullified (discarded) and not retransmitted. This is a serious error that must be handled by software. The TLP is discarded in order to not propagate the error and risk potential worse consequences in other components that would receive a TLP with known bit errors.

The core includes the ability to enable/disable the reporting and handling of ECC/Parity errors. Correctable errors (ECC 1-bit errors) are fixed when correction is enabled. Uncorrectable ECC/Parity errors in the transmit data path result in the associated TLP being discarded/nullified when error handling is enabled. While error handling can be disabled, this is not recommended as passing a known TLP with bad contents can result in a more serious error condition than discarding the TLP.

## 2.1.3.1. Uncorrectable Error Recovery

PCI Express includes the ability to nullify (cancel) a TLP transmission immediately after it finishes by inverting the LCRC and using End Bad (EDB) end framing instead of the normal TLP end framing. TLP may be desired to be nullified to reduce propagation, and potentially multiplying, the affects of the error. Nullified TLPs are generally not regenerated by the original TLP source (it is difficult for software to construct the missing TLP), so a fatal system error condition generally results whether the error TLP is nullified or not. When TLP are nullified due to errors, the core attempts to keep the transmit stream active so that software can be notified of the error using the standard in-band mechanisms (transmission of ERR\_NFAT or ERR\_FAT message for example).

TLPs are allocated a Sequence Number during transmission and the PCIe receiver only accepts TLPs in sequence order. When a TLP is nullified due to an uncorrectable error, the missing sequence number must be recovered, before the link can continue to transmit TLPs.

TLPs are allocated Virtual Channel Flow Control Credits when they are transmitted by the Transaction Layer. The PCI Express device receiving the TLP over the PCI Express link, frees the associated credits by sending Flow Control Update DLLPs. TLPs which are nullified due to uncorrectable ECC and Parity errors have been allocated credits by the Transaction Layer, which is never freed since the TLP is nullified and is not received by the Receiver (nullified TLP are discarded by the Receiver without affecting Flow Control Credits or Sequence Number).

Whenever a transmitted TLP is nullified due to an uncorrectable error, this causes the PCI Express link to be unable to process further TLPs. The sequence number and flow control credits that were allocated to the nullified TLP must be reclaimed before the link is repaired. The Lattice PCIe X1 Core contains logic to correct the link when TLPs are nullified due to uncorrectable errors.

Whenever an uncorrectable ECC or Parity error is detected, even when the link has been corrected for further transmission, it is recommended for software to cause the link to be reset. The TLP(s) which are discarded, due to uncorrectable errors, compromise the application and the application is typically unable to recover.

## 2.1.4. LTSSM State Definitions

## 2.1.4.1. Main LTSSM

The Lattice PCIe X1 Core follows the PCI Express specification for the Link Training and Status State Machine. However, to help hit higher frequencies the LTSSM is split into one Major State LTSSM state machine and several separate LTSSM sub-state machines with one sub-state state machine for each major state.

The Lattice PCIe X1 Core implements additional LTSSM sub-states that are necessary to meet PCIe Spec. LTSSM operation, but are not given an explicit sub-state in the PCI Express specification. Table 2.1 provides information about each state machine state

| LTSSM Major State | LTSSM Sub-state           | DESCRIPTION                                                                                                                                                                       |

|-------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 – Detect        | 0 – DETECT_INACTIVE       | The sub-state is "DETECT_INACTIVE" whenever the LTSSM Major State is not Detect.                                                                                                  |

|                   | 1 – DETECT_QUIET          | Detect.Quiet                                                                                                                                                                      |

|                   | 2 – DETECT_SPD_CHG0       | Detect.Quiet – Sub-state to change speed change back to 2.5G if needed – request PHY speed change                                                                                 |

|                   | 3 – DETECT_SPD_CHG1       | Detect.Quiet – Sub-state to change speed change back to 2.5G if needed – wait for speed change to complete                                                                        |

|                   | 4 – DETECT_ACTIVE0        | Detect.Active – First Rx Detection                                                                                                                                                |

|                   | 5 – DETECT_ACTIVE1        | Detect.Active – Wait 12mS between Rx Detection attempts                                                                                                                           |

|                   | 6 – DETECT_ACTIVE2        | Detect.Active – Second Rx Detection (if needed)                                                                                                                                   |

|                   | 7 – DETECT_P1_TO_P0       | Detect.Active – Change PHY power state from P1 to P0 (inactive to active) if needed (ie. on Detect->Polling transition).                                                          |

|                   | 8 – DETECT_P0_TO_P1_0     | Change PHY power state from P0 to P1 (active to inactive) –<br>Transmit Electrical Idle Ordered Sets to notify the link partner<br>that we are going idle                         |

|                   | 9 – DETECT_P0_TO_P1_1     | Change PHY power state from P0 to P1 – Wait for TX Electrical<br>Idle Ordered Set transit request made in<br>DETECT_P0_T0_P1_0 to get transmitted at the output of the<br>core    |

|                   | 10 - DETECT_P0_T0_P1_2    | Change PHY power state from P0 to P1 – Wait for PHY to reach P1 state before continuing                                                                                           |

| 1 – Polling       | 0 – POLLING_INACTIVE      | The sub-state is "POLLING_INACTIVE" whenever the LTSSM<br>Major State is not Polling.                                                                                             |

|                   | 1 – POLLING_ACTIVE_ENTRY  | Polling.Active – Entry to Polling.Active – State exists because in some cases the LTSSM must exit Polling without Tx of TS OS.                                                    |

|                   | 2 – POLLING_ACTIVE        | Polling.Active                                                                                                                                                                    |

|                   | 3 – POLLING_CFG           | Polling.Configuration                                                                                                                                                             |

|                   | 4 – POLLING_COMP          | Polling.Compliance – Transmitting compliance pattern.                                                                                                                             |

|                   | 5 – POLLING_COMP_ENTRY    | Polling.Compliance entry state – directs a speed change via<br>POLLING_COMP_EIOS, POLLING_COMP_EIOS_ACK, and<br>POLLING_COMP_IDLE when necessary before going to<br>POLLING_COMP. |

|                   | 6 – POLLING_COMP_EIOS     | Polling.Compliance – Transmit Electrical Idle Ordered Sets to notify the link partner that we are going idle                                                                      |

|                   | 7 – POLLING_COMP_EIOS_ACK | Polling.Compliance – Wait for the Electrical Idle Ordered Sets transmitted in POLLING_COMP_EIOS to exit the core                                                                  |

|                   | 8 – POLLING_COMP_IDLE     | Polling.Compliance – Perform speed change now that link is idle.                                                                                                                  |

#### Table 2.1. LTSSM State Definitions

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| LTSSM Major State | LTSSM Sub-state                | DESCRIPTION                                                                                                                                                                                                       |

|-------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 – Configuration | 0 - CONFIGURATION_INACTIVE     | The sub-state is "CONFIGURATION_INACTIVE" whenever the LTSSM Major State is not Configuration.                                                                                                                    |

|                   | 1 – CONFIGURATION_US_LW_START  | Acting as Upstream Port – Configuration.Linkwidth.Start                                                                                                                                                           |

|                   | 2 – CONFIGURATION_US_LW_ACCEPT | Acting as Upstream Port -Configuration.Linkwidth.Accept                                                                                                                                                           |

|                   | 3 – CONFIGURATION_US_LN_WAIT   | Acting as Upstream Port -Configuration.Lanenum.Wait                                                                                                                                                               |

|                   | 4 – CONFIGURATION_US_LN_ACCEPT | Acting as Upstream Port -Configuration.Lanenum.Accept                                                                                                                                                             |

|                   | 5 – CONFIGURATION_DS_LW_START  | Acting as Downstream Port -Configuration.Linkwidth.Start                                                                                                                                                          |

|                   | 6 – CONFIGURATION_DS_LW_ACCEPT | Acting as Downstream Port -Configuration.Linkwidth.Accept                                                                                                                                                         |

|                   | 7 – CONFIGURATION_DS_LN_WAIT   | Acting as Downstream Port -Configuration.Lanenum.Wait                                                                                                                                                             |

|                   | 8 – CONFIGURATION_DS_LN_ACCEPT | Acting as Downstream Port -Configuration.Lanenum.Accept                                                                                                                                                           |

|                   | 9 – CONFIGURATION_COMPLETE     | Configuration.Complete                                                                                                                                                                                            |

|                   | 10 - CONFIGURATION_IDLE        | Configuration.Idle                                                                                                                                                                                                |

| 3 – LO            | 0 – L0_INACTIVE                | The sub-state is "LO_INACTIVE" whenever the LTSSM Major State is not LO.                                                                                                                                          |

|                   | 1 – L0_L0                      | L0 – Link is in L0                                                                                                                                                                                                |

|                   | 2 – LO_TX_EL_IDLE              | Tx_L0s.Entry, L1.Entry, or L2.Entry – Transmit Electrical Idle<br>Ordered Sets to notify the link partner that we are going idle –<br>i.e. for preparing to enter low power states such as Tx_L0s, L1,<br>and L2. |

|                   | 3 – L0_TX_IDLE_MIN             | Tx_L0s.Entry, L1.Entry, or L2.Entry – Guarantee the minimum<br>Tx Elec Idle time when entering electrical idle and also require<br>Rx EIOS to have been received when necessary.                                  |

| 4 – Recovery      | 0 – - RECOVERY_INACTIVE        | The sub-state is "RECOVERY_INACTIVE" whenever the LTSSM<br>Major State is not Recovery.                                                                                                                           |

|                   | 1 – RECOVERY_RCVR_LOCK         | Recovery.RcvrLock                                                                                                                                                                                                 |

|                   | 2 – RECOVERY_RCVR_CFG          | Recovery.RcvrCfg                                                                                                                                                                                                  |

|                   | 3 – RECOVERY_IDLE              | Recovery.Idle                                                                                                                                                                                                     |

|                   | 4 – RECOVERY_SPEED0            | Recovery.Speed – Transmit Electrical Idle Ordered Sets to notify the link partner that we are going idle                                                                                                          |

|                   | 5 – RECOVERY_SPEED1            | Recovery.Speed – Determine to which speed to change                                                                                                                                                               |

|                   | 6 – RECOVERY_SPEED2            | Recovery.Speed – Wait for remote device to enter electrical idle and remain there for required minimum time                                                                                                       |

|                   | 7 – RECOVERY_SPEED3            | Recovery.Speed – Request PHY change speed and wait for PHY to finish changing speed                                                                                                                               |

| 5 – Disable       | 0 – DISABLE_INACTIVE           | The sub-state is "DISABLE_INACTIVE" whenever the LTSSM Major State is not Disable.                                                                                                                                |

|                   | 1 – DISABLEO                   | Disable – Transmit 16 to 32 TS1 Ordered Sets w/ Disable Link bit asserted                                                                                                                                         |

|                   | 2 – DISABLE1                   | Disable – Transition to Electrical Idle                                                                                                                                                                           |

|                   | 3 – DISABLE2                   | Disable – Wait to receive an Electrical Idle Ordered Set and min time of TX_IDLE_MIN afterwards                                                                                                                   |

|                   | 4 – DISABLE3                   | Disable – Wait until a Disable exit condition occurs.                                                                                                                                                             |

| LTSSM Major State | LTSSM Sub-state           | DESCRIPTION                                                                                                                                                                     |

|-------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 – Loopback      | 0 – LOOPBACK_INACTIVE     | The sub-state is "LOOPBACK_INACTIVE" whenever the LTSSM Major State is not Loopback.                                                                                            |

|                   | 1 – LOOPBACK_ENTRY        | Loopback.Entry – Loopback entry state – Loopback Master may<br>be required to Tx Loopback TS OS before continuing or speed<br>may need to be changed before beginning loopback. |

|                   | 2 – LOOPBACK_ENTRY_EXIT   | Loopback.Entry – Prepare to enter Loopback.Active                                                                                                                               |

|                   | 3 – LOOPBACK_EIOS         | Loopback.Entry – Transmit Electrical Idle Ordered Sets to<br>notify the link partner that we are going idle (to change speed)                                                   |

|                   | 4 – LOOPBACK_EIOS_ACK     | Loopback.Entry – Wait for the Electrical Idle Ordered Sets transmitted in LOOPBACK_EIOS to exit the core                                                                        |

|                   | 5 – LOOPBACK_IDLE         | Loopback.Entry – Stay in Electrical Idle for required minimum time.                                                                                                             |

|                   | 6 – LOOPBACK_ACTIVE       | Loopback.Active                                                                                                                                                                 |

|                   | 7 – LOOPBACK_EXITO        | Loopback.Exit – Tx Electrical Idle                                                                                                                                              |

|                   | 8 – LOOPBACK_EXIT1        | Loopback.Exit – Stay in Electrical Idle for required minimum time.                                                                                                              |

| 7 – Hot Reset     | 0 – HOT_RESET_INACTIVE    | The sub-state is "HOT_RESET_INACTIVE" whenever the LTSSM Major State is not Hot Reset.                                                                                          |

|                   | 1 – HOT_RESET_HOT_RESET   | Hot Reset – as Slave                                                                                                                                                            |

|                   | 2 – HOT_RESET_MASTER_UP   | Hot Reset – as Master with Link Up                                                                                                                                              |

|                   | 3 – HOT_RESET_MASTER_DOWN | Hot Reset – as Master with Link Down                                                                                                                                            |

| 8 – TX LOs        | 0 – TX_LOS_INACTIVE       | The sub-state is "TX_LOS_INACTIVE" whenever the LTSSM Major State is not TX LOs.                                                                                                |

|                   | 1 – TX_LOS_IDLE           | Tx_L0s.Idle – Idle                                                                                                                                                              |

|                   | 2 – TX_LOS_TO_LO          | Tx_L0s.Idle – Exiting TX L0s; wait for PHY to indicate exit from L0s complete                                                                                                   |

|                   | 3 – TX_LOS_FTSO           | Tx_L0s.FTS – Transmit requested NFTS                                                                                                                                            |

|                   | 4 – TX_LOS_FTS1           | Tx_L0s.FTS – Transmit additional FTS required by Cfg Register<br>Extended Sync                                                                                                  |

| 9 – L1            | 0 – L1_INACTIVE           | The sub-state is "L1_INACTIVE" whenever the LTSSM Major State is not L1.                                                                                                        |

|                   | 1 – L1_IDLE               | L1.Idle                                                                                                                                                                         |

|                   | 2 – L1_SUBSTATE           | L1.1 or L1.2 depending upon higher level Power Management State Machine control.                                                                                                |

|                   | 3 - L1_TO_L0              | L1.Idle – Exiting L1; wait for PHY to indicate exit from L1 complete                                                                                                            |

| 10 – L2           | 0 – L2_INACTIVE           | The sub-state is "L2_INACTIVE" whenever the LTSSM Major<br>State is not L2.                                                                                                     |

|                   | 1 – L2_IDLE               | L2.Idle – Idle                                                                                                                                                                  |

|                   | 2 – L2_TX_WAKE0           | L2.TransmitWake – Transmit a Beacon until remote device exits electrical idle                                                                                                   |

|                   | 3 – L2_TX_WAKE1           | L2.TransmitWake – Assert Tx Electrical Idle before changing power state to P1                                                                                                   |

|                   | 4 – L2_EXIT               | L2.Idle – L2 exit; wait until PHY finishes power change out of L2                                                                                                               |

|                   | 5 – L2_SPEED              | L2.Idle – Change speed if required before going to L2                                                                                                                           |

## 2.1.4.2. RX LOs State Machine

The Rx\_LOs State Machine follows the LOs state of the receiver. The Rx\_LOs State Machine operates independently of the main LTSSM which controls the state of the transmitter.

| LTSSM Sub-state  | Description                                                                                     |  |

|------------------|-------------------------------------------------------------------------------------------------|--|

| 0 – RX_LOS_LO    | The sub-state is "RX_LOS_LO" whenever the receiver is in LO (ie. not en route to or in Rx LOs). |  |

| 1 – RX_LOS_ENTRY | Rx_LOs.Entry                                                                                    |  |

| 2 – RX_LOS_IDLE  | Rx_LOs.Idle                                                                                     |  |

| 3 – RX_LOS_FTS   | Rx_LOs.FTS                                                                                      |  |

| 4 – RX_LOS_REC   | Rx_L0s.FTS – Wait until LTSSM Major State == Recovery due to Rx L0s exit error                  |  |

### Table 2.2. Single-Ended I/O Standards

## 2.1.5. Multi-Function Support

The Lattice PCIe X1 Core supports 1-4 Functions. Multi-Function Support can only be enabled for Endpoints (functions implementing Type 0 Configuration Space). See the 2.4.1.5.1. function Register 0x8 for the register configuration.

When Multiple Function Support is present, each function is assigned a static Function Number starting at Function Number 0 and incrementing upwards. For ports that communicate function-specific information, port[0] applies to Function[0], port[1] applies to Function[1], etc. If a function is disabled, it does not affect the Function Number of the other enabled functions. Function[0] is always present and cannot be disabled.

## 2.1.6. Root Port Operation

The Lattice PCIe X1 Core is available in the following application configurations:

- Endpoint

- Root Port

## 2.1.6.1. Physical Layer Training

When operating as a Downstream Port (Root Port), the Lattice PCIe X1 Core trains as an upstream component (downstream port/lanes). When operating as an Upstream Port (Endpoint), the Lattice PCIe X1 Core trains as a downstream component (upstream port/lanes). Downstream port training and upstream port training are similar, but in some LTSSM states there are important differences in behavior. In a PCI Express link, the device closest to the Root Complex uses the downstream port training protocol and the other device uses the upstream port training protocol.

The direction of traffic which flows from the various Endpoints towards the Root Complex is called upstream traffic. The direction of traffic which flows in the direction from the Root Complex to the various Endpoints is called downstream traffic.

## 2.1.7. Root Port Configuration

In Root Port mode of operation, Type 1 rather than Type 0 Configuration Registers are implemented in the core.

When the core is operating as a Downstream Port (Root Port), Configuration requests are not permitted to be transmitted upstream and any received PCI Express Configuration Requests is treated as Unsupported Requests.

In Root Port configurations, the I/O, Memory, and Bus windows that are downstream of the Root Port are defined (in accordance with Type 1 Configuration Space) using the I/O Base, I/O Limit, Mem Base, Mem Limit, Prefetchable Mem Base, Prefetchable Mem Limit, Secondary Bus Number, and Subordinate Bus Number Configuration Registers.

When operating as a Downstream Port (Root Port), the core accepts received transactions, which fall outside (and hence target resources which are upstream of the core) these windows and pass them onto the user Local Receive Interface. Transactions falling inside these windows are to devices downstream of the Root Port and considered Unsupprted Requests if received.

A window is disabled (indicating that there are no resources of this type downstream of the port) by programming a Base value that is greater than the Limit value.

## 2.1.7.1. Root Port PCI Configuration

Configuration of devices downstream of the Root Port should be done in accordance with standard PCI Configuration rules by using the Root Port Transmit Interfaces to transmit Configuration Write and Configuration Read requests and the Root Port Receive Interface to receive the resulting completions.

Configuring a PCI Express hierarchy is a complicated task that is best accomplished with a software routine rather than with dedicated hardware. See the PCI and PCI Express Specifications for details. Leveraging existing PCI configuration software is recommended whenever possible.

## 2.1.7.2. Root Port vc\_rx\_cmd\_data\_o Differences

When operating as a Root Port, the vc\_rx\_cmd\_data\_o port has a different meaning. Instead of conveying BAR hit information as in Endpoint Mode, these ports convey Type1 Configuration Space Window hit information:

Individual bits of vc\_rx\_cmd\_data\_o[12:0] carry the following meaning in Root Port configurations:

- Bits[12:10] Traffic Class of the packet (same as for Endpoint)

- Bit[9] Completion/Request indicator; when set indicates the packet is a Completion packet; when clear the packet is a I/O or Memory Request or Message; the remaining bits in this field are decoded differently for Completion versus Base Address Region hits. (similar as for Endpoint)

- Bits[8:0] : Completion packets (Bit[9] == 1)

- a. Bits[8] If (1) the completion targets the core's ID; if (0) the completion targets another device behind the core as determined by Secondary Bus Number and Subordinate Bus Number (new bit definition for Root Port mode)

- b. Bits[7:0] Tag; the Requestor Tag contained in the packet; use to route completions to the associated requestor logic (same as for Endpoint)

- Bits[8:0] : Base Address Region Packet (Bit[9] == 0)

- a. Bit[8] When (1), the packet is a "write" transaction; when (0), the packet is a "read" transaction (same as for Endpoint)

- b. Bit[7] When (1), the packet requires one or more Completion transactions as a response; otherwise is (0) (same as for Endpoint)

- c. Bit[6] (1) if the TLP targets the Expansion ROM Base Address region (same as for Endpoint)

- d. Bit[5] (1) if the TLP is a Type 1 Configuration Request targeting the Secondary Bus Number

- e. Bit[4] (1) if the TLP is a Memory Request (or Message routed by address) and the address hits the memory region specified by Prefetchable Mem Base and Prefetchable Mem Limit (BAR4 hit for Endpoint)

- f. Bit[3] (1) if the TLP is a Memory Request (or Message routed by address) and the address hits the memory region specified by Mem Base and Mem Limit (BAR3 hit for Endpoint)

- g. Bit[2] (1) if the TLP is an I/O Request and and the address hits the IO region specified by I/O Base and I/O Limit (BAR2 hit for Endpoint)

- h. Bit[1] (1) if the TLP is a Write or Read Request (or Message routed by address) that targets Base Address Region 1 (same as for Endpoint)

- i. Bit[0] (1) if the TLP is a Write or Read Request (or Message routed by address) that targets Base Address Region 0 (same as for Endpoint)

#### 2.1.7.3. Locked Transactions

The Lattice PCIe X1 Core does not support locked transactions in Root Port or Endpoint mode. Locked transactions are only required for legacy functions and their use is heavily discouraged by the PCI Express Specification due to the severe performance penalty of implementing locked transactions and the uncertainty as to whether locked transactions are supported by devices in the PCI Express hierarchy.

## 2.1.7.4. Power Management

The Lattice PCle X1 Core supports the L1 link state when operating as a Root Port.

The Power Management process for Root Port operation differs from the Endpoint Power Management process described in the Error Handling section wherein the core is acting as the system-side device rather than as the Endpoint.

### 2.1.7.4.1. Downstream Port L1 Entry and Exit

### 2.1.7.4.1.1. L1 Entry

Before L1 entry begins, operating system power management software informs the drivers of devices downstream of the core that the link goes to L1. The drivers should complete all outstanding transactions and save any necessary state information before allowing power management software put the link in L1.

Power management software initiates the process of putting the PCI Express link into L1 by writing to the Upstream Port's (Endpoint) Power State Configuration register to a D-state other than D0. A write of a non-D0 Power State value causes the Upstream Port to stop TLP transmissions, wait for all outstanding TLPs to be acknowledged, and to indicate its readiness to Enter L1 by transmitting PM\_ENTER\_L1 DLLPs.

When the Lattice PCIe X1 Core's Power Management State Machine, operating as a Downstream Port, receives PM\_ENTER\_L1 DLLPs, the core begins the process of transitioning the link to L1. The core stops TLP transmissions, waits for all outstanding TLPs to be acknowledged, and then transmits PM\_REQ\_ACK DLLPs in response to Upstream Port's PM\_ENTER\_L1 DLLPs to inform the Upstream Port that the Downstream Port is also ready for L1 entry. When the Upstream Port receives the core's PM\_REQ\_ACK DLLPs, the Upstream Port transmits 1 or 2 (depending on Link Speed) Electrical Idle ordered sets and transitions its transmitter to electrical idle. When the Power Management State Machine operating as aDownstream Port, detects the Upstream Port entering electrical idle, the core transmits 1 or 2 (depending on Link Speed) Electrical Idle ordered sets and transitions its transmitter to electrical idle. The link is now in the L1 link state. The PHYs of both devices are put into a low power state to conserve power. Main power, PCI Express reference clock, PHY clock, and core clock are all maintained.

## 2.1.7.4.1.2. L1 Exit

L1 exit begins when either the core or Upstream Port brings its PHY out of the low power state and exits electrical idle in order to transmit a TLP. The device that wants to transmit a TLP exits electrical idle and transitions to Recovery to retrain the link. The other device senses the remote device's exit from electrical idle, takes its PHY out of the low power state, takes its transmitter out of electrical idle, and also enters Recovery. During Recovery the link is retrained and the PHYs of both devices recover symbol lock. After successful Recovery, both devices transition back to L0 and resume normal operation including transmitting and receiving TLPs. Note that during a normal, successful L1 entry and exit, the core is not reset or powered down and retains all context information. The remote device normally also retains all context information. The Upstream Port's reset behavior in L1 is detected by its advertisement of the No\_Soft\_Reset Power Management Capability register. If the Upstream Port's No\_Soft\_Reset register == 1 then the Upstream Port is not reset by a L1 link transition. If No\_Soft\_Reset == 0, then the link is reset by a L1 link transition and the Upstream Port must be re-enumerated and initialized by the BIOS/OS before being accessed.

## 2.1.8. Error Handling

The Lattice PCIe X1 Core detects errors and implements the appropriate response, without user intervention, for most error types. In general, you only need to handle error detection and reporting for error types that the core does not have enough information to detect.

Table 2.3, Table 2.4, Table 2.5, and Table 2.6 list the PCI Express defined error types:

- The TYPE column defines the PCI Express defined error severity:

- COR Correctable

- NFAT Uncorrectable Non-Fatal

- FAT Uncorrectable Fatal

#### 2.1.8.1. General PCI Express Errors

#### Table 2.3. General PCI Express Error List

| Error                        | Туре |

|------------------------------|------|

| Corrected Internal Error     | COR  |

| Uncorrectable Internal Error | FAT  |

| Header Log Overflow          | COR  |

#### 2.1.8.2. Physical Layer Errors

#### Table 2.4. Physical Layer Error List

| Error          | Туре |

|----------------|------|

| Receiver Error | COR  |

#### 2.1.8.3. Data Link Layer Errors

#### Table 2.5. Data Link Layer Error List

| Error                          | Туре |

|--------------------------------|------|

| Bad TLP                        | COR  |

| Bad DLLP                       | COR  |

| Replay Timeout                 | COR  |

| REPLAY_NUM Rollover            | COR  |

| Data Link Layer Protocol Error | FAT  |

| Surprise Down                  | FAT  |

#### 2.1.8.4. Transaction Layer Errors

#### Table 2.6. Transaction Layer Error List

| Error                       | Туре |

|-----------------------------|------|

| Poisoned TLP Received       | NFAT |

| ECRC Check Failed           | NFAT |

| Unsupported Request         | NFAT |

| Completion Timeout          | NFAT |

| Completer Abort             | NFAT |

| Unexpected Completion       | NFAT |

| ACS Violation               | NFAT |

| MC Blocked TLP              | NFAT |

| AtomicOp Egress Blocked     | NFAT |

| Receiver Overflow           | FAT  |

| Flow Control Protocol Error | FAT  |

| Malformed TLP               | FAT  |

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 2.1.9. Power Management

The Lattice PCIe X1 Core supports L0, ASPM L0s,ASPM L1, L1 PM Substates, L1, and L3 link states. L0 (fully operational state) and L3 (off) support is always enabled. The remaining link states may be enabled/disabled via Core Configuration ports. If ASPM L0s, ASPM L1, L1 PM Substates, or L1 support is enabled, then the user design must configure the power management capabilities of the core, and for some link states, take additional action when link states are entered or exited. This section describes the recommended actions user logic should take to control and react to power management states ASPM L0s, ASPM L1, and L1.

The PCI Express Specification defines the following link states:

- L0 Active

- Powered

- Clock & PLLs active; core clock active

- All PCI Express Transactions and operations are enabled

- ASPM LOs Low resume latency, energy saving "standby" state

- Powered

- Clock & PLLs active; core clock active

- PHY transmitter in electrical idle

- Remote PHY receiver must re-establish symbol lock during LOs exit

- When LOs is enabled by power management software, the core autonomously enters LOs when the transmit side of the link is idle and exit LOs when there is pending information to transmit. Link management DLLPs are required to be transmitted periodically so when a link is otherwise idle, it still enters and exit LOs with regularity to transmit link management DLLPs.

- ASPM L1 Low resume latency, energy saving "standby" state

- Powered

- Clock & PLLs active; core clock active

- Significant portion of PHY powered down

- PHY transmitter in electrical idle

- PHY receiver in electrical idle

- Deeper power savings but longer resume time than ASPM LOs

- Remote and local PHY must re-establish symbol lock during L1 exit

- When ASPM L1 is enabled by power management software, the core autonomously negotiates L1 entry with the link partner after an extended period of link inactivity. The link autonomously returns to L0 when either device in the link has TLPs to transmit.

- L1 Higher latency, lower power "standby" state

- Powered

- Clock & PLLs active; core clock active

- Significant portion of PHY powered down

- PHY transmitter in electrical idle

- PHY receiver in electrical idle

- Remote and local PHY must re-establish symbol lock during L1 exit

- The L1 state is entered both under control of power management software

- L3 Off

- Main power off; auxiliary power off

- In this state all power is removed and the core, PHY, and user logic are all non-operational

- All state information is lost

#### 2.1.9.1. Configuring Core to Support Power Management

The Lattice PCIe X1 Core allows for user logic to implement a wide variety of power management functionality. Primarily, you advertise and control the design's power management capabilities through the use of core configuration ports.

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-IPUG-02091-1.3

## 2.1.9.2. LOs

The Lattice PCIe X1 Core supports Active State Power Management (APSM) LOs.

When LOs support is enabled, ASPM LOs TX Entry Time, the desired amount of time for TLP and DLLP transmissions to be idle before LOs TX is entered, is determined by mgmt\_ptl\_pm\_aspm\_lOs\_entry\_time.

The Number of NFTS sets required by the local PHY to recover symbol lock when exiting LOs is determined by mgmt\_tlb\_ltssm\_nfts\_nfts.

NFTS Timeout Extend, mgmt\_tlb\_ltssm\_nfts\_to\_extend, controls how long the core waits after the expected LOs exit time before directing the link to Recovery to recover from a failed LOs exit. Due to high latencies between a PHY's Rx Electrical Idle output and the associated Rx Data it is normally necessary to choose a relatively high NFTS and NFTS Timeout Extend. See mgmt\_tlb\_ltssm\_nfts\_to\_extend description for details.

The PCI Express Device Capabilities configuration register has the following LOs fields:

- Bits[8:6] Endpoint LOs Acceptable Latency From PCI Express Base Specification, Rev 2.1 section 7.8.3: "Acceptable total latency that an Endpoint can withstand due to the transition from LOs state to the LO state. It is essentially an indirect measure of the Endpoint's internal buffering. Power management software uses the reported LOs Acceptable Latency number to compare against the LOs exit latencies reported by all components comprising the data path from this Endpoint to the Root Complex Root Port to determine whether ASPM LOs entry can be used with no loss of performance." Note that the amount of buffering does not refer to Lattice PCIe X1 Core buffering, but rather to user application buffering. Users should set this field in accordance with how long a delay is acceptable for their application.

- 000 Maximum of 64 ns

- 001 Maximum of 128 ns

- 010 Maximum of 256 ns

- 011 Maximum of 512 ns

- 100 Maximum of 1 μs

- 101 Maximum of 2 μs

- 110 Maximum of 4 μs

- 111 No limit

- Non-Endpoints must hard wire this field to 000.

The PCI Express Link Capabilities configuration register has the following LOs fields:

- Bits[14:12] LOs Exit Latency Length of time required to complete transition from LOs to LO:

- 000 Less than 64 ns

- 001 64 ns to less than 128 ns

- 010 128 ns to less than 256 ns

- 011 256 ns to less than 512 ns

- 100 512 ns to less than 1 μs

- 101 1 μs to less than 2 μs

- 110 2 μs-4 μs

- 111 More than 4 μs

- Exit latencies may be significantly increased if the PCI Express reference clocks used by the two devices in the link are common or separate.

- Bits[11:10] Active State Power Management (ASPM) Support should be set to "01" or "11" if LOs support is enabled or "00" otherwise.

## 2.1.9.3. L1

The Lattice PCIe X1 Core supports both software controller L1 entry (via PowerState Configuration Register) and hardware-autonomous L1 entry (Active State Power Management (APSM) L1).

Software-controlled L1 flow for Upstream Ports (Endpoint) is as follows:

- Software initiates changing a link to L1 by writing the core's Power Management Capability: Power State Configuration Register to a value other than 00 == D0. Note that the component's Device driver participates in this process and must ensure that all traffic is idle before permitting the system to power down to L1.

- When the core detects a change of Power State to a non-D0 value, the core's power management state machine, which is responsible for the higher-level power management protocol, follows the following sequence:

- Block further TLP transmissions

- Wait for all in process TLPs to complete transmission

- Wait for the Replay Buffer to empty (all transmitted TLPs acknowledged)

- Core transmits PM\_ENTER\_L1 DLLPs until receiving a PM\_REQ\_ACK DLLP from remote device

- Core directs LTSSM state machine to L1

- When a TLP is pending or the LTTSM state machine indicates L1 state has been exited due to link partner activity, the core returns to L0

Software-controlled L1 flow for Downstream Ports (Root Port) is similar to above, but the Downstream Port core is following the Upstream Port's L1 request:

- Core receives PM\_ENTER\_L1 DLLP from Upstream Port

- Block further TLP transmissions

- Wait for all in process TLPs to complete transmission

- Wait for the Replay Buffer to empty (all transmitted TLPs acknowledged)

- Transmit PM\_REQ\_ACK DLLP to remote device until remote device idles its transmitter

- Core directs LTSSM state machine to L1

- When a TLP is pending or the LTTSM state machine indicates L1 state has been exited due to link partner activity, the core returns to L0

The PCI Express Device Capabilities configuration register has the following L1 fields:

- Bits[11:9] Endpoint L1 Acceptable Latency From PCI Express Base Specification, Rev 2.1 section 7.8.3: "This field indicates the acceptable latency that an Endpoint can withstand due to the transition from L1 state to the L0 state. It is essentially an indirect measure of the Endpoint's internal buffering. Power management software uses the reported L1 Acceptable Latency number to compare against the L1 Exit Latencies reported (see below) by all components comprising the data path from this Endpoint to the Root Complex Root Port to determine whether ASPM L1 entry can be used with no loss of performance." Note that the amount of buffering does not refer to Lattice PCIe X1 Core buffering, but rather to user application buffering. Users should set this field in accordance with how long a delay is acceptable for their application.

- 000 Maximum of 1 μs

- 001 Maximum of 2 μs

- 010 Maximum of 4 μs

- 011 Maximum of 8 μs

- 100 Maximum of 16 μs

- 101 Maximum of 32 μs

- 110 Maximum of 64 μs

- 111 No limit

- Non-Endpoints must hard wire this field to 000.

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

PCI Express Link Capabilities configuration register has the following L1 fields:

- Bits[17:15] L1 Exit Latency Length of time required to complete transition from L1 to L0:

- 000 Less than 1µs

- 001 1 μs to less than 2 μs

- $010 2 \mu s$  to less than  $4 \mu s$

- 011 4 μs to less than 8 μs

- $100 8 \ \mu s$  to less than 16  $\mu s$

- 101 16 μs to less than 32 μs

- 110 32 μs-64 μs

- 111 More than 64 μs

- Exit latencies may be significantly increased if the PCI Express reference clocks used by the two devices in the link are common or separate.

- Bits[11:10] Active State Power Management (ASPM) Support should be set to "10" or "11" if L1 support is enabled or "00" otherwise.

Hardware-autonomous L1 (ASPM L1) entry is initiated only by Upstream Ports (Endpoint). The core ASPM L1 functionality must be enabled and advertised in PCIe Link Capabilities and software must enable ASPM L1 support in order for the hardware-autonomous L1 to be able to be negotiated. When ASPM L1 support is present and enabled for an Upstream Port, the core requests that the link be directed to L1, using ASPM L1 protocol, whenever the link is idle (no TLP or ACK/NAK DLLPs are transmitted) for the configured idle period.

A Downstream Port (Root Port) receives ASPM L1 requests from the remote device and may choose to accept or rejct the request. The core accepts ASPM L1 requests when there are no TLP or ACK/NAK DLLP pending transmit and otherwise rejects the request.

## 2.1.10. PCIe X1 Core Buffers

The Lattice PCIe X1 Core contains three large RAM buffers:

- Transmit Buffer for transmitting TLPs

- Receive Buffer for receiving TLPs

- Replay Buffer for holding TLPs that were transmitted until positive acknowledgement of receipt is received

The size of the Transmit Buffer, Receive Buffer, and Replay Buffer and the size of the corresponding buffers in the remote PCI Express Device have a fundamental impact on the throughput performance of the PCI Express link.

To achieve the highest throughputs, the buffers for both devices in the PCI Express link must be large enough that they can still accept more data while the oldest data begins to be freed from the buffer. If a buffer is too small, then the link stalls until the buffer has enough space to continue. The buffers must be large enough to overcome the expected latencies or throughput is affected.

## 2.1.10.1. PCI Express Credits

Flow Control DLLPs communicate available buffer space in units of Header and Data Credits as defined in the PCI Express Specification. The amount of space required by a Header is 12-20 bytes or (3-5 DWORDs with 1 DWORD == 4 bytes). Each Header Credit represents the capability to store a maximum size packet header which includes all of the transaction control information (address, byte enables, requester ID, etc.) and an optional End to End CRC (ECRC). Each Data Credit represents 16 bytes (4 DWORDs) of data payload. A transaction cannot be transmitted unless there is at least 1 header credit and enough data credits for the packet payload available in the remote device's Receive Buffer.

Credits are further divided into three categories for each of the main types of traffic. There are Posted (memory write requests and messages), Non-Posted (all reads; Configuration and I/O writes), and Completion (responses to Non-Posted Requests) credit categories. Each type of traffic must obey PCI Express transaction ordering rules and is stored in its own buffer area.

The credit categories are annotated as:

- PH Posted Request Header Credits

- PD Posted Request Data Payload Credits

- NH Non-Posted Request Header Credits

- ND Non-Posted Request Data Payload Credits

- CH Completion Header Credits

- CD Completion Data Payload Credits

PCI Express is inherently high-latency due to the serial nature of the protocol (clock rate matching, lane-lane deskewing, etc.) and due to the latency induced by requiring packets to be fully received and robustly checked for errors before forwarding them for higher-level processing.