# 3 MHz, Synchronous TinyBoost<sup>®</sup> Regulator

### Description

The FAN4868 is a low–power boost regulator designed to provide a regulated 3.3 V output from a single cell Lithium or Li–Ion battery. Output voltage options are fixed at 3.3 V with a guaranteed maximum load current of 200 mA at  $V_{IN} = 2.3$  V and 300 mA at  $V_{IN} = 3.3$  V. Input current in Shutdown Mode is less than 1  $\mu$ A, which maximizes battery life.

Light–load PFM operation is automatic and "glitch–free". The regulator maintains output regulation at no–load with as low as  $37 \,\mu A$  quiescent current.

The combination of built-in power transistors, synchronous rectification, and low supply current make the FAN4868 ideal for battery powered applications.

The FAN4868 is available in 6-bump 0.4 mm pitch Wafer-Level Chip Scale Package (WLCSP).

#### Features

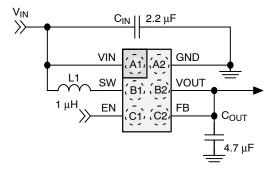

- Operates with Few External Components:

- $1\,\mu H$  Inductor and 0402 Case Size Input and Output Capacitors

- Input Voltage Range from 2.3 V to 3.2 V

- Fixed 3.3 V Output Voltage Options

- Maximum Load Current >150 mA at  $V_{IN}$  = 2.3 V

- Maximum Load Current 300 mA at  $V_{IN} = 2.7$  V,  $V_{OUT} = 3.3$  V

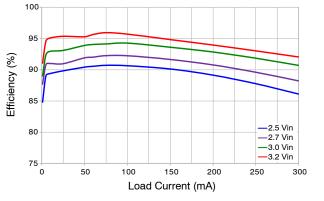

- Up to 92% Efficient

- Low Operating Quiescent Current

- True Load Disconnect During Shutdown

- Variable On-time Pulse Frequency Modulation (PFM) with Light-Load Power-Saving Mode

- Internal Synchronous Rectifier (No External Diode Needed)

- Thermal Shutdown and Overload Protection

- 6-Bump WLCSP, 0.4 mm Pitch

### Applications

- Powering 3.3 V Core Rails

- PDAs, Portable Media Players

- Cell Phones, Smart Phones, Portable Instruments

### **ON Semiconductor®**

www.onsemi.com

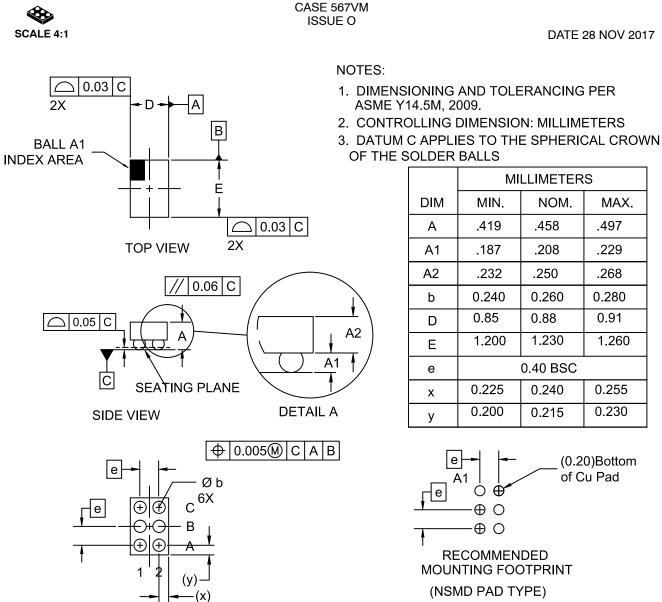

SCALE 4:1

WLCSP6 0.88 x 1.23 x 0.458 CASE 567VM

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

#### TYPICAL APPLICATION

#### Table 1. ORDERING INFORMATION

| Part Number  | Operating Temperature Range | Package             | Packing Method |

|--------------|-----------------------------|---------------------|----------------|

| FAN4868UC33X | −40°C to 85°C               | WLCSP, 0.4 mm Pitch | Tape and Reel  |

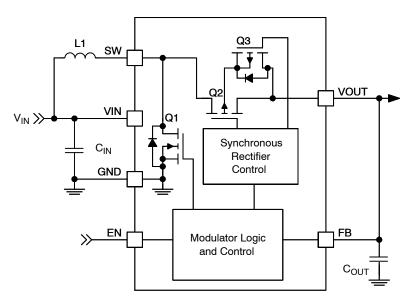

### **BLOCK DIAGRAMS**

Figure 1. IC Block Diagram

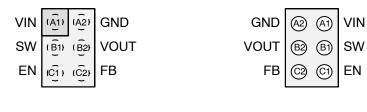

### **PIN CONFIGURATIONS**

Figure 2. WLCSP (Top View)

Figure 3. WLCSP (Bottom View)

#### Table 2. PIN DEFINITIONS

| Pin # |      |                                                                                                                  |

|-------|------|------------------------------------------------------------------------------------------------------------------|

| WLCSP | Name | Description                                                                                                      |

| A1    | VIN  | Input Voltage. Connect to Li-Ion battery input power source and input capacitor (CIN)                            |

| B1    | SW   | Switching Node. Connect to inductor                                                                              |

| C1    | EN   | Enable. When this pin is HIGH, the circuit is enabled. This pin should not be left floating                      |

| C2    | FB   | <b>Feedback</b> . Output voltage sense point for $V_{OUT}$ . Connect to output capacitor ( $C_{OUT}$ )           |

| B2    | VOUT | Output Voltage. This pin is both the output voltage terminal as well as an IC bias supply                        |

| A2    | GND  | <b>Ground</b> . Power and signal ground reference for the IC. All voltages are measured with respect to this pin |

#### Table 3. ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                |                                  |      | Max. | Units |

|------------------|------------------------------------------|----------------------------------|------|------|-------|

| V <sub>IN</sub>  | VIN                                      | VIN Pin                          |      |      | V     |

| V <sub>OUT</sub> | VOU                                      | T Pin                            | -2   | 6    | V     |

| $V_{FB}$         | FB                                       | FB Pin                           |      |      | V     |

| V <sub>SW</sub>  | SW Node                                  | DC                               | -0.3 | 5.5  | V     |

|                  |                                          | Transient: 10 ns, 3 MHz          | -1.0 | 6.5  |       |

| V <sub>EN</sub>  | EN                                       | EN Pin                           |      |      | V     |

| ESD              | Electrostatic Discharge Protection Level | Human Body Model per JESD22-A114 | 2    | 2    | kV    |

|                  | Charged Device Model per<br>JESD22-C101  |                                  |      | 1    |       |

| TJ               | Junction Temperature                     |                                  |      | +150 | °C    |

| T <sub>STG</sub> | Storage Temperature                      |                                  |      | +150 | °C    |

| ΤL               | Lead Soldering Temp                      | perature, 10 Seconds             |      | +260 | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### Table 4. RECOMMENDED OPERATING CONDITIONS

| Symbol           | Parameter      |                      | Min. | Max. | Units |

|------------------|----------------|----------------------|------|------|-------|

| V <sub>IN</sub>  | Supply Voltage | 3.3 V <sub>OUT</sub> | 2.3  | 3.2  | V     |

| I <sub>OUT</sub> | Output Current |                      |      | 200  | mA    |

| T <sub>A</sub>   | Ambient Te     | mperature            | -40  | +85  | °C    |

| TJ               | Junction Te    | emperature           | -40  | +125 | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Table 5. THERMAL PROPERTIES

| Symbol        | Parameter                              | Typical | Units |      |

|---------------|----------------------------------------|---------|-------|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance | WLCSP   | 130   | °C/W |

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperate T<sub>A</sub>.

#### **Table 6. ELECTRICAL SPECIFICATIONS**

Minimum and maximum values are at  $V_{IN} = V_{EN} = 2.3 \text{ V}$  to 4.5 V (2.5 to 3.2  $V_{IN}$  for 3.3  $V_{OUT}$  option),  $T_A = -40^{\circ}$ C to +85°C; circuit of Typical Application, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}$ C, and  $V_{IN} = V_{EN} = 2.7 \text{ V}$  for  $V_{OUT} = 3.3 \text{ V}$ .

| Symbol                | Paramet                                               | er                      | Conditions                                                                   | Min   | Тур   | Мах   | Units |

|-----------------------|-------------------------------------------------------|-------------------------|------------------------------------------------------------------------------|-------|-------|-------|-------|

| l <sub>IN</sub>       | VIN Input Current                                     | 3.3 V <sub>OUT</sub>    | Quiescent: $V_{IN}$ = 2.7 V, $I_{OUT}$ = 0, EN = $V_{IN}$                    |       | 50    | 65    | μA    |

|                       |                                                       |                         | Shutdown: EN = 0, V <sub>IN</sub> = 2.7 V                                    |       | 0.5   | 1.5   |       |

| I <sub>LK_OUT</sub>   | V <sub>OUT</sub> Leakage                              | Current                 | $V_{OUT} = 0, EN = 0, V_{IN} \ge 3 V$                                        |       | 10    |       | nA    |

| I <sub>LK_RVSR</sub>  | V <sub>OUT</sub> to V <sub>IN</sub> Rever             | se Leakage              | V <sub>OUT</sub> = 3.3 V, V <sub>IN</sub> = 3.0 V, EN = 0                    |       |       | 2.5   | μA    |

| V <sub>UVLO</sub>     | Under-Voltage                                         | Lockout                 | V <sub>IN</sub> Rising                                                       |       | 2.2   | 2.3   | V     |

| V <sub>UVLO_HYS</sub> | Under-Voltage<br>Hysteres                             |                         |                                                                              |       | 190   |       | mV    |

| V <sub>ENH</sub>      | Enable HIGH                                           | Voltage                 |                                                                              | 1.05  |       |       | V     |

| V <sub>ENL</sub>      | Enable LOW                                            | /oltage                 |                                                                              |       |       | 0.4   | V     |

| I <sub>LK_EN</sub>    | Enable Input Leak                                     | age Current             |                                                                              |       | 0.01  | 1.00  | μΑ    |

| V <sub>OUT</sub>      | Output Voltage<br>Accuracy<br>(Note 2)                | 3.3 V <sub>OUT</sub>    | $V_{IN}$ from 2.5 V to 3.2 V, $I_{OUT}{\leq}200$ mA                          | 3.17  | 3.33  | 3.41  | V     |

| v <sub>ref</sub>      | Reference Ac                                          | curacy                  | Referred to V <sub>OUT</sub> = 3.3 V                                         | 3.280 | 3.330 | 3.380 | V     |

| t <sub>OFF</sub>      | Off Time                                              | Э                       | V <sub>IN</sub> = 2.7 V, V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 200 mA | 240   | 290   | 350   | ns    |

| I <sub>OUT</sub>      | Maximum Output 3.3 V <sub>OUT</sub>                   | V <sub>IN</sub> = 2.5 V | 250                                                                          |       |       | mA    |       |

|                       | Current<br>(Note 2)                                   |                         | V <sub>IN</sub> = 2.7 V                                                      | 300   |       |       |       |

| I <sub>SW</sub>       | SW Peak Current<br>Limit                              | 3.3 V <sub>OUT</sub>    | V <sub>IN</sub> = 2.7 V, V <sub>OUT</sub> > V <sub>IN</sub>                  | 650   | 800   | 950   | mA    |

| I <sub>SS</sub>       | Soft–Start Input<br>Peak Current<br>Limit<br>(Note 3) | 3.3 V <sub>OUT</sub>    | V <sub>IN</sub> = 2.7 V, V <sub>OUT</sub> < V <sub>IN</sub>                  |       | 700   |       | mA    |

| t <sub>SS</sub>       | Soft-Start Time<br>(Note 4)                           | 3.3 V <sub>OUT</sub>    | V <sub>IN</sub> = 2.7 V, I <sub>OUT</sub> = 200 mA                           |       | 250   | 750   | μs    |

| R <sub>DS(ON)</sub>   | N-Channel Boo                                         | st Switch               | V <sub>IN</sub> = 3.6 V                                                      | 1     | 300   |       | mΩ    |

|                       | P-Channel Synd                                        | Rectifier               | V <sub>IN</sub> = 3.6 V                                                      | 1     | 400   |       | 1     |

| T <sub>TSD</sub>      | Thermal Shu                                           | tdown                   | I <sub>LOAD</sub> = 10 mA                                                    | 1     | 150   |       | °C    |

| T <sub>TSD_HYS</sub>  | Thermal Shutdowr                                      | n Hysteresis            |                                                                              |       | 30    |       | °C    |

I<sub>LOAD</sub> from 0 to I<sub>OUT</sub>, also includes load transient response. VOUT measured from mid-point of output voltage ripple. Effective capacitance of C<sub>OUT</sub> > 1.5 μF.

Guaranteed by design and characterization; not tested in production.

4. Elapsed time from rising EN until regulated  $V_{OUT}$ .

40

20

0

-20

-40

-60

-80

0

50

V<sub>OUT</sub> - 3.33 V (mV)

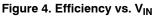

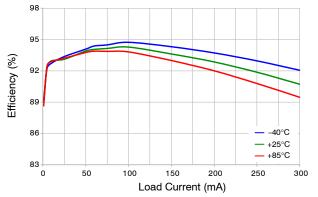

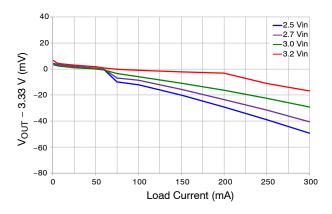

### 3.3 VOUT TYPICAL CHARACTERISTICS

Unless otherwise specified; circuit per Typical Application, 3.0 V<sub>IN</sub>, and  $T_A = 25^{\circ}C$ .

Figure 5. Efficiency vs. Temperature, 3.0 VIN

-40°C +25°C

- +85°C

Figure 6. Line and Load Regulation

Figure 7. Load Regulation vs. Temperature, 3.0 V<sub>IN</sub>

150

Load Current (mA)

200

250

300

100

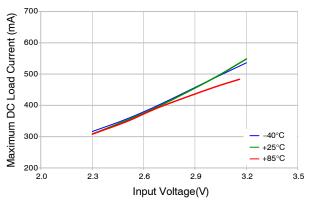

Figure 9. Maximum DC Load Current

## 3.3 VOUT TYPICAL CHARACTERISTICS (continued)

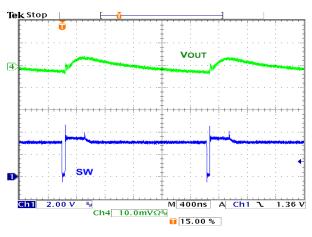

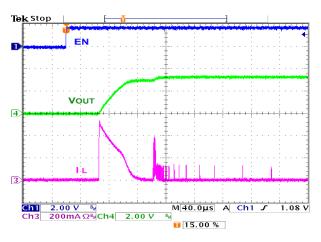

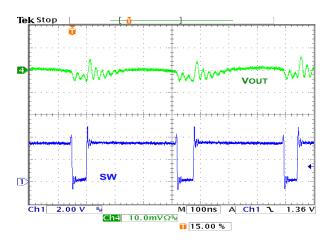

Unless otherwise specified; circuit per Typical Application, 3.0 V<sub>IN</sub>, and  $T_A = 25^{\circ}C$ .

Figure 10. Output Ripple, 10 mA PFM Load

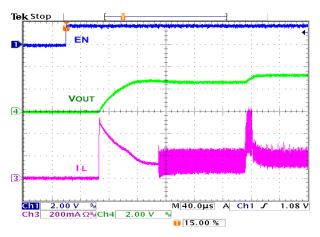

Figure 12. Startup, No Load

Figure 13. Startup, 22  $\Omega$  Load

#### FUNCTIONAL DESCRIPTION

#### **Circuit Description**

The FAN4868 is a synchronous boost regulator, typically operating at 3 MHz in Continuous Conduction Mode (CCM), which occurs at moderate to heavy load current and low  $V_{IN}$  voltages.

At light-load currents, the converter switches automatically to power-saving PFM Mode. The regulator automatically and smoothly transitions between quasi-fixed-frequency continuous conduction PWM Mode and variable-frequency PFM Mode to maintain the highest possible efficiency over the full range of load current and input voltage.

#### PWM Mode Regulation

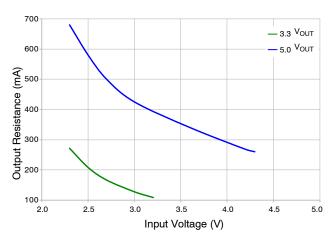

The FAN4868 uses a minimum on-time and computed minimum off-time to regulate  $V_{OUT}$ . The regulator achieves excellent transient response by employing current mode modulation. This technique causes the regulator output to exhibit a load line. During PWM Mode, the output voltage drops slightly as the input current rises. With a constant  $V_{IN}$ , this appears as a constant output resistance.

The "droop" caused by the output resistance when a load is applied allows the regulator to respond smoothly to load transients with negligible overshoot.

Figure 14. Output Resistance (ROUT)

When the regulator is in PWM CCM Mode and the target  $V_{OUT} = 5.05$  V,  $V_{OUT}$  is a function of  $I_{LOAD}$  and can be computed as:

$$V_{OUT} = 5.05 - R_{OUT} \times I_{LOAD}$$

(eq. 1)

For example, at  $V_{IN}$  = 3.3 V, and  $I_{LOAD}$  = 200 mA,  $V_{OUT}$  drops to:

$$V_{OUT} = 5.05 - 0.38 \times 0.2 = 4.974 \text{ V} \quad (eq. 1A)$$

At V<sub>IN</sub> = 2.3 V, and I<sub>LOAD</sub> = 200 mA, V<sub>OUT</sub> drops to:

$$V_{OUT} = 5.05 - 0.68 \times 0.2 = 4.914 \text{ V} \quad (eq. 1B)$$

#### **PFM Mode**

If  $V_{OUT} > V_{REF}$  when the minimum off-time has ended, the regulator enters PFM Mode. Boost pulses are inhibited until  $V_{OUT} < V_{REF}$ . The minimum on-time is increased to enable the output to pump up sufficiently with each PFM boost pulse. Therefore, the regulator behaves like a constant on-time regulator, with the bottom of its output voltage ripple at 5.05 V in PFM Mode.

| Table 7. | OPERATING | STATES |

|----------|-----------|--------|

|----------|-----------|--------|

| Mode | Description             | Invoked When:                       |

|------|-------------------------|-------------------------------------|

| LIN  | Linear Startup          | V <sub>IN</sub> > V <sub>OUT</sub>  |

| SS   | Boost Soft-Start        | V <sub>OUT</sub> < V <sub>REG</sub> |

| BST  | Boost Operating<br>Mode | V <sub>OUT</sub> = V <sub>REG</sub> |

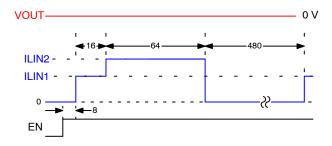

#### Shutdown and Startup

If EN is LOW, all bias circuits are off and the regulator is in Shutdown Mode. During shutdown, true load disconnect between battery and load prevents current flow from  $V_{IN}$  to  $V_{OUT}$ , as well as reverse flow from  $V_{OUT}$  to  $V_{IN}$ .

#### LIN State

When EN rises, if  $V_{IN} > UVLO$ , the regulator first attempts to bring  $V_{OUT}$  within about 1V of  $V_{IN}$  by using the internal fixed current source from  $V_{IN}$  (I<sub>LIN1</sub>). The current is limited to about 630 mA during LIN1 Mode.

If  $V_{OUT}$  reaches  $V_{IN}$ -1V during LIN1 Mode, the SS state is initiated. Otherwise, LIN1 times out after 16 clock counts and the LIN2 Mode is entered.

In LIN2 Mode, the current source is incremented to 850 mA. If  $V_{OUT}$  fails to reach  $V_{IN}$ -1 V after 64 clock counts, a fault condition is declared.

#### SS State

Upon the successful completion of the LIN state ( $V_{OUT} \ge V_{IN} - 1 V$ ), the regulator begins switching with boost pulses current limited to about 50% of nominal level, incrementing to full scale over a period of 32 clock counts.

If the output fails to achieve 90% of its set point within 96 clock counts at full-scale current limit, a fault condition is declared.

#### **BST State**

This is the normal operating mode of the regulator. The regulator uses a minimum  $t_{OFF}$ -minimum  $t_{ON}$  modulation scheme. Minimum  $t_{OFF}$  is proportional to  $V_{IN} / V_{OUT}$ , which keeps the regulator's switching frequency reasonably constant in CCM.  $t_{ON(MIN)}$  is proportional to  $V_{IN}$  and is higher if the inductor current reaches 0 before  $t_{OFF(MIN)}$  during the prior cycle.

To ensure that  $V_{OUT}$  does not pump significantly above the regulation point, the boost switch remains off as long as FB >  $V_{REF}$ .

#### Fault State

The regulator enters the FAULT state under any of the following conditions:

- V<sub>OUT</sub> fails to achieve the voltage required to advance from LIN state to SS state

- V<sub>OUT</sub> fails to achieve the voltage required to advance from SS state to BST state

- Sustained (32 CLK counts) pulse-by-pulse current limit during the BST state

- The regulator moves from BST to LIN state due to a short circuit or output overload (V<sub>OUT</sub> < V<sub>IN</sub>-1 V) Once a fault is triggered, the regulator stops switching and

presents a high-impedance path between  $V_{IN}$  and  $V_{OUT}$ . After waiting 480 CLK counts, a restart is attempted.

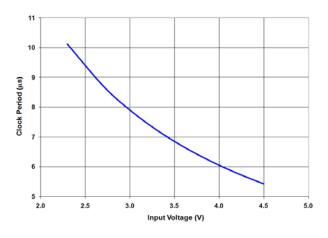

#### Soft-Start and Fault Timing

The soft–start timing for each state, and the fault times, are determined by the fault clock, whose period is inversely proportional to  $V_{IN}$ . This allows the regulator more time to charge larger values of  $C_{OUT}$  when  $V_{IN}$  is lower. With higher  $V_{IN}$ , this also reduces power delivered to  $V_{OUT}$  during each cycle in current limit.

Figure 15. Fault Response into Short Circuit

The fault clock period as a function of  $V_{IN}$  is shown in Figure 16.

Figure 16. Fault Clock Period vs. VIN

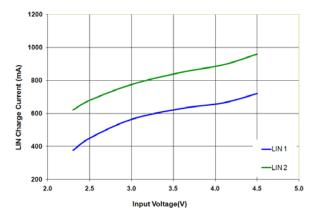

The  $V_{IN}$ -dependent LIN Mode charging current is illustrated in Figure 17.

Figure 17. LIN Mode Current vs. VIN

#### **Over-Temperature Protection (OTP)**

The regulator shuts down when the thermal shutdown threshold is reached. Restart, with soft–start, occurs when the IC has cooled by about  $30^{\circ}$ C.

#### **Over-Current Protection (OCP)**

During Boost Mode, the FAN4868 employs a cycle–by–cycle peak current limit to protect switching elements. Sustained current limit, for 32 consecutive fault clock counts, initiates a fault condition.

During an overload condition, as  $V_{OUT}$  collapses to approximately  $V_{IN}$ -1 V, the synchronous rectifier is immediately switched off and a fault condition is declared.

Automatic restart occurs once the overload/short is removed and the fault timer completes counting.

#### **APPLICATION INFORMATION**

#### **External Component Selection**

Table 8 shows the recommended external components for the FAN4868:

#### Table 8. EXTERNAL COMPONENTS

| REF              | Description                         | Manufacturer                              |

|------------------|-------------------------------------|-------------------------------------------|

| L1               | 1.0 μH, 0.8 A,<br>190 mΩ, 0805      | Murata<br>LQM21PN1R0MC0,<br>or equivalent |

| C <sub>IN</sub>  | 2.2 μF, 6.3 V, X5R, 0402            | Murata<br>GRM155R60J225M                  |

|                  |                                     | TDK C1005X5R0J225M                        |

| C <sub>OUT</sub> | 4.7 μF, 10 V, X5R, 0603<br>(Note 5) | Kemet<br>C0603C475K8PAC                   |

|                  |                                     | TDK C1608X5R1A475K                        |

5. A 6.3 V-rated 0603 capacitor may be used for C<sub>OUT</sub>, such as Murata GRM188R60J225M. All datasheet parameters are valid with the 6.3 V-rated capacitor. Due to DC bias effects, the 10 V capacitor offers a performance enhancement; particularly output ripple and transient response, without any size increase.

#### **Output Capacitance (COUT)**

#### Stability

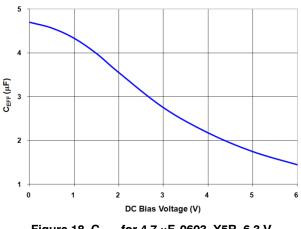

The effective capacitance ( $C_{EFF}$ ) of small, high-value, ceramic capacitors decrease as their bias voltage increases, as shown in Figure 18.

Figure 18. C<sub>EFF</sub> for 4.7 μF, 0603, X5R, 6.3 V (Murata GRM188R60J475K)

FAN4868 is guaranteed for stable operation with the minimum value of  $C_{EFF}$  ( $C_{EFF(MIN)}$ ) outlined in Table 9.

Table 9. MINIMUM CEFF REQUIRED FOR STABILITY

| Operating           |                        |                            |

|---------------------|------------------------|----------------------------|

| V <sub>IN</sub> (V) | I <sub>LOAD</sub> (mA) | C <sub>EFF(MIN)</sub> (μF) |

| 2.3 to 4.5          | 0 to 200               | 1.5                        |

| 2.7 to 4.5          | 0 to 200               | 1.0                        |

| 2.3 to 4.5          | 0 to 150               | 1.0                        |

$C_{EFF}$  varies with manufacturer, dielectric material, case size, and temperature. Some manufacturers may be able to provide an X5R capacitor in 0402 case size that retains  $C_{EFF}$ > 1.5 µF with 5 V bias; others may not. If this  $C_{EFF}$  cannot be economically obtained and 0402 case size is required, the IC can work with the 0402 capacitor as long as the minimum  $V_{IN}$  is restricted to > 2.7 V.

For best performance, a 10 V-rated 0603 output capacitor is recommended (Kemet C0603C475K8PAC, or equivalent). Since it retains greater  $C_{\rm EFF}$  under bias and over temperature, output ripple can is reduced and transient capability enhanced.

#### **Output Voltage Ripple**

Output voltage ripple is inversely proportional to  $C_{OUT}$ . During t<sub>ON</sub>, when the boost switch is on, all load current is supplied by  $C_{OUT}$ .

$$V_{\text{RIPPLE}(P-P)} = t_{\text{ON}} \times \frac{I_{\text{LOAD}}}{C_{\text{OUT}}}$$

(eq. 2)

and

$$t_{\text{ON}} = t_{\text{SW}} \times \text{D} = t_{\text{SW}} \times (1 - \frac{\text{V}_{\text{IN}}}{\text{V}_{\text{OUT}}}) \quad (\text{eq. 3})$$

Therefore:

$$V_{\text{RIPPLE}(P-P)} = t_{\text{SW}} \times (1 - \frac{V_{\text{IN}}}{V_{\text{OUT}}}) \times \frac{I_{\text{LOAD}}}{C_{\text{OUT}}} \quad (\text{eq. 4})$$

Where:

$$t_{SW} = \frac{1}{f_{SW}}$$

(eq. 5)

As can be seen from Equation 4, the maximum  $V_{RIPPLE}$  occurs when  $V_{IN}$  is minimum and  $I_{LOAD}$  is maximum.

#### Startup

Input current limiting is in effect during soft–start, which limits the current available to charge  $C_{OUT}$ . If the output fails to achieve regulation within the time period described in the soft–start section above; a FAULT occurs, causing the circuit to shut down, then restart after a significant time period. If  $C_{OUT}$  is a very high value, the circuit may not start on the first attempt, but eventually achieves regulation if no load is present. If a high–current load and high capacitance are both present during soft–start, the circuit may fail to achieve regulation and continually attempt soft–start, only to have  $C_{OUT}$  discharged by the load when in the FAULT state.

The circuit can start with higher values of  $C_{OUT}$  under full load if  $V_{IN}$  is higher, since:

$$I_{OUT} = (I_{LIM(PK)} - \frac{I_{RIPPLE}}{2}) \times \frac{V_{IN}}{V_{OUT}}$$

(eq. 6)

Generally, the limitation occurs in BST Mode.

The FAN4868 starts on the first pass (without triggering a FAULT) under the following conditions for  $C_{EFF(MAX)}$ :

| Operating           |                                                    |                            |

|---------------------|----------------------------------------------------|----------------------------|

| V <sub>IN</sub> (V) | R <sub>LOAD(MIN)</sub> (Ω)<br>3.3 V <sub>OUT</sub> | C <sub>EFF(MAX)</sub> (μF) |

| > 2.3               | 16                                                 | 10                         |

| > 2.7               | 16                                                 | 15                         |

| > 2.7               | 20                                                 | 22                         |

#### Table 10. MAXIMUM C<sub>EFF</sub> FOR FIRST-PASS STARTUP

$C_{EFF}$  values shown in Table 10 typically apply to the lowest  $V_{IN}$ . The presence of higher  $V_{IN}$  enhances ability to start into larger  $C_{EFF}$  at full load.

#### **Transient Protection**

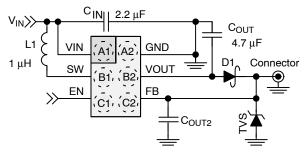

To protect against external voltage transients caused by ESD discharge events, or improper external connections, some applications employ an external transient voltage suppressor (TVS) and Schottky diode (D1 in Figure 19).

#### Figure 19. FAN4868 with External Transient Protection

The TVS is designed to clamp the FB line (system  $V_{OUT}$ ) to +10 V or -2 V during external transient events. The Schottky diode protects the output devices from the positive excursion. The FB pin can tolerate up to 14 V of positive excursion, while both the FB and VOUT pins can tolerate negative voltages.

The FAN4868 includes a circuit to detect a missing or defective D1 by comparing  $V_{OUT}$  to FB. If  $V_{OUT} - FB >$  about 0.7 V, the IC shuts down. The IC remains shut down until  $V_{OUT} < UVLO$  and  $V_{IN} < UVLO + 0.7$  or EN is toggled.

$C_{OUT2}$  may be necessary to preserve load transient response when the Schottky is used. When a load is applied at the FB pin, the forward voltage of the D1 rapidly increases before the regulator can respond or the inductor current can change. This causes an immediate drop of up to 300 mV, depending on D1's characteristics if  $C_{OUT2}$  is absent.  $C_{OUT2}$ supplies instantaneous current to the load while the regulator adjusts the inductor current. A value of at least half of the minimum value of  $C_{OUT}$  should be used for  $C_{OUT2}$ .  $C_{OUT2}$ needs to withstand the maximum voltage at the FB pin as the TVS is clamping.

The maximum DC output current available is reduced with this circuit, due to the additional dissipation of D1.

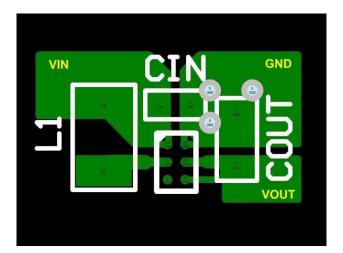

#### LAYOUT GUIDELINE

Figure 20. WLCSP Suggested Layout (Top View)

WLCSP6 0.88x1.23x0.458

DATE 28 NOV 2017

| HE S | OLDER | BALLS    |             |       |  |  |

|------|-------|----------|-------------|-------|--|--|

|      |       | MI       | MILLIMETERS |       |  |  |

|      | DIM   | MIN.     | NOM.        | MAX.  |  |  |

|      | А     | .419     | .458        | .497  |  |  |

|      | A1    | .187     | .208        | .229  |  |  |

|      | A2    | .232     | .250        | .268  |  |  |

|      | b     | 0.240    | 0.260       | 0.280 |  |  |

|      | D     | 0.85     | 0.88        | 0.91  |  |  |

|      | Е     | 1.200    | 1.230       | 1.260 |  |  |

|      | е     | 0.40 BSC |             |       |  |  |

|      | х     | 0.225    | 0.240       | 0.255 |  |  |

0.215

0.230

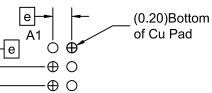

RECOMMENDED MOUNTING FOOTPRINT (NSMD PAD TYPE)

0.200

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98AON79926G Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | WLCSP6 0.88x1.23x0.458                                                                                                                                                                          |  | PAGE 1 OF 1 |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |                                                                                                                                                                                                 |  |             |

BOTTOM VIEW

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative