## **EVK-JODY-W3**

## Evaluation kit for JODY-W3 host-based modules

User guide

## **Abstract**

This document describes how to set up and use the EVK-JODY-W3 evaluation kit to evaluate JODY-W3 series multiradio modules with Wi-Fi and Bluetooth.

## **Document information**

| Title                  | EVK-JODY-W3                                   |             |

|------------------------|-----------------------------------------------|-------------|

| Subtitle               | Evaluation kit for JODY-W3 host-based modules |             |

| Document type          | User guide                                    |             |

| Document number        | UBX-20030840                                  |             |

| Revision and date      | R04                                           | 17-Nov-2021 |

| Disclosure restriction | C1 – Public                                   |             |

#### This document applies to the following products:

| Product name  | Type number          | Hardware version     | PCN reference |

|---------------|----------------------|----------------------|---------------|

| EVK-JODY-W374 | EVK-JODY-W374-00A-00 | Module board rev. B  | N/A           |

| EVK-JODY-W377 | EVK-JODY-W377-00A-00 | Carrier board rev. D | N/A           |

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only permitted with the express written permission of u-blox.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com.

Copyright © u-blox AG.

## Contents

| 1.1  | Ove | erview                                  | 4   |

|------|-----|-----------------------------------------|-----|

| 1.2  | Kit | includes                                | 6   |

| 1.3  | Sof | tware                                   | 7   |

| 1.4  | Sys | stem requirements                       | 7   |

| 1.5  | Оре | erating conditions                      | 8   |

| 3.1  | Blo | ck diagram                              | 11  |

| 3.2  | Jur | npers and connectors                    | 12  |

| 3.   | 2.1 | Jumper and switch configuration options | 13  |

| 3.   | 2.2 | Jumper conventions                      | 13  |

| 3.3  | Pov | ver supply configuration                | 14  |

| 3.   | 3.1 | Selecting the EVB power supply          | 15  |

| 3.   | 3.2 | Selecting the module input voltage      | 16  |

| 3.4  | Вос | otstrapping                             | 18  |

| 3.5  | PCI | e interface                             | 19  |

| 3.6  | SDI | O interface                             | 20  |

| 3.7  | Blu | etooth host interface                   | 21  |

| 3.8  | Blu | etooth audio interface                  | 21  |

| 3.9  | Ant | tenna interfaces                        | 22  |

| 3.9  | 9.1 | EVK-JODY-W374 antenna connections       | 23  |

| 3.9  | 9.2 | EVK-JODY-W377 antenna connections       | 23  |

| 3.10 | Oth | ner interfaces                          | 24  |

| 3.11 | LED | Os                                      | 24  |

| 3.12 | Res | set buttons                             | 25  |

| 0 10 |     |                                         | 0.5 |

## 1 Kit description

JODY-W3 series modules provide complete short-range transceiver solutions based on the NXP chipset 88Q9098.

Intended for the most advanced in-car infotainment and connectivity systems, JODY-W3 series modules deliver the highest data rates in Wi-Fi using advanced Wi-Fi 6 802.11ax technology. The modules operate in concurrent dual-bands, Wi-Fi 2.4 and 5 GHz, dual-MAC, and 2x2 MIMO, and support Bluetooth 5.1 features like extended advertising, long range, and 2 Mbit/s (PHY) data rates.

The modules require a host processor running Linux or Android and connect to the host processor through either PCle or SDIO for Wi-Fi, SDIO or high-speed UART for Bluetooth, and PCM/I2S for Bluetooth audio.

EVK-JODY-W3 allows an external host processor to access several practical features for testing and evaluating the Wi-Fi and Bluetooth connectivity supported in JODY-W3 series modules, including:

- External connectors to all host interfaces (PCIe, SDIO and UART)

- USB interface for easy access the Bluetooth UART interface through a USB-to-UART bridge

- Digital and analog audio interfaces for Bluetooth

- Two internal dual-band 2.4/5 GHz antennas for Wi-Fi and Bluetooth.

- Three SMA connectors for external antennas.

- GPIO pins and other module interfaces are accessible through pin headers

- Multiple power supply options

For more information about JODY-W3 modules, see the JODY-W3 series data sheet [1] and system integration manual [2].

### 1.1 Overview

Table 1 lists the available evaluation kit versions:

| Evaluation kit | Ordering code     | Description                                                                                                                                        | Suitable for evaluation of |

|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| EVK-JODY-W374  | EVK-JODY-W374-00A | Evaluation kit for JODY-W374  Two antennas for simultaneous dual-band Wi-Fi (1x1 2.4 GHz and 2x2 5 GHz) and Bluetooth 5.1                          | JODY-W374-00A              |

| EVK-JODY-W377  | EVK-JODY-W377-00A | Evaluation kit for JODY-W377 Three antennas for simultaneous dual-band Wi-Fi (2x2 2.4 GHz and 2x2 5 GHz) and a dedicated antenna for Bluetooth 5.1 | JODY-W377-00A              |

Table 1: Available EVK-JODY-W3 evaluation kits

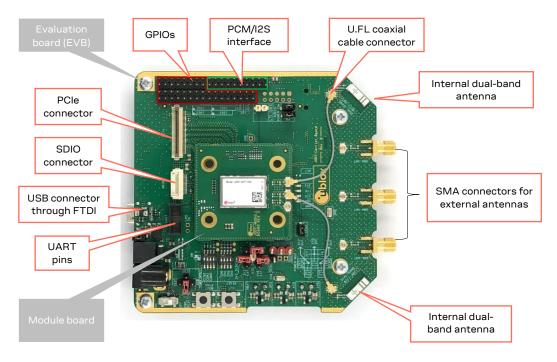

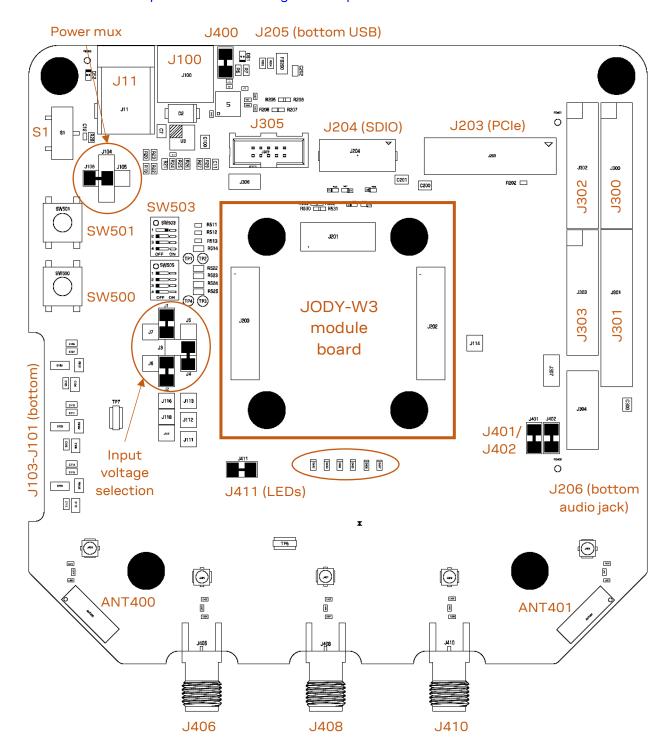

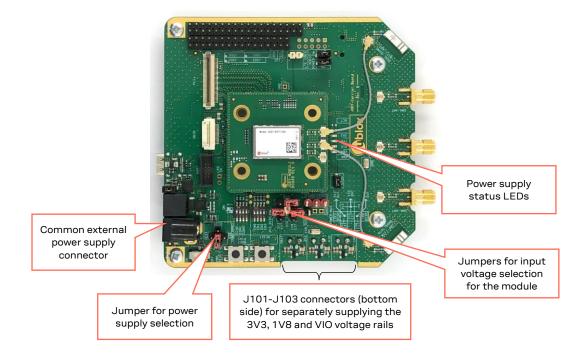

Figure 1 shows the main components of the EVK-JODY-W3 evaluation board.

Figure 1: EVK-JODY-W3 outline showing main interfaces and connectors

The evaluation board design includes a module board and a carrier board:

- The module board includes the JODY-W3 module and U.FL antenna connectors that connect directly to the antenna pins on the module.

- The larger carrier board hosts the module board and includes all the necessary connectors for connecting the JODY-W3 series module to the host system.

## 1.2 Kit includes

Table 2 shows the various components included in the EVK-JODY-W3.

| Part                         | Description                                                                                                                                                                                                             |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Evaluation<br>board<br>(EVB) | Evaluation board for the JODY-W3 series modules. The board includes SMA antenna connectors that connect to external antennas for Wi-Fi and Bluetooth. It also supports two internal dual-band Wi-Fi/Bluetooth antennas. |

Outline

M.2 PCle

M.2 PCle to ZIF adapter for Wi-Fi host communication.

to ZIF

One flat ZIF cable is included for both PCle adapters.

adapter

Mini-PCle to ZIF adapter for Wi-Fi host communication. to ZIF One flat ZIF cable is included for both PCle adapters. adapter

Micro SDIO to ZIF adapter and flat cable for Wi-Fi and/or SDIO to Bluetooth host communication. The adapter is compatible with host sockets designed for micro-SD adapter and flat

Type-C USB cable for Bluetooth host communication USB cable through the USB-to-UART bridge

External 2 x Dual band Wi-Fi/Bluetooth antenna, antennas Linx Technologies ANT-DB1-RAF-SMA

Table 2: EVK-JODY-W3 component list

ZIF cable

#### 1.3 Software

JODY-W3 series modules are based on the NXP 88Q9098 chipset. The drivers and firmware required to operate JODY-W3 series modules are developed by NXP and are already integrated into the Linux BSP for the NXP i.MX application processors [5].<sup>1</sup>

The documentation for the software releases from NXP contains Wi-Fi and Bluetooth release notes and a list of supported software features. The driver source code is provided free of charge as open source under NXP license terms. Being open source allows the drivers to be integrated or ported to other non-NXP based host platforms. Yocto recipes for the driver and firmware, that can be used to develop custom Linux-based systems, are part of the NXP i.MX Linux BSP.

The latest version of the driver source code and Wi-Fi/Bluetooth firmware are available from the following open-source repositories:

- Wi-Fi driver: https://source.codeaurora.org/external/imx/mwifiex/

- Firmware: https://github.com/NXP/imx-firmware/

- Use the repository branches matching to the latest Linux BSP release version. At the time of publication, this is release 5.10.52 2.1.0.

The Wi-Fi driver uses the TCP/IP stack from the Linux kernel for data transmission and the cfg80211 subsystem in the kernel for configuration and control. The  $hci\_uart$  driver from the Linux kernel and BlueZ host stack are used for the Bluetooth part. For further information about initialization and configuration of the Wi-Fi and Bluetooth features, see also the JODY-W3 system integration manual [2] and the NXP User Manual UM11490 [6].

Contact your local u-blox support team for information about additional software options for the JODY-W3 series modules.

## 1.4 System requirements

The evaluation kit has the following system requirements:

- Host (PC or embedded system) with

- o Mini-PCle or M.2 Key E slot for access to Wi-Fi through the PCle 2.0 host interface

- o Micro SDIO slot for access to Wi-Fi through the SDIO 3.0 host interface

- USB 2.0 interface for access to the Bluetooth UART interface through USB-to-UART bridge

- Supported operating systems

- Linux (3.x/4.x/5.x)

- o Android

UBX-20030840 - R04 Kit description Page 7 of 29

$<sup>^{1}</sup>$  Drivers for PCIE-UART are currently supported. SDIO-UART support is planned for Q1/2022.

## 1.5 Operating conditions

Table 3 describes the recommended operating conditions for the EVK-JODY-W3. For more information about power supply requirements, see also the JODY-W3 series data sheet [1].

| Symbol                    | Parameter                                        |       | Min. | Тур. | Max. | Units |

|---------------------------|--------------------------------------------------|-------|------|------|------|-------|

| 3V3/VDD_PCIE<br>/VDD_SDIO | Module 3.3 V po<br>source (J101), P              | 3.14  | 3.3  | 3.46 | V    |       |

|                           | Module I/O                                       | 1.8 V | 1.71 | 1.8  | 1.89 | V     |

| VIO                       | supply voltage<br>(J102)                         | 3.3 V | 3.14 | 3.3  | 3.46 | V     |

| 1V8                       | Module analog power supply voltage 1.8 V (J103)  |       | 1.71 | 1.8  | 1.89 | V     |

| VDD_SYS                   | EVB external power supply (J11/J100)             |       | 4.5  |      | 25.4 | V     |

| VDD_USB3                  | EVB power supply from USB                        |       | 4.5  | 5    | 5.5  | V     |

| T <sub>A</sub>            | Ambient operating temperature                    |       | -40  | -    | +85* | °C    |

| Ripple Noise              | Peak-to-peak voltage ripple on all supply lines. |       | -    | -    | 30   | mV    |

Table 3: EVK-JODY-W3 operating conditions

**7**

The signal voltage for the SDIO interface of the JODY-W3 series module is powered from the **1V8** supply. A level shifter is required to operate the module in Default Speed and High-Speed modes at 3.3 V signal voltage [3]. Contact your local u-blox support team for further information.

## 2 Getting started

This chapter describes the basic settings and procedures to get started with EVK-JODY-W3.

An overview of the EVB and its main connectors is shown in Figure 1. For more detailed description of the available connectors and configuration options, see Board description.

Follow the procedure below to evaluate JODY-W3 series module using EVK-JODY-W3:

- Connect the coaxial cables to the U.FL connectors on the module board and internal antennas on the carrier board; or to SMA connectors for use with external antennas or conducted test setup. The default antenna configuration is described below:

- EVK-JODY-W374 uses both of its two internal dual-band antennas for Wi-Fi and Bluetooth communication.

- EVK-JODY-W377 uses one of its two internal antennas for Bluetooth, and Wi-Fi communication is configured for use through SMA connectors SMA1 and SMA2. Connect the two supplied external antennas to the selected SMA connectors on the EVB.

For more information about the antenna configuration, see also Antenna interfaces.

- 2. Set DIP switch SW503 to select the host interfaces for Wi-Fi and Bluetooth from the possible combinations PCIE-UART, SDIO-UART or SDIO-SDIO, as described in Bootstrapping.

- 3. Configure the power supply source as described in Power supply configuration and shown in Table 5. The most common configuration uses the Wi-Fi host interface as the supply source, which can be either PCle or SDIO.

- 4. Connect the host interfaces to the host system. The EVB and supplied PCle and SDIO adapters use zero insertion force (ZIF) connectors with flat cables for connecting the adapters. To connect the cable, gently flip up the small locking flap of the connector, align and insert the flat cable with the blue marking pointing upwards, and then close the locking flap.

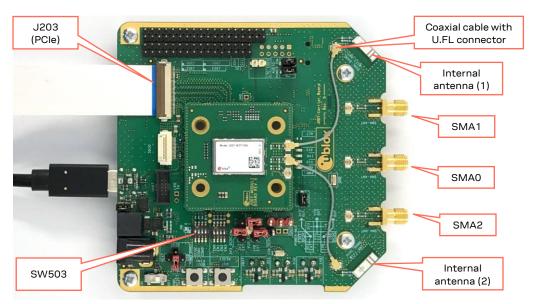

- For PCIe connection to the host, use either the M.2 or the mini-PCIe adapter depending on the available connector on the host platform. First, plug the adapter into the PCIe connector on the host system. Then connect it with the flat cable to the connector (J203) on the EVB, as shown in Figure 2. The PCIe interface can be used for Wi-Fi communication with the JODY-W3 series module.

Figure 2: PCIe and USB connectors

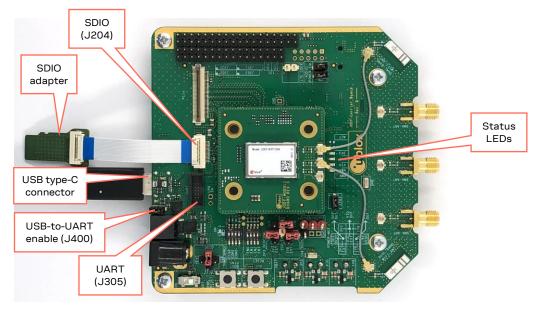

For SDIO connection, connect the supplied micro SDIO adapter card with the flat cable to the SDIO connector (J204) on the EVB, as shown in Figure 3. Insert the adapter card into an SDIO connector of the host system. The SDIO interface can be used for Wi-F and optionally Bluetooth communication with the JODY-W3 series module.

Figure 3: SDIO and USB connectors

- A high speed UART interface can be used for Bluetooth communication with the JODY-W3 series module. A USB-to-UART bridge is included on the evaluation board. To use the Bluetooth interface through USB, connect the supplied USB cable to the USB type-C connector on the EVB and connect it to a USB interface on the host system. Make sure that jumper J400 is bridged (default setting) to enable Bluetooth communication over USB. For information about accessing the UART interface for Bluetooth directly, see also Bluetooth host interface.

- 5. Power on the host system. The LEDs on the EVB indicate the status of the different voltage rails and should turn green to indicate proper power supply. At this point, the module should be detected by the host system.

- 6. Install the necessary driver software for the JODY-W3 module, as described in the JODY-W3 system integration manual [2].

## 3 Board description

This chapter describes the logical components, connectors, jumpers, and switches used to configure the EVK-JODY-W3.

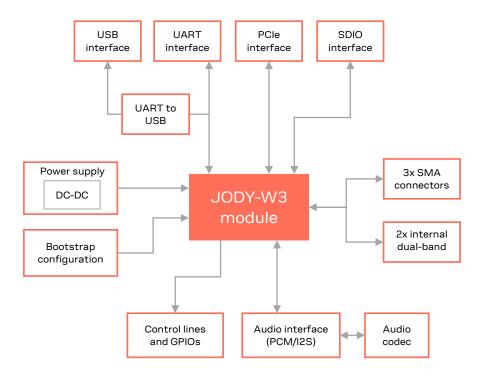

## 3.1 Block diagram

Figure 4 shows the block diagram of the EVB and the logical connections between the JODY-W3 module and the various peripherals around it.

Figure 4: EVK-JODY-W3 block diagram

## 3.2 Jumpers and connectors

Figure 5 shows an outline of the evaluation board and the placement of the connectors, jumpers, and switches. The EVB makes all interfaces of the JODY-W3 module accessible through connectors or pin headers. See also Jumper and switch configuration options

Figure 5: EVK-JODY-W3 jumpers and connectors

## 3.2.1 Jumper and switch configuration options

Table 4 provides a summary of the connectors and jumpers used to configure EVK-JODY-W3.

| Designator       | Connector                          | Description                                                                                                 |

|------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------|

| J104-J106        | Power supply selection (power mux) | Jumper settings for external power supply selection. See also External power supply selection.              |

| J1-J7            | Input voltage selection            | Jumper settings for selecting the input voltages for the module. See also Input voltage selection.          |

| SW503            | Bootstrapping                      | Switch for host interface selection. See also Bootstrapping.                                                |

| J203             | PCle connector                     | ZIF connector for PCle host interface on EVB.<br>See also PCle interface.                                   |

| J204             | SDIO connector                     | ZIF connector for SDIO host interface on EVB.<br>See also SDIO interface.                                   |

| J205             | Type-C USB                         | USB connector for Bluetooth host interface (through USB-to-UART bridge). See also Bluetooth host interface. |

| J400             | USB-UART Enable                    | Jumper to enable/disable the Bluetooth host interface through USB-to-UART bridge                            |

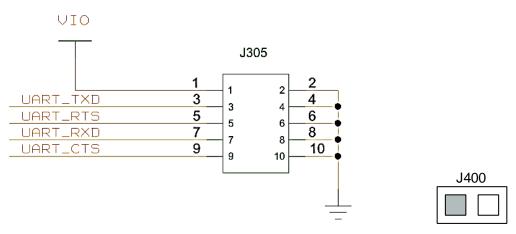

| J305             | Bluetooth UART                     | UART connector for Bluetooth host interface. See also Bluetooth host interface.                             |

| J401, J402       | Audio codec enable                 | Jumpers to enable the audio codec on the EVB (3.8)                                                          |

| J206             | Audio jack                         | Audio jack for the audio codec. See also Bluetooth audio interface.                                         |

| J301             | Bluetooth audio                    | Connector for the PCM/I2S audio interface. See also Bluetooth audio interface.                              |

| J300, J302, J303 | Control lines                      | Connector for host and device wake for Bluetooth and Wi-Fi.<br>See also Other interfaces.                   |

| J406, J408, J410 | SMA connectors                     | SMA coaxial RF connectors for external antennas. See also Antenna interfaces.                               |

| ANT400, ANT401   | Internal antennas                  | Internal dual-band chip antennas.<br>See also Antenna interfaces.                                           |

| SW500, SW501     | Reset buttons                      | Reset buttons for module and power supply. See also Reset buttons.                                          |

| S1               | Power enable switch                | External EVB power supply switch                                                                            |

| J11, J100        | Power jack                         | Power jack and connector for common external EVB supply                                                     |

| J101-J103        | External supply                    | Connectors for individual external supplies                                                                 |

| J411             | LEDs                               | Jumper to enable power supply LEDs.<br>See also LEDs.                                                       |

Table 4: JODY-W3 evaluation board connectors

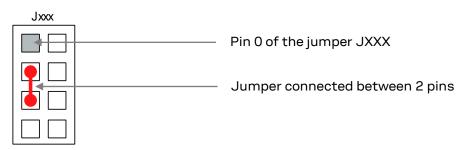

## 3.2.2 Jumper conventions

Figure 6 shows the graphical conventions used for the jumper settings described in this document. Pin 0 is shown in grey color. All jumpers are shown with red lines terminated with round edges.

Figure 6: Jumper convention

## 3.3 Power supply configuration

JODY-W3 series modules must be supplied with 1.8 V (**1V8**), 3.3 V (**3V3**), and a **VIO** voltage that can be either 1.8 V or 3.3 V. The power supply for the EVB can be provided over the different host interfaces or from external sources.

The following power supply options are available on the EVB:

- PCle, SDIO, USB interfaces: The EVB is powered through the host interface. All internal voltages are generated by DC-DC converters on the EVB.

- Common external power supply: The EVB can be connected to an external (5 V to 24 V) power supply through a 2.1 x 6.3 mm DC power jack (J11). DC-DC converters are used for generating all the required internal voltages.

- Separate external supplies: All the individual, **3V3**, **1V8**, and **VIO** voltage rails are supplied from external power sources through the connectors J101-J103.

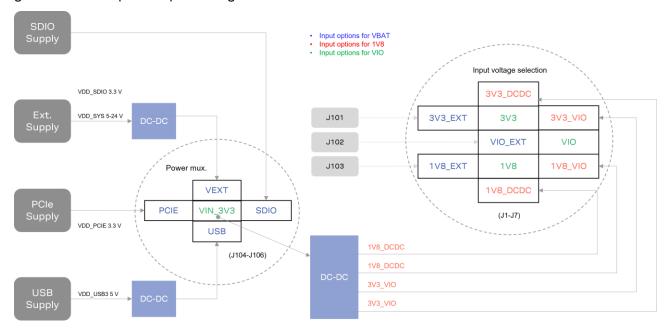

Figure 7 shows the external connectors and jumpers used for configuring the different power supply options.

Figure 7: Overview of EVB power supply configuration

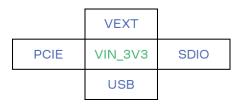

To operate the JODY-W3 EVB, the external power supply source (power mux) and input voltage levels to the module must be configured using jumpers on the EVB. The power supply tree, including the jumpers on the EVB, is shown in Figure 8. See also Jumpers and connectors.

- J104–J106 configure the EVB power supply source (SDIO, PCIe, USB or external) to the VIN\_3V3

domain, which generates the internal power rails for the module.

- J1-J7 configure the input voltages for the JODY-W3 series module, which can be selected between the internally generated voltages and the external supplies from J103-J103.

DC-DC converters are used to step-down the external and USB supplies to the power mux and generate the required input voltages for the module.

Figure 8: JODY-W3 EVB power supply tree

## 3.3.1 Selecting the EVB power supply

Use jumpers J104–J106 to select the EVB power supply (power mux) for the EVB. Figure 9 shows the arrangement of external power supply sources for each jumper position.

Figure 9: External power supply selection, J104-J106

VIN\_3V3 is the input to the DC-DC converter on the EVB that generates the required voltage rails (3V3\_DCDC, 1V8\_DCDC, 3V3\_VIO, and 1V8\_VIO) for the module, as shown in Figure 8. A single jumper is connected between VIN\_3V3 and the chosen voltage supply to the EVB.

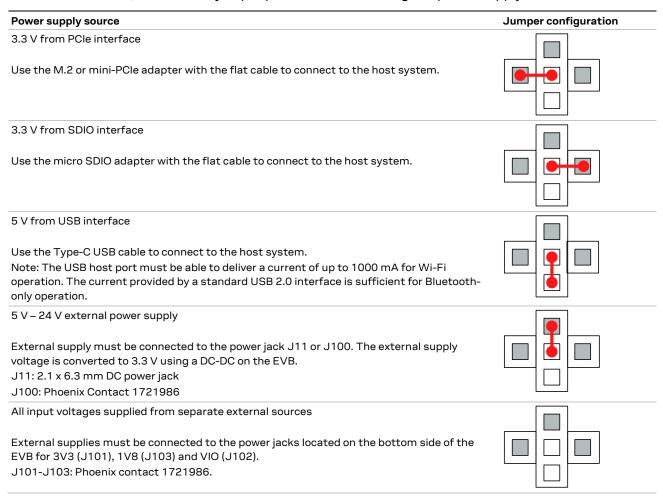

Table 5 shows the (J104-J106) jumper positions for selecting the power supply source for the EVB.

Table 5: Jumper settings for selecting the EVB power supply (J104 - J106)

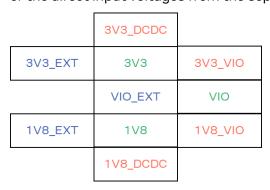

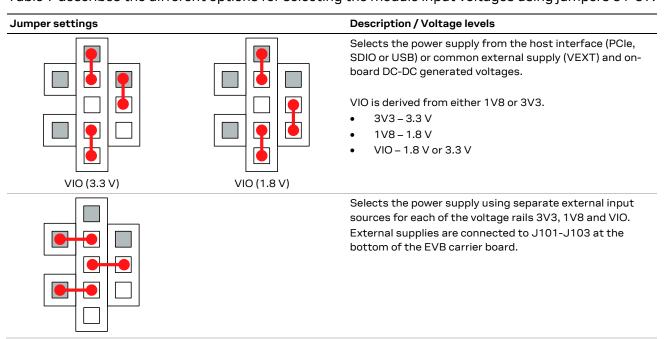

#### 3.3.2 Selecting the module input voltage

Use jumpers J1-J7 to select the external power source to the module, as shown in Figure 8. The input voltage to the module can be sourced from either the on-board DC-DC generated voltages or the direct input voltages from the separate external supplies J101-J103.

Figure 10: Input voltage selection (J1-J7)

The input voltage options for selecting the module supply are described in Table 6.

| Designator | Module supply | Source                                           |

|------------|---------------|--------------------------------------------------|

| 3V3        | 3V3           | Can be connected to 3V3_DCDC or 3V3_EXT          |

| VIO        | VIO           | Can be connected to 3V3_VIO, 1V8_VIO, or VIO_EXT |

| 1V8        | 1V8           | Can be connected to 1V8_DCDC or 1V8_EXT          |

Table 6: Input voltage options

Table 7 describes the different options for selecting the module input voltages using jumpers J1-J7.

Table 7: Jumper settings (J1-J7) for selecting module input voltage

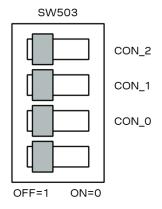

## 3.4 Bootstrapping

JODY-W3 supports the following host interface combinations:

- **PCIE-UART** mode: Commands and data for the Wi-Fi traffic are transferred through the PCle bus to the module. The Bluetooth traffic uses the high-speed UART interface.

- **SDIO-UART** mode: Commands and data for the Wi-Fi traffic is transferred through the SDIO bus to the module. The Bluetooth traffic uses the high-speed UART interface.

- **SDIO-SDIO** mode: Commands and data for both the Wi-Fi and Bluetooth traffic is transferred to the module through the SDIO bus.<sup>2</sup>

DIP switch SW503 is used on the EVB to define the boot mode and the physical interfaces used for Wi-Fi and Bluetooth communication. Set each switch ON to pull the configuration signal low (GND, logic level "0"), and OFF to pull it high (logic level "1").

Figure 11: Boot and host interface configuration

Table 8 describes the DIP switch positions for configuring the boot mode and host interface options.

| Boot mode | CON_2 | CON_1 | CON_0 | Description                                                                    |

|-----------|-------|-------|-------|--------------------------------------------------------------------------------|

| PCIE-UART | ON    | OFF   | OFF   | Wi-Fi through PCle (J203), Bluetooth through USB-to-UART (J205) or UART (J305) |

| SDIO-UART | ON    | ON    | ON    | Wi-Fi through SDIO (J204), Bluetooth through USB-to-UART (J205) or UART (J305) |

| SDIO-SDIO | ON    | ON    | OFF   | Wi-Fi and Bluetooth through SDIO (J204)                                        |

Table 8: Boot mode selection options

The UART interface for Bluetooth can be accessed either directly through J305, or through the USB type-C connector J205 and USB-to-UART bridge. For further information about the Bluetooth UART interface, see also Bluetooth host interface.

UBX-20030840 - R04 Board description Page 18 of 29

<sup>&</sup>lt;sup>2</sup> Driver/firmware support for SDIO-SDIO is currently not productized.

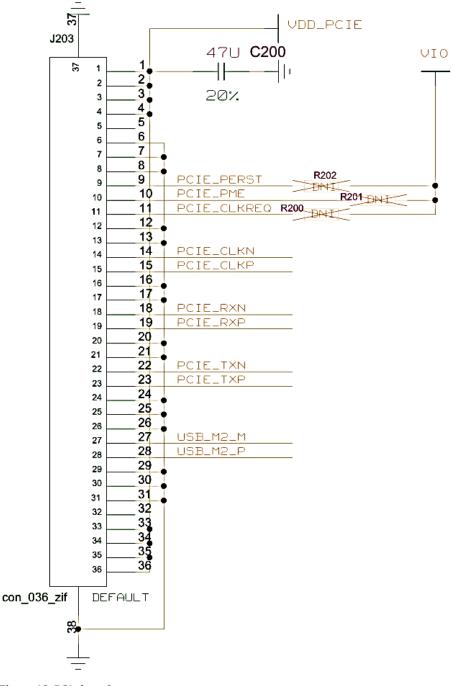

## 3.5 PCIe interface

The EVB can be connected through a PCIe connector for Wi-Fi communication with the host system. Adapters for host-side M.2 Key E and mini-PCIe connectors are supplied in the kit.

The PCle host interface connector (J203) is shown in Figure 12.

Figure 12: PCIe interface connector

VDD\_PCIE can be used for supplying the EVB from the PCIe interface.

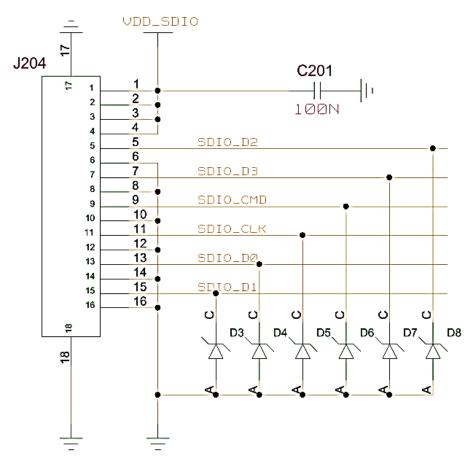

### 3.6 SDIO interface

The EVB can be connected through a micro SDIO connector for Wi-Fi communication with the host system. The SDIO connector can optionally be used for Bluetooth<sup>3</sup>.

The SDIO host interface connector (J204) is shown in Figure 13.

Figure 13: SDIO interface connector

All signals except **VDD\_SDIO** are directly connected to the JODY-W3 module through 22  $\Omega$  series resistors connected on the module board.

**VDD\_SDIO** can be used for supplying the EVB from the SDIO interface. The SDIO signals are powered by the **1V8** voltage domain.

Pull-up resistors for the SDIO lines are not installed on the EVB because they are typically included in the host CPU. The EVB carrier board has the provision to install pull-up resistors if needed by the design.

UBX-20030840 - R04 Board description Page 20 of 29

<sup>&</sup>lt;sup>3</sup> SDIO support for Bluetooth is currently not productized.

### 3.7 Bluetooth host interface

The Bluetooth UART host interface of the JODY-W3 series module can be accessed either directly through the UART pins on J305, or through the USB type-C connector through a USB-to-UART bridge (default).

A USB-to-UART bridge (FTDI FT231X) is included on the evaluation board to connect to the high speed UART interface of the JODY-W3 series module. **VDD\_USB3** from the USB connector is converted by a DC-DC to 3.3 V and can be used for supplying **3V3** from the USB interface. Place the jumper on J400 to use Bluetooth through the USB type-C connector.

Figure 14: Jumper setting to use Bluetooth over USB

The 4-pin UART interface of the JODY-W3 series modules can be directly accessed through the Bluetooth UART connector J305. To use the UART interface directly, remove the jumper on J400 and connect the UART host interface to the respective module side pins and signal ground on J305 as shown in Figure 15 and Table 9. The UART signals are powered by the **VIO** voltage domain.

Figure 15: Bluetooth over UART interface

| Name     | I/O | Description     | Remarks             |

|----------|-----|-----------------|---------------------|

| UART_TXD | 0   | UART TX signal  | Connect to Host RX  |

| UART_RXD | I   | UART RX signal  | Connect to Host TX  |

| UART_RTS | 0   | UART RTS signal | Connect to Host CTS |

| UART_CTS | I   | UART CTS signal | Connect to Host RTS |

Table 9: UART signal description

## 3.8 Bluetooth audio interface

A MAX9860 16-bit audio codec for Bluetooth voice applications is provided on the JODY-W3 EVB and connected to the PCM/I2S interface of the module. A 3.5 mm audio jack (J206) to connect a headset is available on the bottom side of the EVB. The codec is operated with a master clock (MCLK) of 19.2 MHz. The MAX9860 audio codec is completely controlled through software using an I2C interface. The codec responds to the I2C slave address 0x20 for all write commands and 0x21 for all read operations.

Place jumpers J401 and J402 to enable the audio codec, as shown in Figure 16.

Figure 16: Jumpers to enable the audio codec

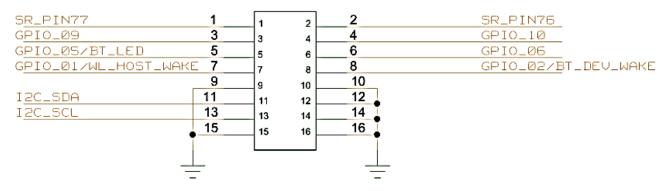

The I2C interface of the audio codec is provided on connector J303 of the EVB as shown in Table 10 and Figure 20. The PCM/I2S interface of the JODY-W3 module is directly connected to the serial audio interface of the MAX9860 audio codec. The PCM pins are shared with the I2S interface and are additionally provided on connector J301 as shown in Table 10 and Figure 19.

| Name     | I/O | Connector / pin no. | Description                                        |

|----------|-----|---------------------|----------------------------------------------------|

| I2C_SDA  | I/O | J303/11             | I2C Serial-Data Input/Output                       |

| I2C_SCL  | I   | J303/13             | I2C Serial-Data clock                              |

| PCM_CLK  | I/O | J301/16             | PCM clock<br>Alternate function: I2S clock         |

| PCM_SYNC | I/O | J301 / 15           | PCM frame sync Alternate function: I2S word select |

| PCM_IN   | I   | J301/18             | PCM data in<br>Alternate function: I2S data in     |

| PCM_OUT  | 0   | J301 / 17           | PCM data out<br>Alternate function: I2S data out   |

Table 10: Audio interfaces

## 3.9 Antenna interfaces

The evaluation board includes two dual-band 2.4/5 GHz chip antennas (Pulse Electronics W3006) for Wi-Fi and Bluetooth communication. Three standard 50  $\Omega$  female SMA connectors are included to connect external antennas or measurement instruments. The antenna interfaces are selected by connecting U.FL connectors on the EVB module board with designated U.FL connectors on the EVB carrier board with coaxial RF cables.

The module board has three U.FL connectors which connect to the antenna pins of the JODY-W3 series module. To use any of the chip antennas or SMA connectors on the EVB carrier board, connect the coaxial RF cables between the U.FL connector on the module board and U.FL connectors on the carrier board. See also EVK-JODY-W374 antenna connections and EVK-JODY-W377 antenna connections.

Figure 11 describes the available radio interfaces of the modules and the default antenna interfaces that are selected in the EVK-JODY-W3.

| a pin Function           | Default antenna interface selected |

|--------------------------|------------------------------------|

| 5GHz Wi-Fi and Bluetooth | Dual-band chip antenna ANT400      |

| 2.4/5 GHz Wi-Fi          | Dual-band chip antenna ANT401      |

| -                        | -                                  |

| 2.4/5 GHz Wi-Fi          | SMA connector 2                    |

| 2.4/5 GHz Wi-Fi          | SMA connector 1                    |

| Bluetooth                | Dual-band chip antenna ANT400      |

|                          | Bluetooth                          |

Table 11: Antenna interface configuration

Connect the external antennas supplied with EVK-JODY-W377 to the selected SMA connectors. For further information about the included external antennas, see also Kit includes.

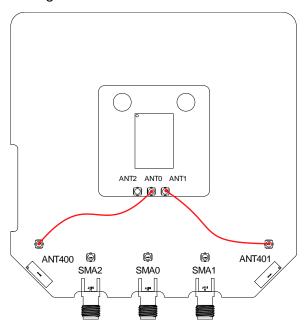

#### 3.9.1 EVK-JODY-W374 antenna connections

On EVK-JODY-W374 the U.FL connectors on the module board (ANT0 and ANT1) are connected through coaxial cables to the two internal antennas on the carrier board (ANT400 and ANT401).

Figure 17: Default antenna configuration for EVK-JODY-W374

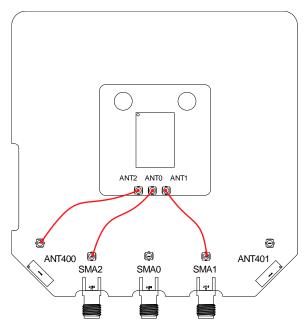

#### 3.9.2 EVK-JODY-W377 antenna connections

On EVK-JODY-W377 one U.FL connector (ANT2) on the module board is connected through a single coaxial cable to the internal antenna (ANT400) on the carrier board. ANT0 and ANT1 on the module board are connected to two SMA connectors (SMA1 and SMA2) on the carrier board for use with external antennas.

Figure 18: Default antenna configuration for EVK-JODY-W377

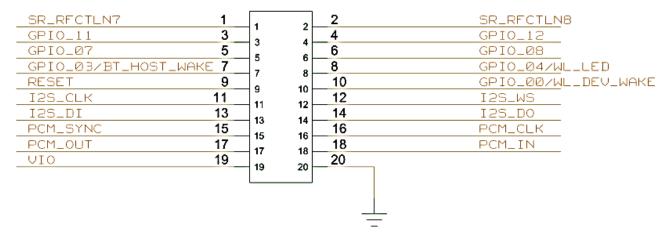

### 3.10 Other interfaces

Connectors J301 and J303 provide several other interfaces from the JODY-W3 series module, such as host wake-up signals, GPIOs, and audio interfaces. Additional GPIOs and RF control signals are provided on connectors J300 and J302. See Schematics for more information.

Figure 19 shows the signals connected through J301.

Figure 19: Connector J301

Figure 19 shows the signals connected through J303.

Figure 20: Connector J303

#### 3.11 LEDs

Table 12 describes the function and designation of the available LEDs on the EVK-JODY-W3 evaluation board.

| in power supply status indication                        | D402                                                                        | Green                                                                                            |

|----------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| ) Cumple (1, 0.) (av. 2, 2.) ()                          |                                                                             |                                                                                                  |

| Supply (1.8 V or 3.3 V)                                  | D403                                                                        | Green                                                                                            |

| 1.8V power supply D404 Green                             |                                                                             | Green                                                                                            |

| -board 3.3 V supply voltage                              | D405                                                                        | Green                                                                                            |

| Wi-Fi activity signal from module GPIO D406 (DNP) Yellow |                                                                             | Yellow                                                                                           |

| etooth activity signal from module GPIO                  | D407 (DNP)                                                                  | Blue                                                                                             |

| V<br>-b                                                  | power supply coard 3.3 V supply voltage ii activity signal from module GPIO | power supply D404 coard 3.3 V supply voltage D405 ci activity signal from module GPIO D406 (DNP) |

Table 12: LED descriptions

Jumper J411 can be removed to turn the LEDs off for module power measurements.

J411

Figure 21: LED enable jumper

## 3.12 Reset buttons

Two buttons, SW500 and SW501, can be used to reset the JODY-W3 module and the whole EVB, respectively.

Button SW500 asserts the **PD#** pin of the JODY-W3 module to enter power down mode, while keeping the supply rails enabled. When exiting the power-down mode, the module is automatically reset and the firmware must be downloaded again.

Button SW501 causes all the module supply rails from the on-board Power Management Unit (PMU) to shut down. Internal power-on reset of the module is triggered when the button is released, which restores power to the module.

#### 3.13 Schematics

Complete schematics for the JODY-W3 evaluation board (carrier and module board) are available on request. For further information, contact your local u-blox support team.

Page 26 of 29

## **Appendix**

## A Glossary

| Abbreviation | Definition                                  |  |  |  |

|--------------|---------------------------------------------|--|--|--|

| EVB          | Evaluation board                            |  |  |  |

| EVK          | Evaluation kit                              |  |  |  |

| HCI          | Host controller interface                   |  |  |  |

| I/O          | Input / output                              |  |  |  |

| I2S          | Inter-Integrated circuit sound              |  |  |  |

| LED          | Light-Emitting Diode                        |  |  |  |

| LDO          | Low-dropout regulator                       |  |  |  |

| LPO          | Low-power oscillator                        |  |  |  |

| LTE          | Long-Term Evolution                         |  |  |  |

| MAC          | Medium access control                       |  |  |  |

| MIMO         | Multiple input multiple output              |  |  |  |

| MMC          | Multimedia card                             |  |  |  |

| PC           | Personal computer                           |  |  |  |

| PCI          | Peripheral component interconnect           |  |  |  |

| PCIe         | Peripheral component interconnect express   |  |  |  |

| PCM          | Pulse-code modulation                       |  |  |  |

| SD           | Secure digital                              |  |  |  |

| SDIO         | Secure digital input output                 |  |  |  |

| UART         | Universal asynchronous receiver/transmitter |  |  |  |

| USB          | Universal serial bus                        |  |  |  |

| Wi-Fi        | Wireless local area network                 |  |  |  |

| ZIF          | Zero Insertion Force                        |  |  |  |

|              |                                             |  |  |  |

Table 13: Explanation of the abbreviations and terms used

## Related documents

- [1] JODY-W3 series data sheet, UBX-19010615

- [2] JODY-W3 system integration manual, UBX-19011209

- [3] JODY-W2 level shifter integration application note, UBX-19034257

- [4] EVK-JODY-W3 schematics

- [5] Embedded Linux for i.MX Applications Processors, https://www.nxp.com/design/software/embedded-software/i-mx-software/embedded-linux-for-i-mx-applications-processors:IMXLINUX

- [6] NXP UM11490, Feature Configuration Guide for NXP-based Wireless Modules on i.MX 8M Quad EVK, https://www.nxp.com/docs/en/user-guide/UM11490.pdf

- For product change notifications and regular updates of u-blox documentation, register on our website, www.u-blox.com.

# Revision history

| Revision | Date        | Name | Comments                                                     |

|----------|-------------|------|--------------------------------------------------------------|

| R01      | 9-Jul-2020  | mzes | Initial release.                                             |

| R02      | 2-Nov-2020  | mzes | Minor editorial updates. Released for public distribution.   |

| R03      | 9-Nov-2021  | mzes | Updated for new carrier board revision D.                    |

| RO4      | 17-Nov-2021 | mzes | Revised the max voltage for VDD_USB in Operating conditions. |

## **Contact**

For complete contact information, visit us at www.u-blox.com.

#### u-blox Offices

#### North, Central and South America

#### u-blox America, Inc.

Phone: +1 703 483 3180 E-mail: info\_us@u-blox.com

#### **Regional Office West Coast:**

Phone: +1 408 573 3640 E-mail: info\_us@u-blox.com

#### **Technical Support:**

Phone: +1 703 483 3185 E-mail: support\_us@u-blox.com

#### Headquarters Europe, Middle East, Africa

#### u-blox AG

Phone: +41 44 722 74 44

E-mail: info@u-blox.com

Support: support@u-blox.com

#### Asia, Australia, Pacific

#### u-blox Singapore Pte. Ltd.

Phone: +65 6734 3811

E-mail: info\_ap@u-blox.com

Support: support\_ap@u-blox.com

#### Regional Office Australia:

Phone: +61 3 9566 7255

E-mail: info\_anz@u-blox.com

Support: support\_ap@u-blox.com

#### Regional Office China (Beijing):

Phone: +86 10 68 133 545

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

#### Regional Office China (Chongqing):

Phone: +86 23 6815 1588

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

#### Regional Office China (Shanghai):

Phone: +86 21 6090 4832

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

#### Regional Office China (Shenzhen):

Phone: +86 755 8627 1083

E-mail: info\_cn@u-blox.com

Support: support\_cn@u-blox.com

#### Regional Office India:

Phone: +91 80 405 092 00

E-mail: info\_in@u-blox.com

Support: support\_in@u-blox.com

#### Regional Office Japan (Osaka):

Phone: +81 6 6941 3660

E-mail: info\_jp@u-blox.com

Support: support\_jp@u-blox.com

### Regional Office Japan (Tokyo):

Phone: +81 3 5775 3850 E-mail: info\_jp@u-blox.com Support: support\_jp@u-blox.com

#### Regional Office Korea:

Phone: +82 2 542 0861

E-mail: info\_kr@u-blox.com

Support: support\_kr@u-blox.com

#### Regional Office Taiwan:

Phone: +886 2 2657 1090

E-mail: info\_tw@u-blox.com

Support: support\_tw@u-blox.com