# ML4062-SLB V2.0

# **MSA Compliant 50G**

**QSFP-DD Electrical Passive Loopback Module**

Rev 0.7

# **Table of Contents**

| 1.       | Gen                                 | eral Description5                           |  |  |  |  |  |  |  |

|----------|-------------------------------------|---------------------------------------------|--|--|--|--|--|--|--|

| 2.       | Fun                                 | ctional Description                         |  |  |  |  |  |  |  |

| 2        | 2.1 Management Data Interface – I2C |                                             |  |  |  |  |  |  |  |

| 2        | 2.2                                 | I2C Signals, Addressing and Frame Structure |  |  |  |  |  |  |  |

|          | 2.2.2                               | 1 QSFP-DD Timing Diagram                    |  |  |  |  |  |  |  |

|          | 2.2.2                               | 2 Management Interface Timing Parameters    |  |  |  |  |  |  |  |

|          | 2.2.3                               | 3 Memory Specifications7                    |  |  |  |  |  |  |  |

| 2        | 2.3                                 | Low Speed Electrical Hardware Pins8         |  |  |  |  |  |  |  |

|          | 2.3.                                | 1 ModSelL                                   |  |  |  |  |  |  |  |

|          | 2.3.2                               | 2 ResetL                                    |  |  |  |  |  |  |  |

|          | 2.3.3                               | 3 InitMode                                  |  |  |  |  |  |  |  |

|          | 2.3.4                               | 4 ModPrsL                                   |  |  |  |  |  |  |  |

|          | 2.3.                                | 5 IntL8                                     |  |  |  |  |  |  |  |

| 2        | 2.4                                 | QSFP-DD Memory Map9                         |  |  |  |  |  |  |  |

|          | 2.4.                                | 1 Firmware Revision                         |  |  |  |  |  |  |  |

| 2        | 2.5                                 | ML4062-SLB Specific Functions10             |  |  |  |  |  |  |  |

|          | 2.5.                                | 1 Temperature Monitor                       |  |  |  |  |  |  |  |

|          | 2.5.2                               | 2 Voltage Sense                             |  |  |  |  |  |  |  |

|          | 2.5.3                               | 3 Thermal Loads Mode Select                 |  |  |  |  |  |  |  |

|          | 2.5.4                               | 4 Status and control registers14            |  |  |  |  |  |  |  |

|          | 2.5.                                | 5 Insertion Counter                         |  |  |  |  |  |  |  |

|          | 2.5.0                               | 6 Cut-Off Temperature15                     |  |  |  |  |  |  |  |

|          |                                     | 7 Alarm and warning thresholds15            |  |  |  |  |  |  |  |

|          | 2.5.                                |                                             |  |  |  |  |  |  |  |

| 3.       |                                     | P-DD Pin Allocation                         |  |  |  |  |  |  |  |

| 3.<br>4. | QSF                                 | P-DD Pin Allocation                         |  |  |  |  |  |  |  |

#### ML4062-SLB QSFP-DD 4x28G Passive Loopback Modules – Key Features

- ✓ Supports 8x50G electrical interface

- ✓ QSFP-DD MSA Form Factor

- ✓ Microcontroller can be programmed to maintain user specified PD or constant temperature

- ✓ Built with advanced PCB material

- ✓ 2 Thermistors on PCBA, and two on the shell

- ✓ 4 independent power heathers, with 0.1W resolution, up to 14W

- ✓ Temperature Monitor and alarms warning

- ✓ Superior SI performance

- ✓ MSA Compatible Configuration and EEPROM

- ✓ Loops back TX to RX on all 8 ports

- ✓ I2C Interface

- ✓ Programmable MSA memory pages

- ✓ I2C control from edge connectors and from rear pin header

- ✓ 2 status LED Indicator

- ✓ Insertions counter

- ✓ Hot Pluggable module

- ✓ Cut-off temperature preventing module overheating

- ✓ Controller card with I2C Master, supports multiple modules, USB master

- ✓ Cable assemblies for power & I2C Control

- ✓ Custom memory maps

- ✓ Confirm CDAUI-8 compliance for 56G PAM-4

#### **LED Indicator**

Green (Solid) – Signifies that the module is operating in high power mode.

**Red (Solid)** – Signifies the module is operating in low power mode.

# **Operating Conditions**

| Recommended Operation Conditions |        |                                           |      |     |       |       |

|----------------------------------|--------|-------------------------------------------|------|-----|-------|-------|

| Parameter                        | Symbol | Notes/Conditions                          | Min  | Тур | Max   | Units |

| Operating Temperature            | Тд     |                                           | 0    |     | 85    | °C    |

| Supply Voltage                   | VCC    | Main Supply Voltage                       | 3.00 | 3.3 | 3.5   | V     |

| Input/Output Load<br>Resistance  | RL     | AC-Coupled, Differential                  | 90   | 100 | 110   | Ω     |

| Power Class                      |        | Programmable to Emulate all power classes | 0    |     | 14    | W     |

| Bit Rate                         |        | 28G NRZ<br>56G PAM4                       |      |     | 56.25 | Gbps  |

# **1. General Description**

**QSFP-DD** Passive Loopback Module, **ML4062-SLB**, is used for testing QSFP-DD transceiver ports under board level tests. By substituting a full-featured QSFP-DD transceiver with the ML4062-SLB, its electrical loopback provides a cost effective low loss method for QSFP-DD port testing.

The **ML4062-SLB** is packaged in a standard MSA housing compatible with all QSFP-DD ports. Transmit data from the host is electrically routed, (internal to the loopback module), to the receive data outputs and back to the host. It provides an economical way to exercise QSFP-DD ports during R&D validation, production testing, and field testing.

The **ML4062-SLB** provides 7 power classes using a customer supplied +3.3V voltage supply.

# **2. Functional Description**

#### 2.1 Management Data Interface – I2C

The ML4062 supports the I2C interface. This QSFP-DD datasheet is based on the QSFP-DD specification Rev0.4.

#### 2.2 I2C Signals, Addressing and Frame Structure

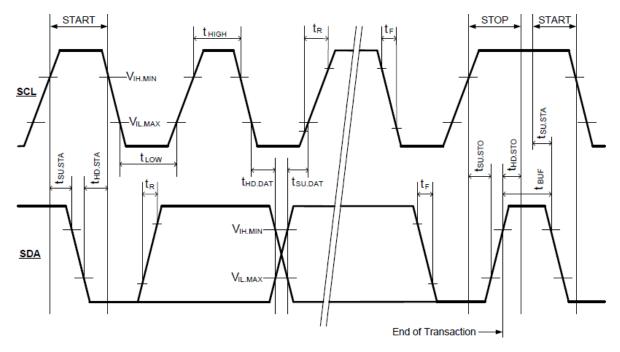

#### 2.2.1 QSFP-DD Timing Diagram

The 2-wire serial interface address of the QSFP-DD module is 1010000X (A0h). In order to allow access to multiple QSFP-DD modules on the same 2-wire serial bus, the QSFP-DD includes a module select pad, ModSelL. This input (which is pulled high, deselected in the module) must be held low by the host to select the module of interest and allow communication over the 2-wire serial interface. The module must not respond to or accept 2-wire serial bus instructions unless it is selected.

Before initiating a 2-wire serial bus communication, the host shall provide setup time on the ModSelL line of all modules on the 2-wire bus. The host shall not change the ModSelL line of any module until the 2-wire serial bus communication is complete and the hold time requirement is satisfied.

## **2.2.2** Management Interface Timing Parameters

The timing parameters for the 2-Wire interface to the QSFP-DD module are shown in the table below.

|                                                 |                | Fast Mode<br>(400 KHz) |     |      |

|-------------------------------------------------|----------------|------------------------|-----|------|

| Parameter                                       | Symbol         | Min                    | Max | Unit |

| Clock Frequency                                 | fSCL           | 0                      | 400 | kHz  |

| Clock Pulse Width Low                           | tLOW           | 1.3                    |     | us   |

| Clock Pulse Width High                          | tHigh          | 0.6                    |     | us   |

| Time bus free before new transmission can start | tBUF           | 20                     |     | us   |

| START Hold Time                                 | tHD.STA        | 0.6                    |     | us   |

| START Set-up Time                               | tSU.STA        | 0.6                    |     | us   |

| Data In Hold Time                               | tHD.DAT        | 0                      |     | us   |

| Data in Setup Time                              | tSU.DAT        | 0.1                    |     | us   |

| Input Rise Time (400kHz)                        | tR.400         |                        | 300 | ns   |

| Input Fall Time (400kHz)                        | tF.400         |                        | 300 | ns   |

| STOP Setup Time                                 | tSU.STO        | 0.6                    |     | us   |

| ModSelL Setup Time                              | tSU.ModSelL    | 2                      |     | ms   |

| ModSelL Hold Time                               | tHD.ModSelL    | 2                      |     | ms   |

| Aborted sequence – bus release                  | Deselect_Abort | 2                      |     | ms   |

#### 2.2.3 Memory Specifications

QSFP-DD memory transaction timings are given in the following table:

| Parameter                                         | Symbol       | Min | Max | Unit   |

|---------------------------------------------------|--------------|-----|-----|--------|

| Serial Interface Clock Holdoff "Clock Stretching" | T_clock_hold |     | 500 | us     |

| Complete Single or Sequential Write               | tWR          |     | 40  | ms     |

| Endurance (Write Cycles)                          |              | 50K |     | cycles |

#### 2.3 Low Speed Electrical Hardware Pins

In addition to the 2-wire serial interface the module has the following low speed pins for control and status:

- ModSelL

- ResetL

- InitMode

- ModPrsL

- IntL

#### 2.3.1 ModSelL

The ModSelL is an input signal that must be pulled to Vcc in the QSFP-DD module. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP-DD modules on a single 2-wire interface bus. When ModSelL is "High", the module shall not respond to or acknowledge any 2-wire interface communication from the host.

#### 2.3.2 ResetL

The ResetL signal shall be pulled to Vcc in the module. A low level on the ResetL signal for longer than the minimum pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default state.

#### 2.3.3 InitMode

InitMode is an input signal. The InitMode signal must be pulled up to Vcc in the QSFP-DD module. The InitMode signal allows the host to define whether the QSFP-DD module will initialize under host software control (InitMode asserted High) or module hardware control (InitMode deasserted Low). Under host software control, the module shall remain in Low Power Mode until software enables the transition to High Power Mode. Under hardware control (InitMode de-asserted Low), the module may immediately transition to High Power Mode after the management interface is initialized.

#### 2.3.4 ModPrsL

ModPrsL must be pulled up to Vcc Host on the host board and grounded in the module. The ModPrsL is asserted "Low" when the module is inserted and deasserted "High" when the module is physically absent from the host connector.

#### 2.3.5 IntL

IntL is an output signal. The IntL signal is an open collector output and must be pulled to Vcc Host on the host board. When the IntL signal is asserted Low it indicates a change in module state, a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL signal is deasserted "High" after all set interrupt flags are read.

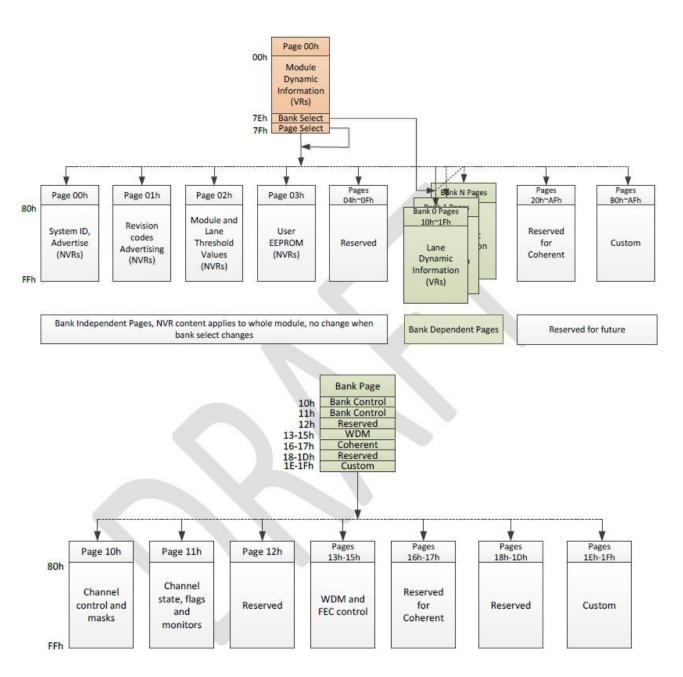

#### 2.4 QSFP-DD Memory Map

QSFP-DD management working draft specification Rev 0.4

Figure 2: QSFP-DD Memory Map

This section defines the Memory Map for QSFP-DD Module used for serial ID, digital monitoring and certain control functions. The interface is mandatory for all QSFP-DD devices.

The structure of the memory is shown in Figure 6. The memory space is arranged into a lower, single page, address space of 128 bytes and multiple upper address space pages. This structure permits timely access to addresses in the lower page, e.g. Interrupt Flags and Monitors. Less time critical entries, e.g. serial ID information and threshold settings, are available with the Page Select function. The structure also provides address expansion by adding additional upper pages as needed. For example, in Figure 6 upper pages 01 and 02 are optional. Upper page 01 allows implementation of Application Select Table, and upper page 02 provides a user read/write space. The lower page and upper page 00 are always implemented. Page 03 is required if byte 2, bit 2 in the lower page is low.

#### 2.4.1 Firmware Revision

The Firmware Revision is shown in the table below, it shows the values in the corresponding registers for the FW V3.2 and FW V3.3:

| Page | Address | Description  | Value in FW V3.2 | Value in updated<br>FW (V3.3) |

|------|---------|--------------|------------------|-------------------------------|

| 1    | 128     | Major FW Rev | 0                | 3                             |

| 1    | 129     | Minor FW Rev | 3                | 3                             |

| 1    | 130     | Major HW Rev | 2                | 4                             |

| 1    | 131     | Minor HW Rev | 0                | 2                             |

#### 2.5 ML4062-SLB Specific Functions

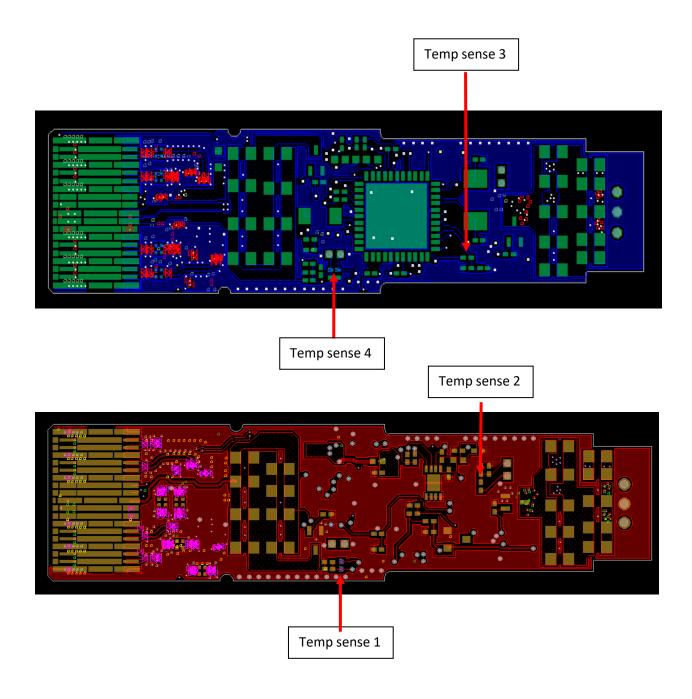

#### 2.5.1 Temperature Monitor

The ML4062-SLB has 4 internal temperature sensors in order to continuously monitor the module's temperature. The temperature sensor readings are present in low-memory registers. Internally measured Module temperature are represented as a 16-bit signed two's complement value in increments of 1/256 degrees Celsius, yielding a total range of -128C to +128C that is considered valid

between –40 and +125C. Temperature accuracy is less than 1 degree Celsius over specified operating temperature and voltage. Please check below for details on the location of temperature sensors.

| c               | Bit | Name            | Description                              |

|-----------------|-----|-----------------|------------------------------------------|

| 12 (lower Page) | ALL | Temperature MSB | Internally measured module temperature 1 |

| 13 (lower Page) | ALL | Temperature LSB | Internally measured module temperature 1 |

| 14 (lower Page) | ALL | Temperature MSB | Internally measured module temperature 2 |

| 15 (lower Page) | ALL | Temperature LSB | Internally measured module temperature 2 |

| 152 Page 3      | ALL | Temperature MSB | Internally measured module temperature 3 |

| 153 Page 3      | ALL | Temperature LSB | Internally measured module temperature 3 |

| 154 page 3      | ALL | Temperature MSB | Internally measured module temperature 4 |

| 155 page 3      | ALL | Temperature LSB | Internally measured module temperature 4 |

#### 2.5.2 Voltage Sense

A voltage sense circuit is available in the ML4062-SLB that allows to measure the internal module supplied voltage Vcc. Supply voltage is represented as a 16-bit unsigned integer with the voltage defined as the full 16-bit value (0 – 65535) with LSB equal to 100 uVolt, yielding a total measurement range of 0 to +6.55 Volts.

| Address         | Bit | Name               | Description                               |

|-----------------|-----|--------------------|-------------------------------------------|

| 16 (lower Page) | ALL | Supply Voltage MSB | Internally measured module Supply Voltage |

| 17 (lower Page) | ALL | Supply Voltage LSB | Internally measured module Supply Voltage |

| 18 (lower Page) | ALL | Not implemented    |                                           |

| 19 (lower Page) | ALL | Not implemented    |                                           |

| 158 Page 3      | ALL | VCCTX sens MSB     | Internally measured module Supply Voltage |

| 159 Page 3      | ALL | VCCTX sens LSB     | Internally measured module Supply Voltage |

| 160 Page 3      | ALL | VCCRX sens MSB     | Internally measured module Supply Voltage |

| 161 Page 3      | ALL | VCCRX sens LSB     | Internally measured module Supply Voltage |

#### 2.5.3 Thermal Loads Mode Select

The thermal loads can be programmed in two modes:

Register 129 of memory page 3 allows to switch between the two modes.

- 1. To maintain user specified power dissipation (bit 0 = 0)

- 2. To maintain a constant temperature (bit 0 = 1)

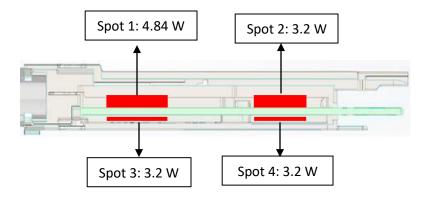

#### 1. Constant Power

Registers 135 to 138 of page 3 are used for PWM control over I2C. These are 8 bit data wide register. The consumed power changes accordingly when the value in this register is changed (only when in high power mode). The values written in this register are permanently stored.

The PWM can also be used for module thermal emulation.

The module contains 4 thermal spots positioned where the optical transceivers usually are in an optical module that is heated relative to the related PWM register. One spot is 4.84 W and three are 3.2 W. The power can be configured with a 0.1 W resolution.

| Address        | Bit | Name                      | Description                                                                |

|----------------|-----|---------------------------|----------------------------------------------------------------------------|

| 135<br>Page 03 | 7:0 | 4.84 W power controller 1 | 4.48 W top power spot control register, powered by P3V3 net                |

| 136<br>Page 03 | 7:0 | 3.2 W power controller 2  | 3.2 W top power spot control register, powered by P3V3_Vcc1 net            |

| 137<br>Page 03 | 7:0 | 3.2 W PWM controller 3    | 3.2 W bottom power spot PWM control register,<br>powered by P3V3_VccTx net |

| 138<br>Page 03 | 7:0 | 3.2 W PWM controller 4    | 3.2 W bottom power spot PWM control register,<br>powered by P3V3_VccRx net |

In the figure below, the red spots represents the 4 thermal spots on the module.

#### 2. Constant Temperature

The module can be programmed to maintain a constant temperature. Register 130 of memory page 3 is used to set the desired temperature.

Two modes are available, Average module temperature to be maintained, or maintain temperature for a defined temp sense spot

| Address        | Bit | Name               | Description                                                        |

|----------------|-----|--------------------|--------------------------------------------------------------------|

| 130<br>Page 03 | 7:0 | Target temperature | Target Temperature to be maintained by the module,<br>LSB = 1 degC |

| 131<br>Page 03 | 0   | Mode Select        | 0 = Average Temp ; 1=Selected Spot Temp                            |

| 131<br>Page 03 | 7:4 | Spot Select        | Number of temp sense spot                                          |

#### **2.5.4 Status and control registers**

Register 139 of Page 3 reports the digital state of the QSFP-DD low speed signals and controls IntL pin.

| Address       | Bit | Name          | Description                 |

|---------------|-----|---------------|-----------------------------|

| 139 (Page 3)  | 0   | ModSel        | Digital state of ModSel pin |

| 139(Page 3)   | 1   | InitMode      | Digital state of InitMode   |

| 139(Page 3)   | 4   | IntL          | Assert/Deassert IntL pin    |

| 132 (Page 16) | 0   | DataPathPwrUp | Enable Tx and Rx data path  |

#### 2.5.5 Insertion Counter

The Insertion counter contains the number of times the module was plugged in a host. The insertion counter is incremented every time the module goes in initializing sequence, as it is nonvolatile it is always saved, and can be read anytime from registers 132 and 133 of memory page 3.

| Address     | Bit | Name                  | Description            |

|-------------|-----|-----------------------|------------------------|

| 132(Page 3) | ALL | Insertion Counter MSB | LSB unit = 1 insertion |

| 133(Page 3) | ALL | Insertion Counter LSB |                        |

#### 2.5.6 Cut-Off Temperature

To avoid overheating the module, a Cut-Off Temperature is pre-defined.

The module is continuously monitoring the temperature and checking its value against the Cut-Off temperature. Once the module temperature reaches the cut-off temperature, the PWM will automatically turn off in order to prevent overheating. Once the temperature is 5 degrees below cut-off value, the PWM goes back to its previous value.

The Cut-Off temperature for the ML4062-SLB is 85°C and it can be programmed to any value from register 134 of memory page 3.

| Address     | Bit | Name                | Description                              |

|-------------|-----|---------------------|------------------------------------------|

| 134(Page 3) | 7:0 | Cut-Off temperature | Module Cut-Off Temperature, LSB = 1 degC |

#### **2.5.7** Alarm and warning thresholds

Each A/D quantity has a corresponding high alarm, low alarm, high warning and low warning threshold. These factory preset values allow the user to determine when a particular value is outside of "normal" limits. While Voltage LSB unit is 100  $\mu$ V and Temperature LSB unit is 1/256 °C. Note that these addresses are of memory Page 02.

| Address     | Bit | Name                              | Default Value |  |

|-------------|-----|-----------------------------------|---------------|--|

| 128(Page 2) | ALL | high temp alarm threshold (MSB)   | 80°C          |  |

| 129(Page 2) | ALL | high temp alarm threshold (LSB)   |               |  |

| 130(Page 2) | ALL | low temp alarm threshold (MSB)    | СС            |  |

| 131(Page 2) | ALL | low temp alarm threshold (LSB)    |               |  |

| 132(Page 2) | ALL | high temp warning threshold (MSB) | 75°C          |  |

| 133(Page 2) | ALL | high temp warning threshold (LSB) |               |  |

| 134(Page 2) | ALL | low temp warning threshold (MSB)  | 5°C           |  |

| 135(Page 2) | ALL | low temp warning threshold (LSB)  |               |  |

| 144(Page 2) | ALL | high volt alarm threshold (MSB)   | 3.6 V         |  |

| 145(Page 2) | ALL | high volt alarm threshold (LSB)   |               |  |

| 146(Page 2) | ALL | low volt alarm threshold (MSB)    | 3.0 V         |  |

| 147(Page 2) | ALL | low volt alarm threshold (LSB)    |               |  |

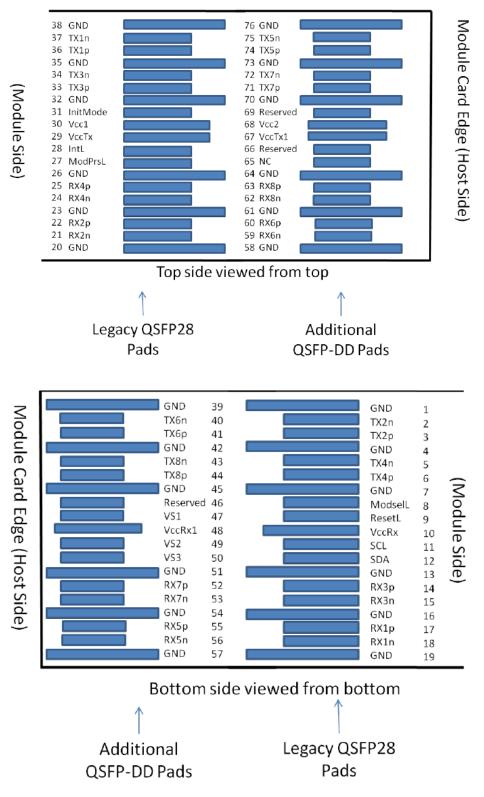

# 3. **QSFP-DD Pin Allocation**

Figure 3: QSFP-DD Module Pad Layout

# 4. Appendix

## 4.1 Major FW upgrades

Major upgrades in FW V3.3 are listed below:

- 1. Updated Temperature monitoring accuracy

- 2. Updated FW and HW Revision values in the corresponding registers

#### **Revision History**

| Revision number | Date       | Description                                                                                                                                                            |

|-----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1             | 16/05/2017 | Preliminary                                                                                                                                                            |

| 0.2             | 17/05/2017 | <ul> <li>Compliant with MSA rev2.0</li> </ul>                                                                                                                          |

| 0.3             | 6/6/2017   | <ul> <li>Removed Read/Write functionality parag</li> <li>Removed Device addressing and operation parag</li> <li>Updated parag 2.2, 2.5.1, 2.5.3 and parag 3</li> </ul> |

| 0.4             |            | <ul> <li>Fixed typo in parag 2.1</li> </ul>                                                                                                                            |

| 0.5             | 27/11/2017 | <ul> <li>Compliant with QSFP-DD specs 0.4 (updated parag 2.4 and 2.5)</li> </ul>                                                                                       |

| 0.6             | 13/02/2018 | <ul> <li>memory mapping updated (parag 2.5)</li> </ul>                                                                                                                 |

| 0.7             | 2/4/2019   | <ul> <li>add FW revision (Parag 2.4.1)</li> <li>Register 18-19 not implemented (parag 2.5.2)</li> <li>add Appendix for major FW upgrades(parag 4.1)</li> </ul>         |

#### North America

48521 Warm Springs Blvd. Suite 310 Fremont, CA 94539 USA +1 510 573 6388

#### Worldwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 5 941 668

#### Asia

14F-5/ Rm.5, 14F., No 295 Sec.2, Guangfu Rd. East Dist., Hsinchu City 300, Taiwan (R.O.C) +886 3 5744 591