# MINIATURE FIBER OPTIC MEMS SWITCH

# **OVERVIEW**

The *SX* series are miniature opto-mechanical switches for fiber optic communication systems and submodules. The switch is available in latching variants, with 1x1, 2x1, 2x2, The switch offers smallest size, ease of integration and the established reliability of Sercalo's MEMS components.

The package is one of the smallest in the industry. It is optimized for low cost production while maintaining high reliability. The component meets Telcordia 1221 quality standards. It is compliant to RoHS requirements 2015/863/E.

### **FEATURES**

- 23 x 10 x 6 mm size

- TTL or CMOS logic

- Latching

- 2x2, 2x1, 1x1 variants

- Single or multimode fiber

# **APPLICATIONS**

- Protection Switching

- Reconfiguration

- Optical Subsystems

- Array integration

### Contact

Sercalo Microtechnology Ltd.

Landstrasse 151, FL 9494 Schaan

Fürstentum Liechtenstein

Tel. +423 237 57 97 Fax. +423 237 57 48

www.sercalo.com Email: info@sercalo.com

### **DESCRIPTION**

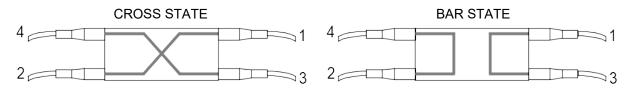

In the SX switches the optical switching function is realised by a silicon MEMS chip, on which a mirror can be moved in and out of the optical path by electrostatic actuation. The miniature SX switch is available as latching variant where a bistable suspension mechanism keeps the last selected state in power off. The non-latching type (i.e. SXNA) is not recommended for new designs.

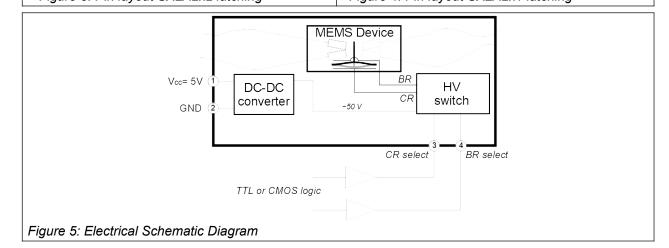

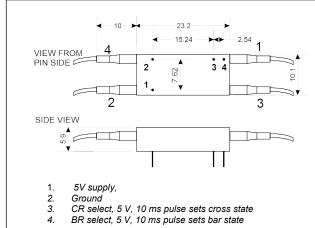

To operate the switch 5V and 0V are applied on pins 1 and 2, which are used by the internal DC-DC converter to supply a high voltage for the actuator control. CMOS or TTL logic levels on pins 3-4 control the electrostatic actuator. To set the switch state pin 3 respectively pin 4 are set to logic high (5V) for 20 ms and the corresponding switch state is selected. At rest pins 3 and 4 should be pulled to 0 V and must not be floating.

|                                 | Unit   | Min  | Тур               | Max   |

|---------------------------------|--------|------|-------------------|-------|

| Switch                          |        |      |                   |       |

| Wavelength Range <sup>1</sup>   | nm     | 1240 |                   | 1640  |

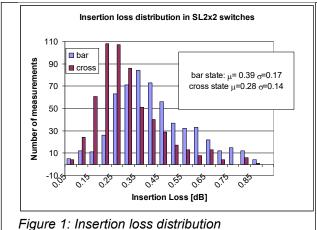

| Insertion Loss <sup>2</sup>     | dB     |      | 0.4               | 1.0   |

| Crosstalk <sup>1</sup>          | dB     |      | 75                | 60    |

| Return Loss <sup>1</sup>        | dB     |      | 55                | 40    |

| Polarisation Dependent Loss     | dB     |      | 0.03              | 0.07  |

| Repeatability <sup>3</sup>      | dB     |      |                   | 0.002 |

| Switching Time <sup>1</sup>     | ms     |      | 2                 | 10    |

| Durability                      | cycles |      | 10^9              |       |

| ntegrated Driver                |        |      |                   |       |

| Supply Voltage Vcc (pin 1)      | V      | 3.2  | 3.3 or 5          | 5.25  |

| Current Consumption Icc (pin 1) | mA     |      | 1                 | 45    |

| Logic Level Low (pins 3, 4)     | V      |      |                   | 0.3   |

| Logic Level High (pins 3, 4)    | V      | 3.0  |                   |       |

| Selection Pulse Width           | ms     | 10   | 20                |       |

| Package                         |        |      |                   |       |

| Operation Temperature           | °C     | 0    |                   | 70    |

| Storage Temperature             | °C     | -40  |                   | 85    |

| Size (L x W x H) – for single   | mm     |      | 23.2 x 10.1 x 6.0 |       |

<sup>&</sup>lt;sup>1</sup> **for multimode**: range: 600 – 1700 nm; IL @ 1300 nm: <1.0 dB max; CT max: >40 dB; RL max: 35 dB; resp. time: <20ms. <sup>2</sup>value @ 25 °C, without connectors. <sup>3</sup>for constant temperature and polarisation.

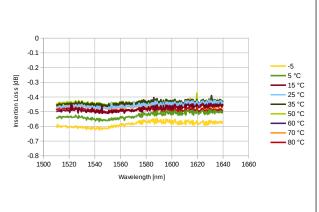

Figure 2: spectral response over temperature

Figure 3: Pin layout SXLA2x2 latching

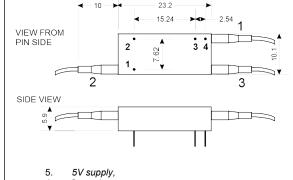

- Ground

- 6. 7. CR select, 5 V, 10 ms pulse sets cross state BR select, 5 V, 10 ms pulse sets bar state

- Figure 4: Pin layout SXLA2x1 latching