# Multi Output Clock Generator with Integrated 2.0GHz VCO AK8186B

#### **FEATURES**

- Low phase noise PLL: RMS Jitter < 300fs

- On-chip VCO tunes from 1.75GHz to 2.25GHz

- External VCO/VCXO to 500MHz optional

- 1 differential or 2 single-ended Inputs

- Reference Switchover/Holdover modes

- Lock Detect

- 3 pairs of 1GHz LVPECL outputs

- 2 pairs of 800MHz LVDS outputs

- 8 250MHz CMOS outputs (two per LVDS)

- Serial control register interface

- 3.3V+/-5% Operating Voltage

- 2.5V-3.3V LVPECL Drive Voltage

- Operating Temperature: -40 to +85°C

- Package: 64-pin Leadless QFN (Pb free)

- Pin compatible with AD9516-3

#### DESCRIPTION

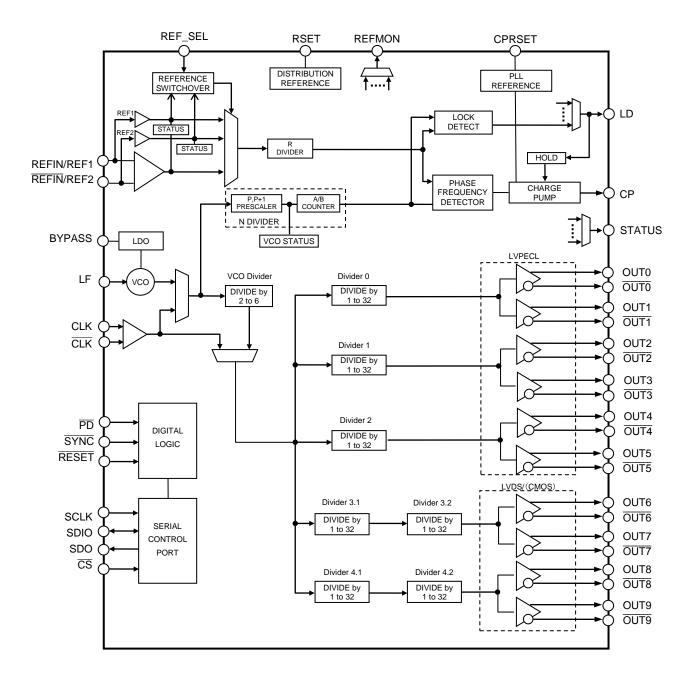

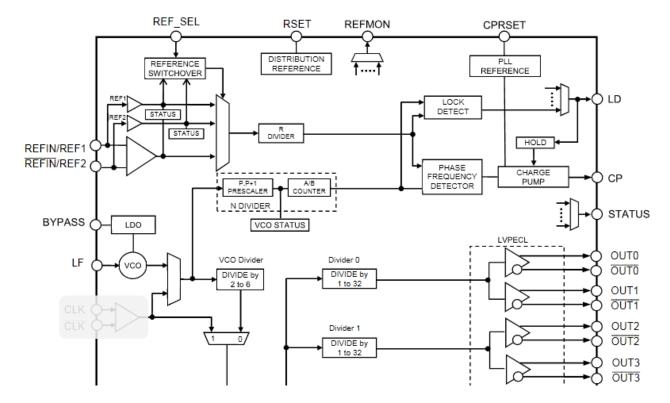

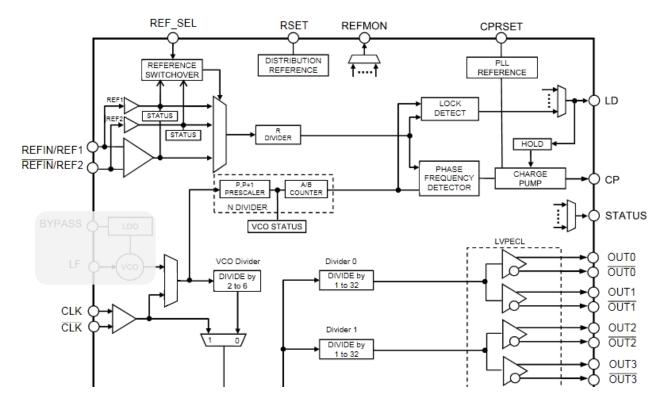

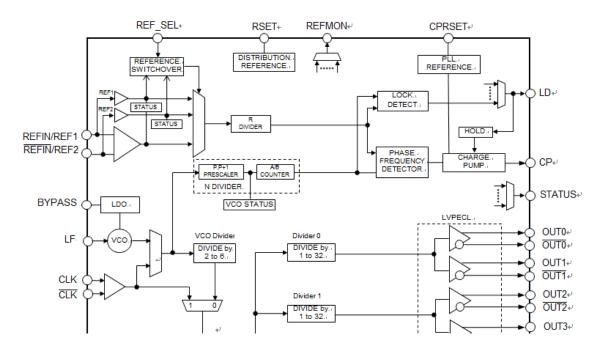

The AK8186B is a multi-output clock generator with sub-ps jitter performance. The on-chip VCO tunes from 1.75GHz to 2.25GHz.

The distribution section has three pairs of LVPECL buffers (6 outputs) and two pairs of LVDS buffers (4 outputs)/eight CMOS buffers (two per LVDS outputs). The LVPECL outputs operate up to 1GHz, the LVDS outputs operate up to 800MHz and the CMOS outputs operate up to 250MHz.

Each pair of the outputs has a divider. The LVPECL outputs have the division range of 1 to 32. The LVDS and CMOS outputs have the 1 to 1024.

The AK8186B operates at 3.3V and the LVPECL outputs are supplied independently from 2.375V to 3.6V. The operating temperature range is from -40 to +85°C. The part is available in a 9mm 9 mm 64-pin Leadless-QFN (Pb free) package.

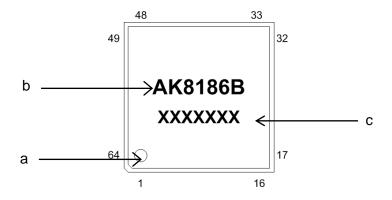

#### ORDERING INFORMATION

| Part Number | Marking | Shipping<br>Packaging | Package                | Temperature<br>Range |

|-------------|---------|-----------------------|------------------------|----------------------|

| AK8186B     | AK8186B | Tape and Reel         | 64-pin<br>Leadless QFN | -40 to 85 °C         |

# **BLOCK DIAGRAM**

Figure 1. AK8186B Block Diagram

# **TABLE OF CONTENTS**

| FEATURES                |                                   | - 1 - |

|-------------------------|-----------------------------------|-------|

| DESCRIPTION             |                                   | - 1 - |

| ORDERING INFORMATIO     | N                                 | - 1 - |

| BLOCK DIAGRAM           |                                   | - 2 - |

| PIN DESCRIPTION         |                                   | - 4 - |

| PIN CONFIGURATION       |                                   | - 4 - |

| PIN FUNCTION            |                                   | - 5 - |

| ABSOLUTE MAXIMUM RA     | ATING                             | - 7 - |

| RECOMMENDED OPERAT      | ING CONDITIONS                    | - 7 - |

| ELECTRICAL CHARACTERI   | STICS                             | - 7 - |

| Power Dissipation       |                                   | - 7 - |

|                         |                                   |       |

|                         | TICS                              |       |

|                         | RISTICS                           |       |

|                         |                                   |       |

| CLOCK OUTPUT ADDITIVE P | HASE NOISE (DISTRIBUTION ONLY; VO | co    |

|                         |                                   |       |

| CLOCK OUTPUT PHASE NOI  | se (Internal VCO Used)            | 13 -  |

|                         | TIME JITTER (CLOCK GENERATION USI |       |

| INTERNAL VCO)           |                                   | 14 -  |

| CLOCK OUTPUT ABSOLUTE   | TIME JITTER (CLOCK GENERATION USI | NG    |

| EXTERNAL VCXO)          |                                   | 14 -  |

| CLOCK OUTPUT ADDITIVE T | IME JITTER (VCO DIVIDER NOT USED  | )     |

| 15 -                    |                                   |       |

| CLOCK OUTPUT ADDITIVE T | IME JITTER (VCO DIVIDER USED)     | 15 -  |

| SERIAL CONTROL PORT     |                                   | 16 -  |

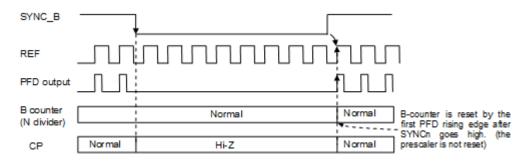

| PD, SYNC AND RESET      |                                   | 17 -  |

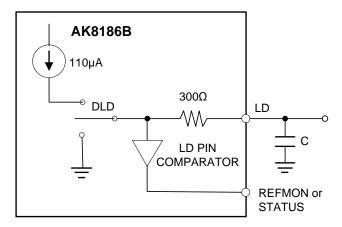

| LD, STATUS AND REFMO    | DN                                | 17 -  |

| TIMING DIAGRAMS         |                                   | 18 -  |

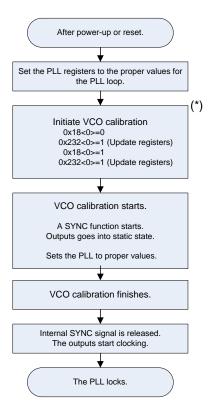

| THEORY OF OPERATION .   |                                   | 19 -  |

|                         | URATIONS                          |       |

|                         |                                   |       |

|                         | ock Distribution                  |       |

|                         | lock Distribution                 |       |

|                         |                                   |       |

|                         |                                   |       |

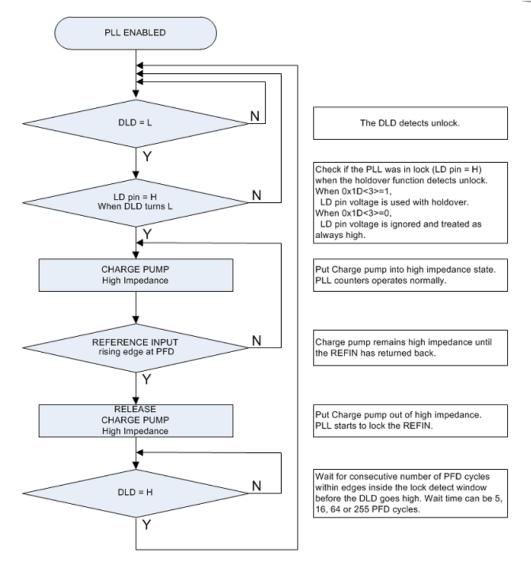

|                         | HOVER                             |       |

|                         | NCE DIVIDER)                      |       |

|                         | DETECTOR (PFD)                    |       |

|                         | ····                              |       |

| ·                       |                                   |       |

|                         |                                   |       |

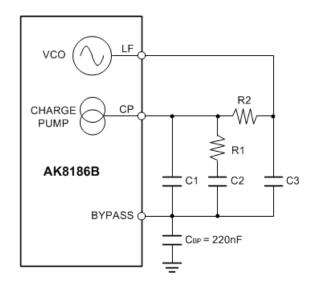

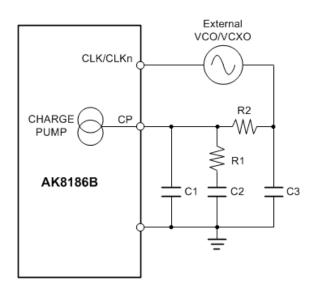

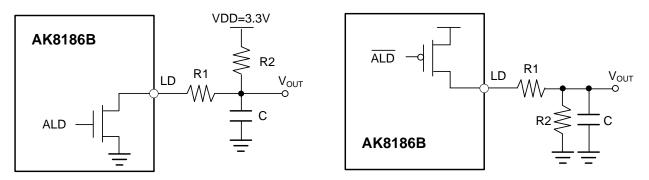

|                         | P FILTER                          | 24 -  |

| · ·                     | of External Loop Filter for the   |       |

| Internal VCO            | Figure 13 Example of External     |       |

| Loop Filter for an External VCO                                                                                                                                                                                                                                                                                          |                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                          | 24 -                                                                 |

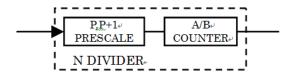

| FEEDBACK DIVIDER (N DIVIDER)                                                                                                                                                                                                                                                                                             | 24 -                                                                 |

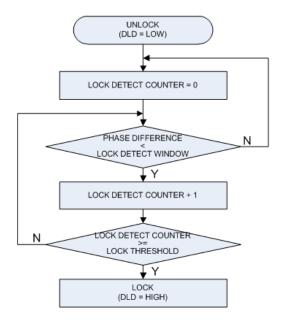

| LOCK DETECT                                                                                                                                                                                                                                                                                                              | 26 -                                                                 |

| HOLDOVER                                                                                                                                                                                                                                                                                                                 | 28 -                                                                 |

| Frequency Status Monitors                                                                                                                                                                                                                                                                                                | 30 -                                                                 |

| CLOCK DISTRIBUTION                                                                                                                                                                                                                                                                                                       | 31 -                                                                 |

| VCO DIVIDER                                                                                                                                                                                                                                                                                                              | 31 -                                                                 |

| Channel Dividers for LVPECL OUTPUTS                                                                                                                                                                                                                                                                                      | 31 -                                                                 |

| Channel Dividers for LVDS/CMOS OUTPUTS                                                                                                                                                                                                                                                                                   | 31 -                                                                 |

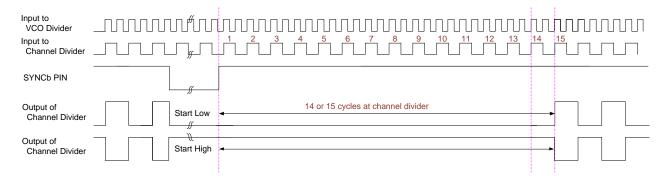

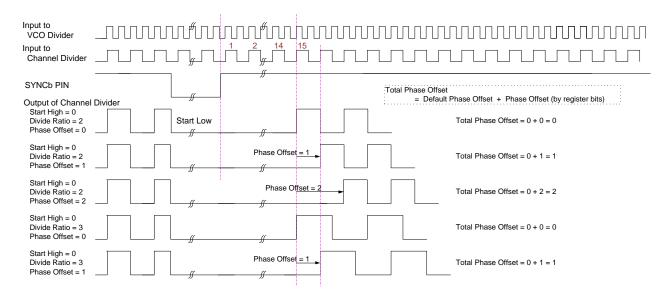

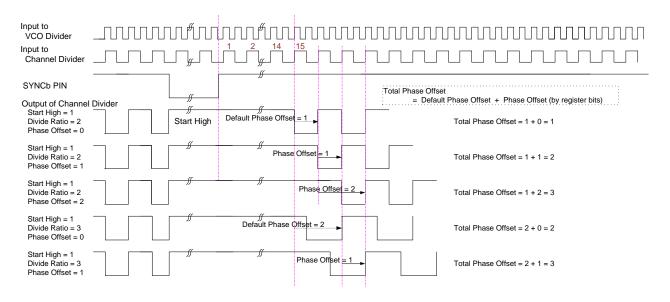

| Synchronizing the Outputs: SYNC FUNCTION                                                                                                                                                                                                                                                                                 | 32 -                                                                 |

| Phase Offset                                                                                                                                                                                                                                                                                                             | 32 -                                                                 |

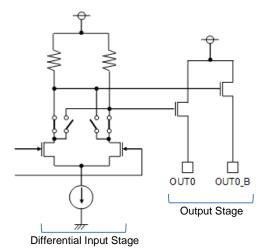

| LVPECL OUTPUTS : OUT0 to OUT5                                                                                                                                                                                                                                                                                            | 34 -                                                                 |

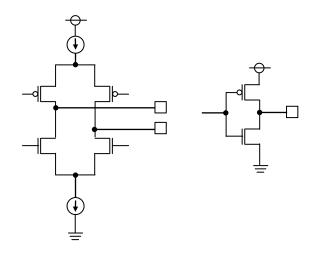

| LVDS/CMOS OUTPUTS: OUT6 to OUT9                                                                                                                                                                                                                                                                                          |                                                                      |

| RESET                                                                                                                                                                                                                                                                                                                    |                                                                      |

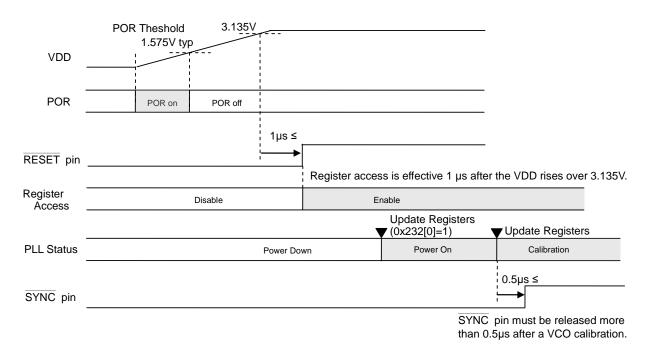

| Power-on reset (POR)                                                                                                                                                                                                                                                                                                     |                                                                      |

| Asynchronous reset by RESET pin                                                                                                                                                                                                                                                                                          |                                                                      |

| Soft reset by 0x00[5]                                                                                                                                                                                                                                                                                                    |                                                                      |

| POWER DOWN MODES                                                                                                                                                                                                                                                                                                         |                                                                      |

| Chip Power Down by PDn pin                                                                                                                                                                                                                                                                                               |                                                                      |

| PLL Power Down                                                                                                                                                                                                                                                                                                           |                                                                      |

| REF1, REF2 Power Down                                                                                                                                                                                                                                                                                                    |                                                                      |

| VCO and CLK Input Power Down                                                                                                                                                                                                                                                                                             |                                                                      |

| Distribution Power Down                                                                                                                                                                                                                                                                                                  |                                                                      |

| Individual Clock Output Power Down (OUT0 to                                                                                                                                                                                                                                                                              |                                                                      |

| 37 -                                                                                                                                                                                                                                                                                                                     | •                                                                    |

| SERIAL CONTROL PORT                                                                                                                                                                                                                                                                                                      | 38 -                                                                 |

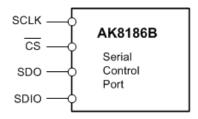

| SERIAL CONTROL PORT PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                     | 38 -                                                                 |

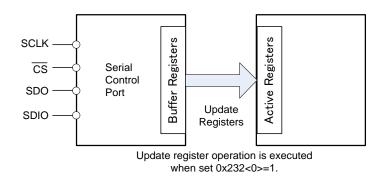

| GENERAL DESCRIPTION OF SERIAL CONTROL PO                                                                                                                                                                                                                                                                                 | ORT- 38                                                              |

| -                                                                                                                                                                                                                                                                                                                        |                                                                      |

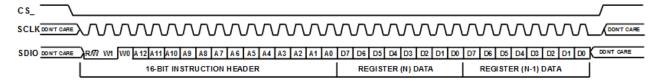

| Communication Cycle                                                                                                                                                                                                                                                                                                      | - 38 -                                                               |

|                                                                                                                                                                                                                                                                                                                          | 50                                                                   |

| The Instruction Word (16 bits)                                                                                                                                                                                                                                                                                           |                                                                      |

| The Instruction Word (16 bits) WRITE                                                                                                                                                                                                                                                                                     | 39 -                                                                 |

|                                                                                                                                                                                                                                                                                                                          | 39 -<br>39 -                                                         |

| WRITE                                                                                                                                                                                                                                                                                                                    | 39 -<br>39 -<br>40 -                                                 |

| WRITE<br>READ                                                                                                                                                                                                                                                                                                            | 39 -<br>39 -<br>40 -<br>40 -                                         |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS                                                                                                                                                                                                                                                                           | 39 -<br>39 -<br>40 -<br>40 -<br>41 -                                 |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS                                                                                                                                                                                                                                                  | 39 -<br>39 -<br>40 -<br>41 -<br>43 -                                 |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS                                                                                                                                                                                                | 39 -<br>39 -<br>40 -<br>41 -<br>43 -<br>46 -                         |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP                                                                                                                                                                                                                                    | 39 -<br>39 -<br>40 -<br>40 -<br>41 -<br>43 -<br>46 -                 |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration                                                                                                                                                                     | 39 -<br>39 -<br>40 -<br>41 -<br>43 -<br>46 -<br>46 -                 |

| WRITE                                                                                                                                                                                                                                                                                                                    | 39 -<br>40 -<br>40 -<br>41 -<br>43 -<br>46 -<br>47 -<br>56 -         |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs                                                                                                                                  | 39 -<br>39 -<br>40 -<br>41 -<br>43 -<br>46 -<br>47 -<br>56 -<br>58 - |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs                                                                                                               | 39 39 40 41 43 46 47 56 58 60 -                                      |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs.  LVPECL Channel Dividers.                                                                                    | 39 39 40 41 43 46 47 56 58 60 62 -                                   |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs  LVPECL Channel Dividers  LVDS/CMOS Channel Dividers                                                          | 39 39 40 41 43 46 46 56 58 60 62 64 -                                |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs.  LVPECL Channel Dividers.  VCO Divider and CLK Input                                                         | 39 39 40 41 46 46 56 58 62 65 -                                      |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs  LVPECL Channel Dividers  LVDS/CMOS Channel Dividers  VCO Divider and CLK Input  System  Update All Registers | 39 39 40 41 43 46 56 58 60 65 65 -                                   |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS.  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs.  LVPECL Channel Dividers.  LVDS/CMOS Channel Dividers  VCO Divider and CLK Input.  System                   | 39 39 40 41 43 46 56 58 60 65 65 -                                   |

| WRITE  READ  BUS STALLING IN READ/WRITE ACCESS  MSB/LSB FIRST TRANSFERS  REGISTER MAP  REGISTER MAP FUNCTION DESCRIPTIONS  Serial Port Configuration  PLL Configuration  LVPECL Outputs  LVDS/CMOS Outputs  LVPECL Channel Dividers  LVDS/CMOS Channel Dividers  VCO Divider and CLK Input  System  Update All Registers | 39 39 40 40 41 43 46 56 65 66 -                                      |

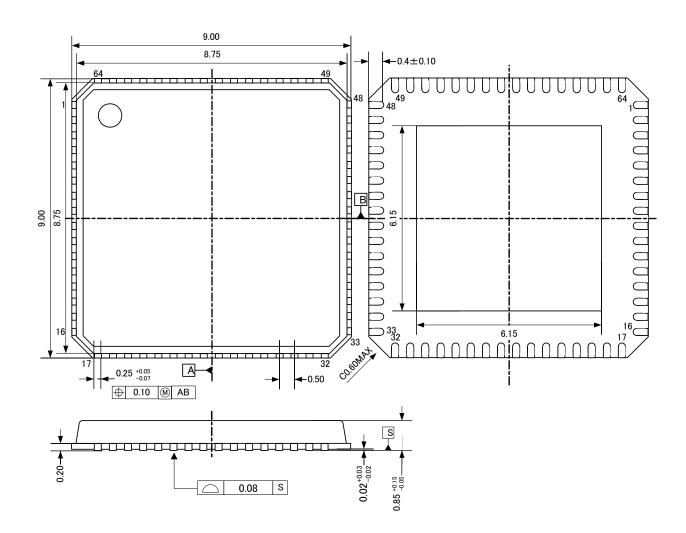

## PIN DESCRIPTION

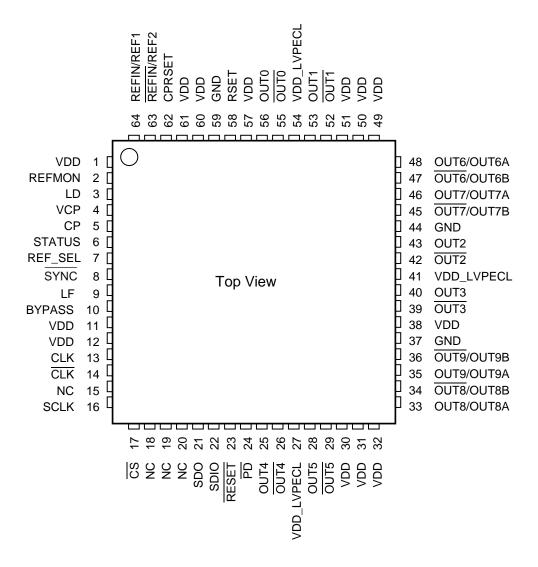

## **PIN CONFIGURATION**

Figure 2. Pin Configuration

# **PIN FUNCTION**

| Pin<br>No. | Pin Name   | Pin<br>Type | Description                                                                                                |

|------------|------------|-------------|------------------------------------------------------------------------------------------------------------|

| 1          | VDD        | PWR         | 3.3V Power Supply.                                                                                         |

| 2          | REFMON     | OUT         | Reference Monitor.                                                                                         |

| 3          | LD         | OUT         | Lock Detect.                                                                                               |

| 4          | VCP        |             | 3.3V Power Supply for Charge Pump (CP)                                                                     |

| 5          | CP         | OUT         | Charge Pump Output. Connect to external loop filter.                                                       |

| 6          | STATUS     | OUT         | Status Indication.                                                                                         |

| 7          | REF_SEL    | IN          | Reference Select. L: REF1 H: REF2. Pulled down with 30k $\Omega$ internal resistor.                        |

| 8,         | SYNC       | IN          | Manual Synchronization and Manual Holdover. Active Low. Pulled up with 30 k $\Omega$ internal resistor.    |

| 9          | LF         | IN          | Loop Filter Input.                                                                                         |

| 10         | BYPASS     |             | This pin is for bypassing the LDO to ground.                                                               |

| 11         | VDD        | PWR         | 3.3V Power supply.                                                                                         |

| 12         | VDD        | PWR         | 3.3V Power supply.                                                                                         |

| 13         | CLK        |             | Differential Input for the external VCO/VCXO                                                               |

| 14         | CLK        |             | Differential Input for the external VCO/VCXO                                                               |

| 15         | NC         |             | No Connect. Leave open or connected to GND.                                                                |

| 16         | SCLK       | IN          | Serial clock for the Serial control port. Pulled down with 30k $\Omega$ internal resistor.                 |

| 17         | CS         | IN          | Chip Select for the Serial control port. Active low. Pulled up to VDD with 30 $k\Omega$ internal resistor. |

| 18         | NC         |             | No Connect. Leave open or connected to GND.                                                                |

| 19         | NC         |             | No Connect. Leave open or connected to GND.                                                                |

| 20         | NC         |             | No Connect. Leave open or connected to GND.                                                                |

| 21         | SDO        | OUT         | Unidirectional Serial Data Out for Serial Control Port.                                                    |

| 22         | SDIO       | IN/OUT      | Bidirectional Serial Data In/Out for Serial Control Port.                                                  |

| 23         | RESET      | IN          | Reset. Active low. Pulled up with 30 k $\Omega$ internal resistor.                                         |

| 24         | PD         | IN          | Power Down. Active low. Pulled up with 30 k $\Omega$ internal resistor.                                    |

| 25         | OUT4       | OUT         | LVPECL Output 4                                                                                            |

| 26         | OUT4       | OUT         | LVPECL Output 4                                                                                            |

| 27         | VDD_LVPECL | PWR         | 2.5V to 3.3V Power Supply for LVPECL Output (OUT4/OUT4, OUT5/OUT5).                                        |

| 28         | OUT5       | OUT         | LVPECL Output 5                                                                                            |

| 29         | OUT5       | OUT         | LVPECL Output 5                                                                                            |

| 30         | VDD        | PWR         | 3.3V Power supply                                                                                          |

| 31         | VDD        | PWR         | 3.3V Power supply.                                                                                         |

| 32         | VDD        | PWR         | 3.3V Power supply for OUT8/OUT8 and OUT9/OUT9.                                                             |

(Continued on next page)

| Pin<br>No. | Pin Name       | Pin<br>Type | Description                                                                          |

|------------|----------------|-------------|--------------------------------------------------------------------------------------|

| 33         | OUT8/OUT8A     | OUT         | LVDS/CMOS Output 8                                                                   |

| 34         | OUT8/OUT8B     | OUT         | LVDS/CMOS Output 8                                                                   |

| 35         | OUT9/OUT9A     | OUT         | LVDS/CMOS Output 9                                                                   |

| 36         | OUT9/OUT9B     | OUT         | LVDS/CMOS Output 9                                                                   |

| 37         | GND            | PWR         | Ground. Includes External Pad (EPAD).                                                |

| 38         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 39         | OUT3           | OUT         | LVPECL Output 3                                                                      |

| 40         | OUT3           | OUT         | LVPECL Output 3                                                                      |

| 41         | VDD_LVPECL     | PWR         | 2.5V to 3.3V Power Supply for LVPECL Output (OUT2/OUT2, OUT3/OUT3).                  |

| 42         | OUT2           | OUT         | LVPECL Output 2                                                                      |

| 43         | OUT2           | OUT         | LVPECL Output 2                                                                      |

| 44         | GND            | PWR         | Ground. Includes External Pad (EPAD).                                                |

| 45         | OUT7/OUT7B     | OUT         | LVDS/CMOS Output 7                                                                   |

| 46         | OUT7/OUT7A     | OUT         | LVDS/CMOS Output 7                                                                   |

| 47         | OUT6/OUT6B     | OUT         | LVDS/CMOS Output 6                                                                   |

| 48         | OUT6 /OUT6A    | OUT         | LVDS/CMOS Output 6                                                                   |

| 49         | VDD            | PWR         | 3.3V Power supply for OUT6/OUT6 and OUT7/OUT7.                                       |

| 50         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 51         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 52         | OUT1           | OUT         | LVPECL Output 1                                                                      |

| 53         | OUT1           | OUT         | LVPECL Output 1                                                                      |

| 54         | VDD_LVPECL     | PWR         | 2.5V to 3.3V Power Supply for LVPECL Output (OUT0/OUT0, OUT1/OUT1).                  |

| 55         | OUT0           | OUT         | LVPECL Output 0                                                                      |

| 56         | OUT0           | OUT         | LVPECL Output 0                                                                      |

| 57         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 58         | RSET           |             | Internal bias current control. Nominal value = $4.12$ k $\Omega$                     |

| 59         | GND            | PWR         | Ground.                                                                              |

| 60         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 61         | VDD            | PWR         | 3.3V Power supply.                                                                   |

| 62         | CPRSET         |             | Charge pump current control. Nominal value = $5.1 k\Omega$                           |

| 63         | REFIN<br>/REF2 | IN          | Differential input for the PLL reference. Alternatively single-ended input for REF2. |

| 64         | REFIN<br>/REF1 | IN          | Differential input for the PLL reference. Alternatively single-ended input for REF1. |

| EPAD       | GND            | PWR         | Ground. The EPAD is connected with other GND pins.                                   |

## ABSOLUTE MAXIMUM RATING

Table 1 Over operating free-air temperature range unless otherwise noted (1)

| Items                              | Symbol | Min     | Max     | Unit |  |

|------------------------------------|--------|---------|---------|------|--|

| Supply voltage(VDD,VDD_LVPECL,VCP) | VDD    | -0.3    | 4.3     | V    |  |

| Input voltage                      | VIN    | GND-0.3 | VDD+0.3 | V    |  |

| Input Current                      | IIN    | -10     | 10      | mA   |  |

| Storage temperature                | Tstg   | -55     | 125     | °C   |  |

(1) Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

**ESD Sensitive Device**

This device is manufactured on a CMOS process, therefore, generically susceptible to damage by excessive

static voltage. Failure to observe proper handling and installation procedures can cause damage. AKM recommends that this device is handled with appropriate precautions.

## RECOMMENDED OPERATING CONDITIONS

Table 2

|                       | 1          |                    | 1     |      |       |      |

|-----------------------|------------|--------------------|-------|------|-------|------|

| Parameter             | Symbol     | Conditions         | Min   | Тур  | Max   | Unit |

| Operating temperature | Та         |                    | -40   |      | 85    | °C   |

| Committee on (1)      | VDD, VCP   |                    | 3.135 | 3.3  | 3.465 | V    |

| Supply voltage (1)    | VDD_LVPECL |                    | 2.375 |      | VDD V | V    |

| RSET Pin Resistor     | Rr         | Connect to GND.    | 4.08  | 4.12 | 4.16  | kΩ   |

| CPRSET Pin Resistor   | Rc         | Connect to GND.    | 4.3   | 5.1  | 6.2   | kΩ   |

| BYPASS Pin Capacitor  | Свр        | Connect to VCOGND. |       | 220  |       | nF   |

<sup>(1)</sup> Power of 2.5V or 3.3V requires to be supplied from a single source. A decoupling capacitor of  $0.1\mu F$  for power supply line should be located close to each VDD pin.

## **ELECTRICAL CHARACTERISTICS**

## **Power Dissipation**

Table 3

| Parameter        | Symbol | Conditions | Min | Тур | Max  | Unit |

|------------------|--------|------------|-----|-----|------|------|

| Power on default | PD1    | *1         |     | 0.4 | 0.52 | W    |

| Full Operation   | PD2    | *2         |     | 1.6 | 2.0  | W    |

| Full Operation   | PD3    | *3         |     | 1.4 | 1.7  | W    |

| Power Down       | PD4    |            |     |     | 0.4  | mW   |

<sup>(\*1)</sup>No clock input. Default register values. Not include power dissipation in external resistors.

<sup>(\*2)</sup> REF1/REF2=246.575MHz, Rdiv=16, Ndiv=146, VCO=2.25GHz, VCO div=2, LVPECL=562.5MHz, CMOS(10pF load)=225MHz. Not include power dissipation in external resistors.

<sup>(\*3)</sup> REF1/REF2=246.575MHz, Rdiv=16, Ndiv=146, VCO=2.25GHz, VCO div=2, LVPECL=562.5MHz, LVDS=225MHz. Not include power dissipation in external resistors.

# **PLL Characteristics**

Table 4. All specifications at VDD= $3.3V\pm5\%$ , VDD\_LVPECL=2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                                                                                                               | Conditions                                                | Min            | Тур            | Max               | Unit              |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------|----------------|-------------------|-------------------|

| On Chip VCO Frequency Range                                                                                             |                                                           | 1750           |                | 2250              | MHz               |

| VCO Gain                                                                                                                | Fvco=2.25GHz<br>Fvco=1.97GHz<br>Fvco=1.75GHz              | 18<br>16<br>14 | 67<br>52<br>41 | 146<br>128<br>114 | MHz/V             |

| Tuning Voltage                                                                                                          |                                                           | 1.0            |                | 2.5               | V                 |

| Frequency Pushing                                                                                                       | Open Loop                                                 | -5             |                | 5                 | MHz/V             |

| Phase Noise@100kHz Offset<br>Phase Noise@1MHz Oddset                                                                    | Fvco=2.00GHz<br>Fvco=2.00GHz                              |                | -105<br>-130   |                   | dBc/Hz<br>dBc/Hz  |

| Reference Inputs (Differential Mode) Input Frequency                                                                    | REFIN, REFINn Below 1MHz should be dc-coupled             | 0              |                | 250               | MHz               |

| Input Duty                                                                                                              |                                                           | 40             |                | 60                | %                 |

| Input Sensitivity(AC-Couple)                                                                                            |                                                           | 200            |                |                   | mVpp              |

| Input Slew Rate                                                                                                         |                                                           | 0.2            |                |                   | V/ns              |

| Self-Bias Voltage,REFIN<br>Self-Bias Voltage,REFINn                                                                     |                                                           | 1.35<br>1.3    | 1.6<br>1.5     | 1.75<br>1.7       | V<br>V            |

| Input Resistance,REFIN Input Resistance,REFINn                                                                          |                                                           | 3.3<br>3.7     | 4.8<br>5.3     | 6.2<br>6.9        | kΩ<br>kΩ          |

| Reference Inputs (Single-Ended Mode) Input Frequency(AC-Couple) Input Frequency(DC-Couple) Input Sensitivity(AC-Couple) | REF1, REF2                                                | 20<br>0<br>0.6 |                | 250<br>250        | MHz<br>MHz<br>Vpp |

| Input Duty                                                                                                              | at VDD/2                                                  | 40             |                | 60                | %                 |

| Input Slew Rate                                                                                                         |                                                           | 0.2            |                |                   | V/ns              |

| Input Logic HIgh<br>Input Logic Low                                                                                     |                                                           | 2.0            |                | 0.8               | V<br>V            |

| Input Logic Current                                                                                                     |                                                           | -100           |                | +100              | μА                |

| INPUT Capacitance                                                                                                       | REFIN/REF1, REFINn/REF2                                   |                | 5              |                   | pF                |

| Phase Frequency Detector PFD Input Frequency Antibacklash Pulse Width                                                   |                                                           |                | 1.4            | 100               | MHz<br>ns         |

| Charge Pump                                                                                                             |                                                           |                |                |                   |                   |

| Icp Sink/Source High Value Low Value                                                                                    | Programmable CPRSET=5.1kΩ, VCP=3.3V, CP =1.65V, Temp=25°C | 4.32<br>0.54   | 4.8<br>0.60    | 5.28<br>0.66      | mA<br>mA          |

| Icp Leakage                                                                                                             | CP = 0.5 to VCP-0.5V                                      | -1             |                | +1                | μA                |

| Sink/Source Matching *1                                                                                                 | CP = 0.5 to VCP-0.5V                                      | -10            | 2.2            | +10               | %                 |

| Icp vs Vcp *2                                                                                                           | CP = 0.5 to VCP-0.5V                                      | -8             | 3.6            | +8                | %                 |

| Icp vs Temperature                                                                                                      | CP = 0.5*VCP                                              | -5             |                | +5                | %                 |

| Parameter                         | Conditions                               | Min | Тур  | Max  | Unit      |

|-----------------------------------|------------------------------------------|-----|------|------|-----------|

| Prescaler (Part of N divider)     |                                          |     |      |      |           |

| Prescaler Input Frequency         |                                          |     |      |      |           |

| P = 1 FD                          | 1E1[1]=0                                 |     |      | 300  | MHz       |

| P = 2 FD                          | 1E1[1]=0                                 |     |      | 500  | MHz       |

| P = 3 FD                          | 1E1[1]=0                                 |     |      | 500  | MHz       |

| P = 2 DM (2/3)                    | 1E1[1]=0                                 |     |      | 500  | MHz       |

| P = 4 DM (4/5)                    | 1E1[1]=0                                 |     |      | 500  | MHz       |

| P = 8 DM (8/9)                    | 1E1[1]=0 or 1                            |     |      | 2250 | MHz       |

| P = 16 DM (16/17)                 | 1E1[1]=0 or 1                            |     |      | 2250 | MHz       |

| P = 32 DM (32/33)                 | 1E1[1]=0 or 1                            |     |      | 2250 | MHz       |

| Prescaler Output Frequency        | A,B counter input.                       |     |      | 300  | MHz       |

| Noise Characteristics             |                                          |     |      |      |           |

| In-Band Phase Noise of the Charge | @500 kHz PFD Frequency                   |     | -169 |      | dBc/Hz    |

| Pump/Phase Frequency Detecter     | @1MHz PFD Frequency                      |     | -166 |      | dBc/Hz    |

| , ,                               | @10MHz PFD Frequency                     |     | -155 |      | dBc/Hz    |

|                                   | @50MHz PFD Frequency                     |     | -147 |      | dBc/Hz    |

| PLL Figure of Merit (FOM)         | FOM                                      |     | -226 |      | dBc/Hz    |

|                                   | = Phase Noise - 10log(f <sub>PFD</sub> ) |     |      |      | 0.20/1.12 |

|                                   | - 20log(Ndiv) + 20log(Odiv);             |     |      |      |           |

|                                   | where Ndiv = N divider ratio, Odiv =     |     |      |      |           |

|                                   | VCO divider ratio * Channel divider      |     |      |      |           |

|                                   | ratio.                                   |     |      |      |           |

| PLL Digital Lock Detect Window    |                                          |     |      |      |           |

| Required to Lock                  | 0x18[4] = 1                              |     | 3.5  |      | ns        |

| ·                                 | 0x18[4] = 0                              |     | 7.5  |      | ns        |

| To Unlock After Lock (Hysteresis) | 0x18[4] = 1                              |     | 7    |      | ns        |

|                                   | 0x18[4] = 0                              |     | 15   |      | ns        |

<sup>\*1) [(|</sup>Isink|-|Isource|)/{(|Isink|+|Isource|)/2}] \* 100 [%]

# **Clock Input Characteristics**

Table 5.

| Parameter                       | Conditions                                    | Min | Тур  | Max | Unit |

|---------------------------------|-----------------------------------------------|-----|------|-----|------|

| CLOCK INPUTS (CLK, CLK)         |                                               |     |      |     |      |

| Input Frequency                 | Below 1MHz should be dc-coupled.              | 0   |      | 500 | MHz  |

| Input Sensitivity, Differential |                                               |     | 150  |     | mVpp |

| Input Level, Differential       |                                               |     |      | 2   | Vpp  |

| Input Common-Mode Voltage, Vcm  |                                               | 1.3 | 1.57 | 1.8 | V    |

| Input Common-Mode Range, Vcm    | With 200mVpp signal applied. dc-coupled       | 1.3 |      | 1.8 | V    |

| Input Sensitivity, Single-Ended | CLK ac-coupled, CLK ac-bypassed to RF ground. |     | 150  |     | mVpp |

| Input Resistance                | Self-biased                                   | 3.2 | 4.7  | 6.1 | kΩ   |

| Input Capacitance               |                                               |     | 2    |     | pF   |

<sup>\*2) (|</sup>I1-I2|)/(|I1+I2|/2)\*100 [%]

# **Clock Output Characteristics**

Table 6. All specifications at VDD=3.3V±5%, VDD\_LVPECL= 2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                   | Symbol | Conditions                                                                                                       | Min                 | Тур                 | Max                 | Unit |

|-----------------------------|--------|------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| LVPECL CLOCK OUTPUT         |        | Vterm = $50\Omega$ to                                                                                            |                     |                     |                     |      |

| Output Frequency            |        | VDD_LVPECL-2V                                                                                                    |                     |                     | 1000                | MHz  |

| Output High Voltage(VOH)    |        | 0xFn[3:2] = 00 (n=0 to 5)<br>0xFn[3:2] = 01 (n=0 to 5)<br>0xFn[3:2] = 10 (n=0 to 5)<br>0xFn[3:2] = 11 (n=0 to 5) | VDD_LVPECL<br>-1.23 | VDD_LVPECL<br>-0.98 | VDD_LVPECL<br>-0.73 | V    |

| Output High Voltage(VOL)    |        | 0xFn[3:2] = 00 (n=0 to 5)                                                                                        | VDD_LVPECL<br>-1.67 | VDD_LVPECL<br>-1.38 | VDD_LVPECL<br>-1.10 |      |

|                             |        | 0xFn[3:2] = 01 (n=0 to 5)                                                                                        | VDD_LVPECL<br>-1.86 | VDD_LVPECL<br>-1.58 | VDD_LVPECL<br>-1.31 |      |

|                             |        | 0xFn[3:2] = 10 (n=0 to 5)                                                                                        | VDD_LVPECL<br>-2.03 | VDD_LVPECL<br>-1.77 | VDD_LVPECL<br>-1.49 | V    |

|                             |        | 0xFn[3:2] = 11 (n=0 to 5)                                                                                        | VDD_LVPECL<br>-2.20 | VDD_LVPECL<br>-1.94 | VDD_LVPECL<br>-1.65 |      |

| Differential Output Voltage |        | 0xFn[3:2] = 00 (n=0 to 5)                                                                                        | 250                 | 400                 | 550                 |      |

|                             |        | 0xFn[3:2] = 01 (n=0 to 5)                                                                                        | 430                 | 600                 | 770                 |      |

|                             |        | 0xFn[3:2] = 10 (n=0 to 5)                                                                                        | 550                 | 790                 | 980                 | mV   |

|                             |        | 0xFn[3:2] = 11 (n=0 to 5)                                                                                        | 740                 | 960                 | 1180                |      |

| LVDS CLOCK OUTPUT           |        |                                                                                                                  |                     |                     |                     |      |

| Output Frequency Maximum    |        |                                                                                                                  |                     |                     | 800                 | MHz  |

| Differential Output Voltage |        | 0x14n[2:1] = 00 (n=0 to 3)                                                                                       | 124                 | 180                 | 227                 |      |

|                             |        | 0x14n[2:1] = 01 (n=0 to 3)                                                                                       | 247                 | 360                 | 454                 | mV   |

|                             |        | 0x14n[2:1] = 10 (n=0 to 3)                                                                                       | 186                 | 270                 | 340                 |      |

|                             |        | 0x14n[2:1] = 11 (n=0 to 3)                                                                                       | 247                 | 360                 | 454                 |      |

| Delta V <sub>OD</sub>       |        | 0x14n[2:1] = 01 (n=0 to 3)                                                                                       |                     |                     | 25                  | mV   |

| Output Offset Voltage       |        | 0x14n[2:1] = 01 (n=0 to 3)                                                                                       | 1.125               | 1.24                | 1.375               | V    |

| Delta V <sub>OD</sub>       |        | 0x14n[2:1] = 01 (n=0 to 3)                                                                                       |                     |                     | 25                  | mV   |

| Short-Circuit Current       |        | 0x14n[2:1] = 01 (n=0 to 3)<br>Output shorted to GND.                                                             |                     | 3.5                 | 24                  | mA   |

| CMOS CLOCK OUTPUTS          |        |                                                                                                                  |                     |                     |                     |      |

| Output Frequency Maximum    |        | load=10pF                                                                                                        |                     |                     | 250                 | MHz  |

| Output High Voltage(VOH)    |        | Ioh=1mA                                                                                                          | VDD-0.2             |                     |                     | V    |

| Output High Voltage(VOL)    |        | lol=1mA                                                                                                          |                     |                     | 0.2                 | V    |

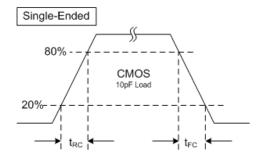

# **Timing Characteristics**

Table 7. All specifications at VDD=3.3V±5%, VDD\_LVPECL= 2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                                                               | Symbol | Conditions                                                                                                                  | MIN                        | TYP                        | MAX                        | Unit             |

|-------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------|

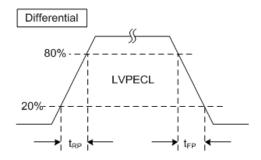

| LVPECL Output                                                           |        | Termination = 50Ω to VDD-LVPECL-2V 0xFn[3:2] = 10 (n=0 to 5)                                                                |                            |                            |                            |                  |

| Rise/Fall time                                                          |        | 20% to 80% / 80% to 20%                                                                                                     |                            | 175                        | 225                        | ps               |

| Propagation Delay, CLK-to-LVPECL Ouput Variation with Temperature       |        |                                                                                                                             |                            | TBD<br>TBD                 |                            | ns<br>ps/°C      |

| Output Skew *1                                                          |        | Same Divider Different Dividers                                                                                             |                            | 5<br>13                    | 40<br>40                   | ps<br>ps         |

| Output Duty                                                             |        | 750MHz ≤ Fout<br>500M ≤ Fout < 750MHz<br>250M ≤ Fout < 500MHz *2<br>Fout < 250MHz *2 *3<br>Fout<1000MHz, VDD_LVPECL=3.3V±5% | 30<br>35<br>40<br>45<br>45 | 50<br>50<br>50<br>50<br>50 | 70<br>65<br>60<br>55<br>55 | %<br>%<br>%<br>% |

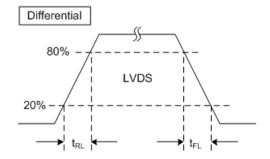

| LVDS Output  Rise/Fall time                                             |        | Termination = $100\Omega$ @3.5mA<br>0x14n[2:1] = 01 (n=0 to 3)<br>20% to $80%$ / $80%$ to $20%$                             |                            | 190                        | 350                        | ps               |

| Propagation Delay, CLK-to-LVPECL Ouput Variation with Temperature       |        | For All Device Values                                                                                                       |                            | TBD<br>TBD                 | 330                        | ns<br>ps/°C      |

| Output Skew *1                                                          |        | Same Divider Different Dividers                                                                                             |                            | 6<br>25                    | 62<br>150                  | ps<br>ps         |

| Output Duty                                                             |        | *2 *3                                                                                                                       | 45                         | 50                         | 55                         | %                |

| CMOS Output Rise/Fall time                                              |        | 20% to 80% / 80% to 20%<br>Cload = 10pF                                                                                     |                            | 400                        | 1000                       | ps               |

| Propagation Delay,<br>CLK-to-LVPECL Ouput<br>Variation with Temperature |        | For All Device Values                                                                                                       |                            | TBD<br>TBD                 |                            | ns<br>ps/°C      |

| Output Skew *1                                                          |        | Same Divider Different Dividers                                                                                             |                            | 4<br>28                    | 66<br>180                  | ps<br>ps         |

| Output Duty                                                             |        | *2 *3                                                                                                                       | 45                         | 50                         | 55                         | %                |

<sup>\*1)</sup> Skew: The Difference between any two similar delay paths while operating at the same voltage and temperature.

<sup>\*2)</sup> Differential input through CLK/ $\overline{\text{CLK}}$  pins: Clock input is assumed to be 50% duty.

<sup>\*3)</sup> Single-end input through CLK pin: Clock input is assumed to be 50% duty and Fout < 150 MHz.

# Clock Output Additive Phase Noise (Distribution Only; VCO Divider Not Used)

Table 8. All specifications at VDD=3.3V±5%, VDD\_LVPECL= 2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                          | Min | Тур  | Max | Unit   | Test Conditions/Comments     |

|------------------------------------|-----|------|-----|--------|------------------------------|

| CLK-TO-LVPECL Additive Phase Noise |     |      |     |        | Does not include PLL and VCO |

| CLK=500MHz, Output=500MHz,         |     |      |     |        | Input slew rate > 1 V/ns     |

| Divider=1                          |     |      |     |        |                              |

| At 1 kHz Offset                    |     | -108 |     | dBc/Hz |                              |

| At 10 kHz Offset                   |     | -130 |     | dBc/Hz |                              |

| At 100 kHz Offset                  |     | -142 |     | dBc/Hz |                              |

| At 1 MHz Offset                    |     | -149 |     | dBc/Hz |                              |

| At 10 MHz Offset                   |     | -150 |     | dBc/Hz |                              |

| CLK=500MHz, Output=250MHz,         |     |      |     |        | Input slew rate > 1 V/ns     |

| Divider=2                          |     |      |     |        |                              |

| At 1 kHz Offset                    |     | -114 |     | dBc/Hz |                              |

| At 10 kHz Offset                   |     | -133 |     | dBc/Hz |                              |

| At 100 kHz Offset                  |     | -143 |     | dBc/Hz |                              |

| At 1 MHz Offset                    |     | -151 |     | dBc/Hz |                              |

| At 10 MHz Offset                   |     | -152 |     | dBc/Hz |                              |

| CLK-TO-LVDS Additive Phase Noise   |     |      |     |        | Does not include PLL and VCO |

| CLK=500MHz, Output=500MHz,         |     |      |     |        | Input slew rate > 1 V/ns     |

| Divider=1                          |     |      |     |        |                              |

| At 1 kHz Offset                    |     | -106 |     | dBc/Hz |                              |

| At 10 kHz Offset                   |     | -126 |     | dBc/Hz |                              |

| At 100 kHz Offset                  |     | -141 |     | dBc/Hz |                              |

| At 1 MHz Offset                    |     | -145 |     | dBc/Hz |                              |

| At 10 MHz Offset                   |     | -147 |     | dBc/Hz |                              |

| CLK=500MHz, Output=250MHz,         |     |      |     |        | Input slew rate > 1 V/ns     |

| Divider=2                          |     |      |     |        |                              |

| At 1 kHz Offset                    |     | -114 |     | dBc/Hz |                              |

| At 10 kHz Offset                   |     | -133 |     | dBc/Hz |                              |

| At 100 kHz Offset                  |     | -143 |     | dBc/Hz |                              |

| At 1 MHz Offset                    |     | -150 |     | dBc/Hz |                              |

| At 10 MHz Offset                   |     | -152 |     | dBc/Hz |                              |

| Parameter                               | Min | Тур  | Max | Unit   | Test Conditions/Comments     |

|-----------------------------------------|-----|------|-----|--------|------------------------------|

| CLK-TO-CMOS Additive Phase Noise        |     |      |     |        | Dose not include PLL and VCO |

| CLK=500MHz, Output=250MHz,<br>Divider=2 |     |      |     |        | Input slew rate > 1 V/ns     |

| At 1 kHz Offset                         |     | -113 |     | dBc/Hz |                              |

| At 10 kHz Offset                        |     | -135 |     | dBc/Hz |                              |

| At 100 kHz Offset                       |     | -143 |     | dBc/Hz |                              |

| At 1 MHz Offset                         |     | -149 |     | dBc/Hz |                              |

| At 10 MHz Offset                        |     | -152 |     | dBc/Hz |                              |

| CLK=500MHz, Output=50MHz,<br>Divider=10 |     |      |     |        | Input slew rate > 1 V/ns     |

| At 1 kHz Offset                         |     | -129 |     | dBc/Hz |                              |

| At 10 kHz Offset                        |     | -139 |     | dBc/Hz |                              |

| At 100 kHz Offset                       |     | -149 |     | dBc/Hz |                              |

| At 1 MHz Offset                         |     | -156 |     | dBc/Hz |                              |

| At 10 MHz Offset                        |     | -160 |     | dBc/Hz |                              |

# **Clock Output Phase Noise (Internal VCO Used)**

Table 9. All specifications at VDD= $3.3V\pm5\%$ , VDD\_LVPECL=2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                       | Min | Тур  | Max | Unit   | Test Conditions/Comments                |

|---------------------------------|-----|------|-----|--------|-----------------------------------------|

| LVPECL Phase Noise              |     |      |     |        | through VCO divider and channel divider |

| Fvco=2.24256GHz, Fout=280.32MHz |     |      |     |        |                                         |

| At 1 kHz Offset                 |     | -94  |     | dBc/Hz | REF=122.88MHz                           |

| At 10 kHz Offset                |     | -103 |     | dBc/Hz |                                         |

| At 100 kHz Offset               |     | -105 |     | dBc/Hz |                                         |

| At 1 MHz Offset                 |     | -125 |     | dBc/Hz |                                         |

| At 10 MHz Offset                |     | -135 |     | dBc/Hz |                                         |

| At 40 MHz Offset                |     | -136 |     | dBc/Hz |                                         |

| Fvco=1.96608GHz, Fout=245.76MHz |     |      |     |        |                                         |

| At 1 kHz Offset                 |     | -89  |     | dBc/Hz | REF=122.88MHz                           |

| At 10 kHz Offset                |     | -102 |     | dBc/Hz |                                         |

| At 100 kHz Offset               |     | -106 |     | dBc/Hz |                                         |

| At 1 MHz Offset                 |     | -127 |     | dBc/Hz |                                         |

| At 10 MHz Offset                |     | -136 |     | dBc/Hz |                                         |

| At 40 MHz Offset                |     | -137 |     | dBc/Hz |                                         |

| Fvco=1.75104GHz, Fout=218.88MHz |     |      |     |        |                                         |

| At 1 kHz Offset                 |     | -96  |     | dBc/Hz | REF=122.88MHz                           |

| At 10 kHz Offset                |     | -105 |     | dBc/Hz |                                         |

| At 100 kHz Offset               |     | -108 |     | dBc/Hz |                                         |

| At 1 MHz Offset                 |     | -129 |     | dBc/Hz |                                         |

| At 10 MHz Offset                |     | -137 |     | dBc/Hz |                                         |

| At 40 MHz Offset                |     | -138 |     | dBc/Hz |                                         |

# **Clock Output Absolute Time Jitter (Clock Generation Using Internal VCO)**

Table 10.

| Parameter                          | Min | Тур | Max | Unit   | Test Conditions/Comments       |

|------------------------------------|-----|-----|-----|--------|--------------------------------|

| LVPECL Output Absolute Time Jitter |     |     |     |        | Internal VCO; through dividers |

| Fvco=1.96608GHz, Fout=245.76MHz    |     |     |     |        | REF=122.88MHz, PLL BW=140kHz   |

|                                    |     | 156 |     | fs rms | 200kHz to 10MHz                |

|                                    |     | 284 |     | fs rms | 12kHz to 20MHz                 |

| Fvco=1.96608GHz, Fout=122.88MHz    |     |     |     |        | REF=122.88MHz, PLL BW=140kHz   |

|                                    |     | 169 |     | fs rms | 200kHz to 10MHz                |

|                                    |     | 293 |     | fs rms | 12kHz to 20MHz                 |

| Fvco=1.96608GHz, Fout=61.44MHz     |     |     |     |        | REF=122.88MHz, PLL BW=140kHz   |

|                                    |     | 193 |     | fs rms | 200kHz to 10MHz                |

|                                    |     | 325 |     | fs rms | 12kHz to 20MHz                 |

# **Clock Output Absolute Time Jitter (Clock Generation Using External VCXO)**

Table 11.

| Parameter                            | Min | Тур | Max | Unit   | Test Conditions/Comments         |

|--------------------------------------|-----|-----|-----|--------|----------------------------------|

| LVDECL Output Absolute Time litter   |     |     |     |        | External VCXO:                   |

| LVPECL Output Absolute Time Jitter   |     |     |     |        | Reference = 15.36MHz, R=1        |

| LVPECL=245.76MHz, PLLBW=125Hz        |     |     |     | fs rms | Integration BW = 200kHz to 5MHz  |

|                                      |     | TBD |     | fs rms | Integration BW = 200kHz to 10MHz |

|                                      |     |     |     | fs rms | Integration BW = 12kHz to 20MHz  |

| LVPECL=122.88MHz, PLLBW=125Hz        |     |     |     | fs rms | Integration BW = 200kHz to 5MHz  |

| 2V1 202=122.00W12, 1 223V1=120112    |     | TBD |     | fs rms | Integration BW = 200kHz to 10MHz |

|                                      |     |     |     | fs rms | Integration BW = 12kHz to 20MHz  |

| LVPECL=61.44MHz, PLLBW=125Hz         |     |     |     | fs rms | Integration BW = 200kHz to 5MHz  |

| 2V1 202-01.7-1VII 12, 1 225V2-125V12 |     | TBD |     | fs rms | Integration BW = 200kHz to 10MHz |

|                                      |     |     |     | fs rms | Integration BW = 12kHz to 20MHz  |

# **Clock Output Additive Time Jitter (VCO Divider Not Used)**

Table 12

| Parameter                          | Min | Тур | Max | Unit   | Test Conditions/Comments  |

|------------------------------------|-----|-----|-----|--------|---------------------------|

| LVPECL Output Additive Time Jitter |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=500MHz,Divider=1 |     | 39  |     | fs rms | 12kHz to 20MHz            |

| CLK=500MHz,Output=250MHz,Divider=2 |     | 92  |     | fs rms | 12kHz to 20MHz            |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 137 |     | fs rms | 12kHz to 20MHz            |

| LVDS Output Additive Time Jitter   |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=500MHz,Divider=1 |     | 76  |     | fs rms | 12kHz to 20MHz            |

| CLK=500MHz,Output=250MHz,Divider=2 |     | 92  |     | fs rms | 12kHz to 20MHz            |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 237 |     | fs rms | 12kHz to 20MHz            |

| CMOS Output Additive Time Jitter   |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 131 |     | fs rms | 12kHz to 20MHz            |

# **Clock Output Additive Time Jitter (VCO Divider Used)**

Table 13

| Parameter                          | Min | Тур | Max | Unit   | Test Conditions/Comments  |

|------------------------------------|-----|-----|-----|--------|---------------------------|

| LVPECL Output Additive Time Jitter |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 129 |     | fs rms | 12kHz to 20MHz            |

| LVDS Output Additive Time Jitter   |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 219 |     | fs rms | 12kHz to 20MHz            |

| CMOS Output Additive Time Jitter   |     |     |     |        | Distribution Section Only |

| CLK=500MHz,Output=100MHz,Divider=5 |     | 120 |     | fs rms | 12kHz to 20MHz            |

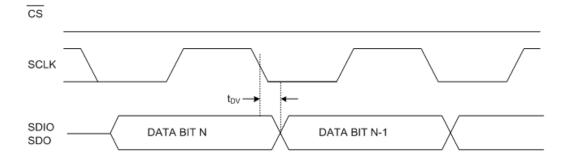

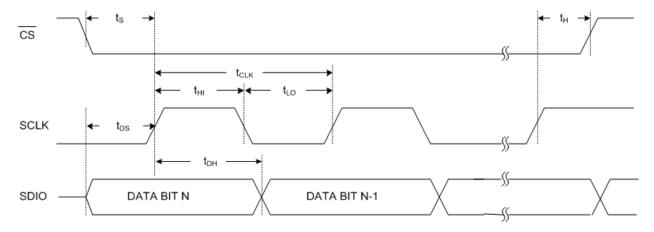

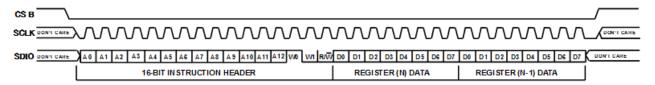

## **Serial Control Port**

Table 14. All specifications at VDD=3.3V±5%, VDD\_LVPECL= 2.375V to VDD, Ta: -40 to +85°C, unless otherwise noted

| Parameter                   | Symbol               | Conditions                           | MIN | TYP | MAX | Unit |

|-----------------------------|----------------------|--------------------------------------|-----|-----|-----|------|

| CS (INPUT)                  | -                    | internal 30kΩ pull-up resistor       |     |     |     |      |

| Input High Level Voltage    | V <sub>IH</sub>      |                                      | 2.0 |     |     | V    |

| Input Low Level Voltage     | V <sub>IL</sub>      |                                      |     |     | 0.8 | V    |

| Input High Level Current    | I <sub>IH</sub>      |                                      | -3  |     | 3   | μА   |

| Input Low Level Current     | I <sub>IL</sub>      |                                      | 45  | 110 | 220 | μА   |

| Input Capacitance           | C <sub>IN</sub>      |                                      |     | 5   |     | pF   |

| SCLK (INPUT)                |                      | internal 30kΩ pull-down resistor     |     |     |     |      |

| Input High Level Voltage    | V <sub>IH</sub>      |                                      | 2.0 |     |     | V    |

| Input Low Level Voltage     | V <sub>IL</sub>      |                                      |     |     | 0.8 | V    |

| Input High Level Current    | I <sub>IH</sub>      |                                      | 45  | 110 | 220 | μА   |

| Input Low Level Current     | I <sub>IL</sub>      |                                      | -3  |     | 3   | μА   |

| Input Capacitance           | C <sub>IN</sub>      |                                      |     | 5   |     | pF   |

| SDIO (INPUT)                |                      |                                      |     |     |     |      |

| Input High Level Voltage    | V <sub>IH</sub>      |                                      | 2.0 |     |     | V    |

| Input Low Level Voltage     | V <sub>IL</sub>      |                                      |     |     | 0.8 | V    |

| Input High Level Current    | I <sub>IH</sub>      |                                      | -3  |     | 3   | μА   |

| Input Low Level Current     | I <sub>IL</sub>      |                                      | -3  |     | 3   | μА   |

| Input Capacitance           | C <sub>IN</sub>      |                                      |     | 11  |     | pF   |

| SDIO, SDO (OUTPUT)          |                      |                                      |     |     |     |      |

| High Level Output Voltage   | V <sub>OHS</sub>     | SDO,SDIO(OUT), I <sub>OH</sub> =-1mA | 2.7 |     |     | V    |

| Low level Output Voltage    | V <sub>OLS</sub>     | SDO,SDIO(OUT) , I <sub>OL</sub> =1mA |     |     | 0.4 | V    |

| TIMING                      |                      | Load=100pF                           |     |     |     |      |

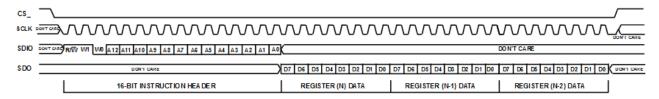

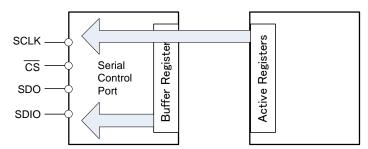

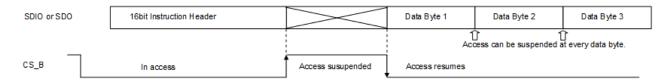

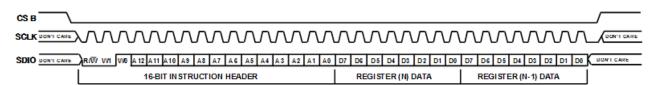

| Clock Rate(SCLK)            | 1/ t <sub>SCLK</sub> |                                      |     |     | 20  | MHz  |