# Apollo S10 SoM Board

USER MANUAL

#### Contents

| Chap                      | ter 1 Overview                                                              | 5                          |

|---------------------------|-----------------------------------------------------------------------------|----------------------------|

| 1.1                       | General Description                                                         | 5                          |

| 1.2                       | Board Layout                                                                | 6                          |

| 1.3                       | Key Features                                                                | 8                          |

| 1.3.                      | Block Diagram                                                               | 9                          |

| 1.4.                      | Mechanical Specifications                                                   | 10                         |

| 1.5.                      | The Purpose of Screw Set                                                    | 12                         |

| 1.6.                      | Power Requirement                                                           | 13                         |

|                           |                                                                             |                            |

| 1.7.                      | Connectivity                                                                | 14                         |

|                           | Connectivityter 2 Board Component                                           |                            |

|                           |                                                                             | 17                         |

| Chap                      | ter 2 Board Component                                                       | <b>17</b><br>17            |

| <b>Chap</b><br>2.1        | ter 2 Board Component  Configuration Interface                              | <b>17</b><br>17<br>21      |

| <b>Chap</b><br>2.1<br>2.2 | ter 2 Board Component  Configuration Interface  Setup and Status Components | <b>17</b><br>17<br>21      |

| <b>Chap</b> 2.1 2.2 2.3   | Configuration Interface  Setup and Status Components  General User I/O      | 17<br>17<br>21<br>25<br>27 |

| 2.7  | Clock    | Circuit                         | 59  |

|------|----------|---------------------------------|-----|

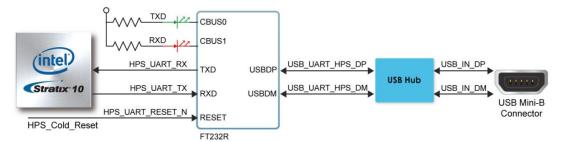

| 2.8  | USB to   | o UART for HPS                  | 61  |

| 2.9  | DDR4     | SDRAM                           | 61  |

| 2.10 | USB 2    | 2.0 OTG PHY                     | 73  |

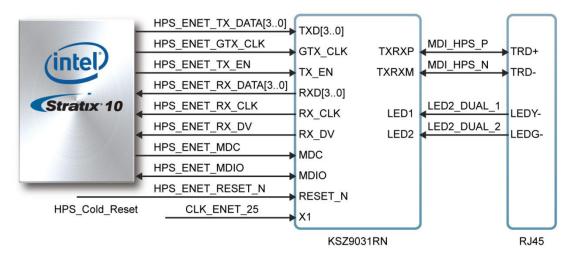

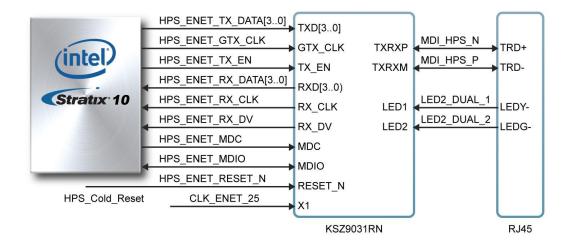

| 2.11 | Gigabi   | it Ethernet                     | 74  |

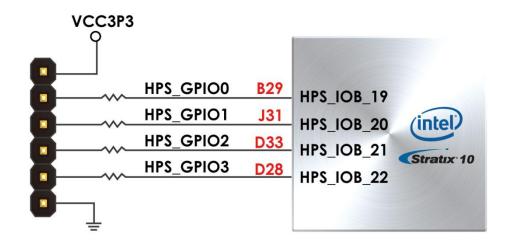

| 2.12 | 1x6 GI   | PIO Header                      | 76  |

| 2.13 | Systen   | m Status Interface              | 76  |

| Chap | ter 3    | System Builder                  | 78  |

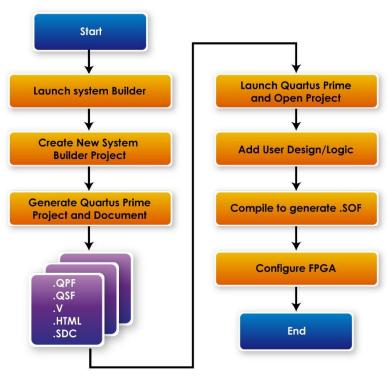

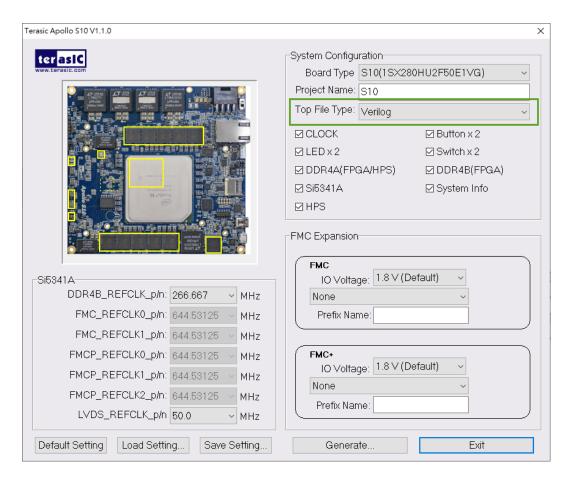

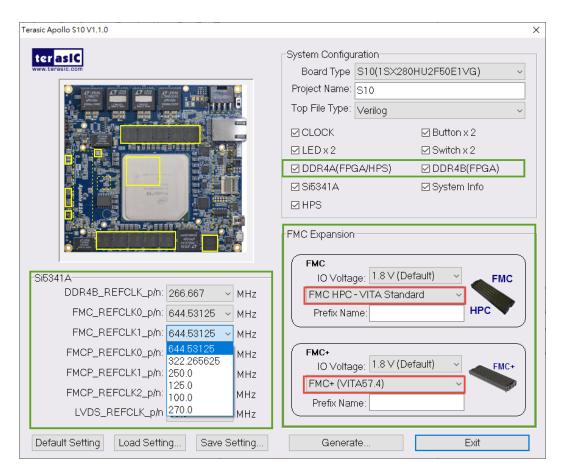

| 3.1  | Introdu  | uction                          | 78  |

| 3.2  | Gener    | al Design Flow                  | 79  |

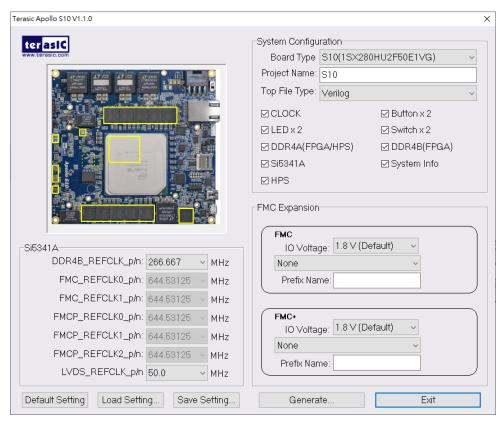

| 3.3  | Using    | System Builder                  | 80  |

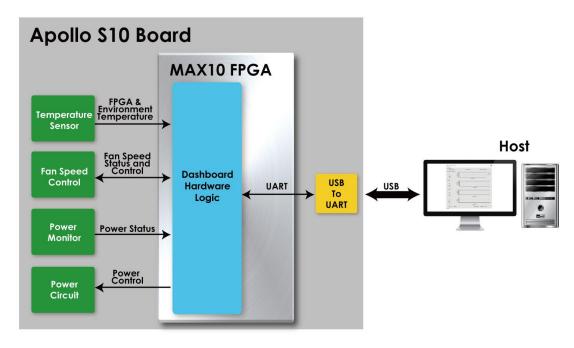

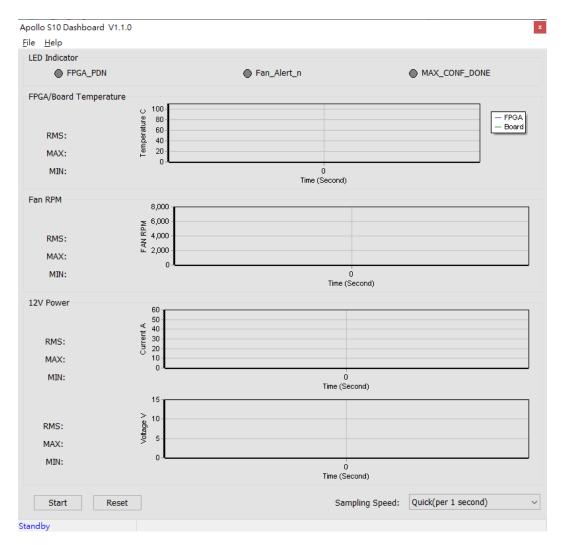

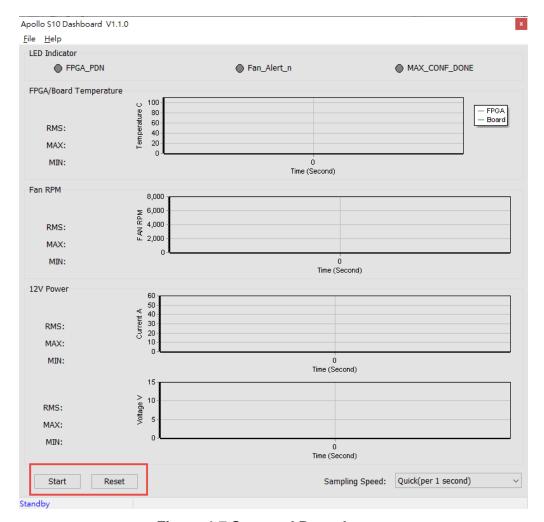

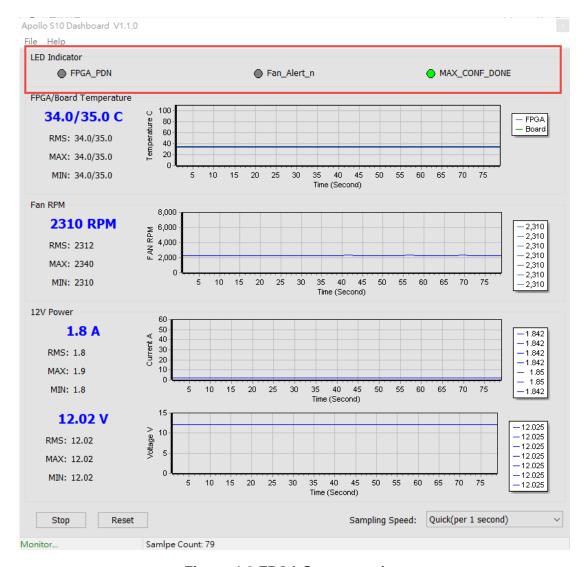

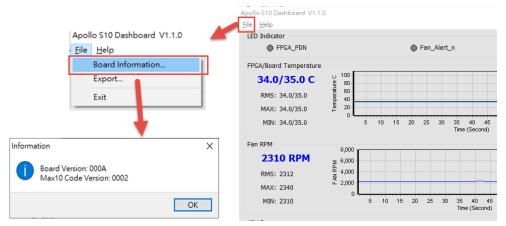

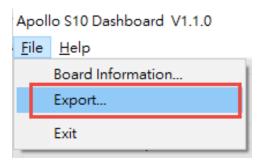

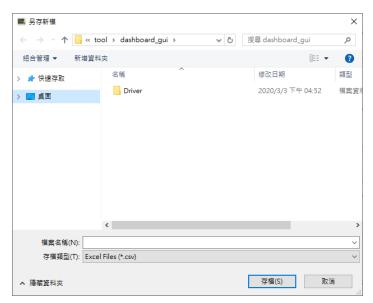

| Chap | ter 4    | Dashboard GUI                   | 88  |

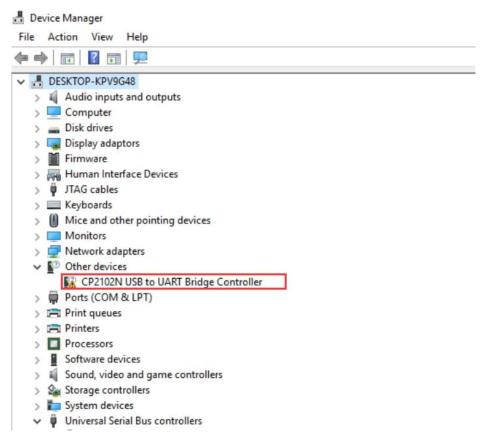

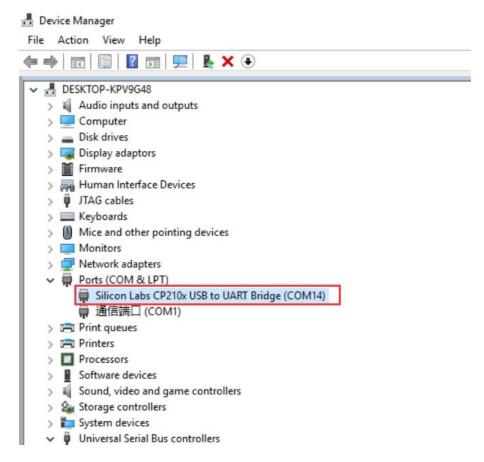

| 4.1  | Driver   | Installed on Host               | 88  |

| 4.2  | Run D    | ashboard GUI                    | 91  |

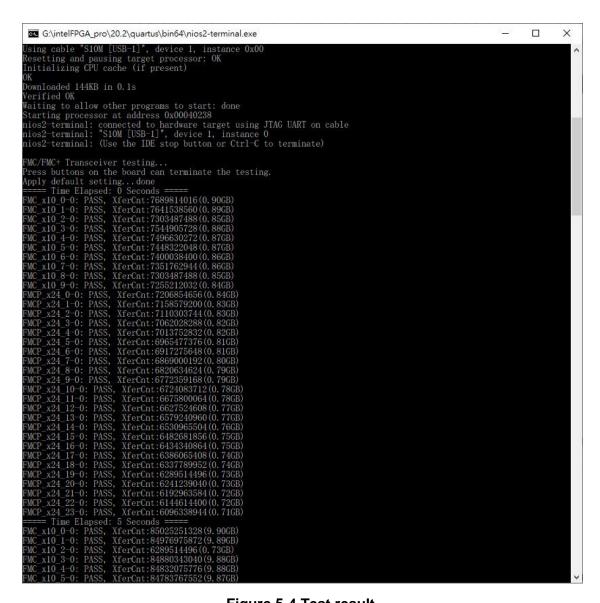

| Chap | ter 5    | Transceiver Verification        | 100 |

| 5.1  | Function | on of the Transceiver Test Code | 100 |

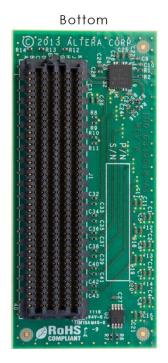

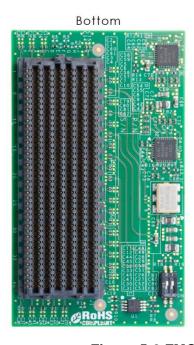

| 5.2  | Hardw    | /are Required                   | 100 |

| 5.3  | Execu    | te the Test Code                | 102 |

| Chapt | er 6 Additional Information10 | 04 |

|-------|-------------------------------|----|

| 6.1   | Getting Help10                | 04 |

# **Chapter 1**

# **Overview**

his chapter provides an overview of the Apollo S10 SoM Board and installation guide.

## 1.1 General Description

Designed for modular and scalable high-performance FPGA Prototyping and HPC solutions, Apollo S10 SoM packs unbeatable performance and energy efficiency in a tiny form factor and provides up to 90X performance increase over CPUs for critical workloads such as simulation acceleration, molecular dynamics, machine learning.

Apollo S10 SoM takes advantage of the latest Intel® Stratix® 10 SoC with 2800K logic elements to obtain speed and power breakthrough (with up to 70% lower power). Combining a number of high-end hardware interfaces such as high-capacity and high-bandwidth DDR4 SDRAM (up to 64GB), on-board USB Blaster II, and FMC/FMC+ connectors for I/O expansion, the board delivers more than 2X the performance of previous generation development kits.

Apollo S10 SoM is also extensible. Apollo Carrier board is designed to assist our clients' development of Apollo S10 SoM. The carrier board features two ultra low-latency, straight connections 40Gbps QSFP+ module and Thunderbolt™ 3 for our clients' to evaluate the I/O planned for their systems, and build their custom systems around it.

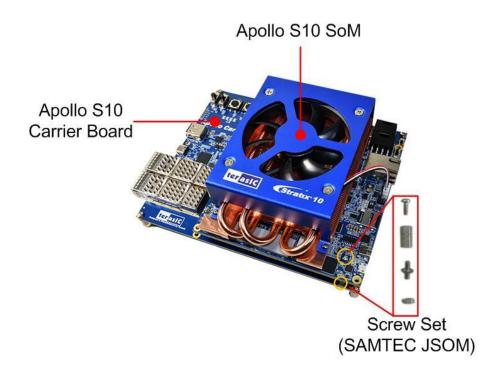

Apollo S10 SoM

**User Manual**

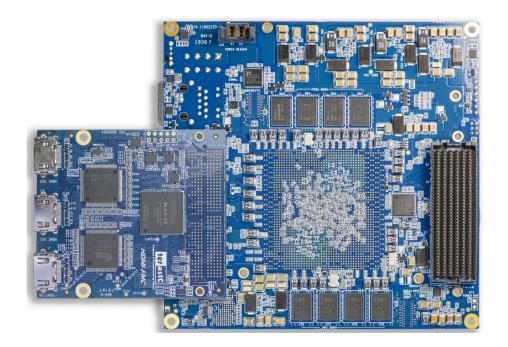

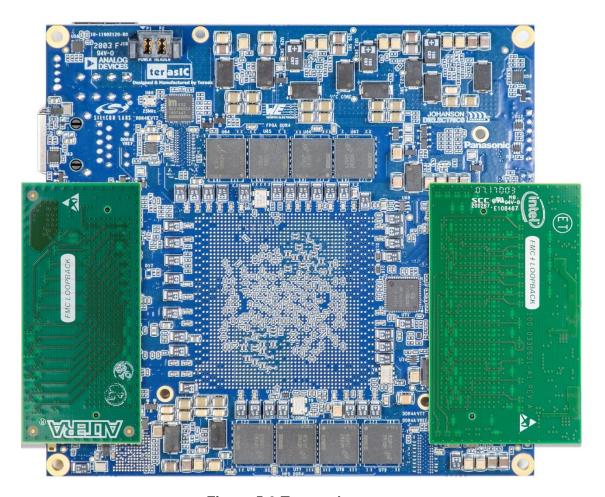

Figure 1-1 Apollo S10 board with heat sink and fan

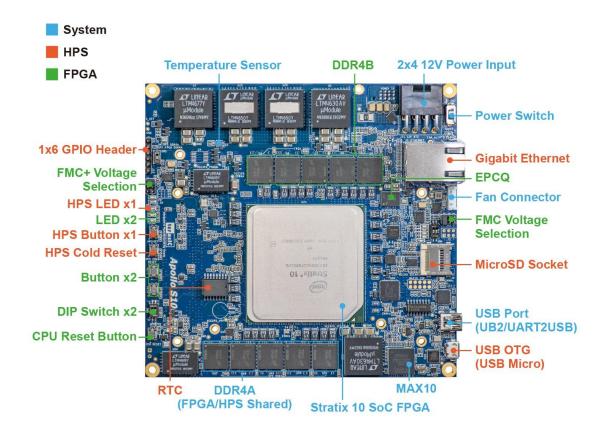

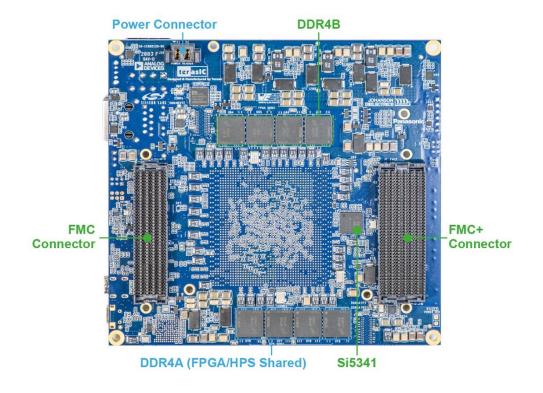

## 1.2 Board Layout

The figures below depict the layout of the board and indicate the location of the connectors and key components.

December 21,

Figure 1-2 Apollo S10 board top

## 1.3 Key Features

The following hardware is implemented on the Apollo S10 board:

#### **■** FPGA Device

- Intel Stratix ® 10 SoC FPGA: 1SX280HU2F50E1VG

- 2,800K logic elements (LEs)

- 229 Mbits embedded memory(M20K)

- 96 transceivers (up to 28.3Gbps)

- 11,520 18-bit x 19-bit multipliers

- 5,760 Variable-precision DSP blocks

#### **■** FPGA Configuration

- On-Board USB Blaster II (UB2) for FPGA programming and Debug

- AS Mode configuration from QSPI Flash

#### ■ FPGA Fabric

- 1024Mbit QSPI Flash (EPCQL1024 Compliant)

- 2 on-board independent DDR4 banks

- Each 32GB x72bit DDR4-2133MT/s

- One bank is shared with FPGA and HPS

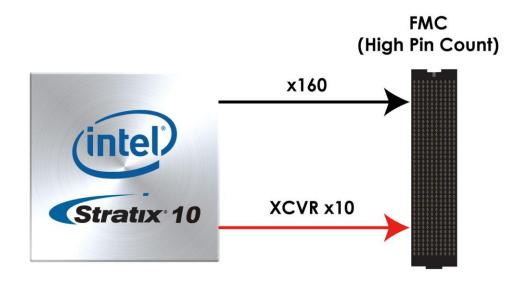

- FMC (Vita57.1) connector with 10 transceivers

- FMC 1.8V/1.5V/1.2V Voltage Selection

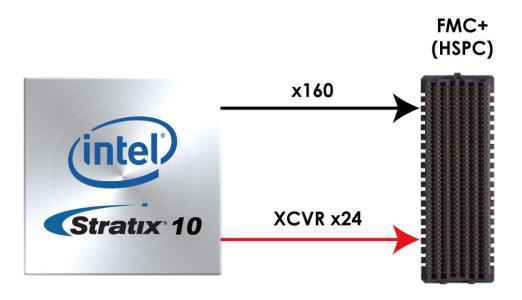

- FMC+(Vita57.4) connector with 24 transceivers

- FMC+ 1.8V/1.5V/1.2V Voltage Selection

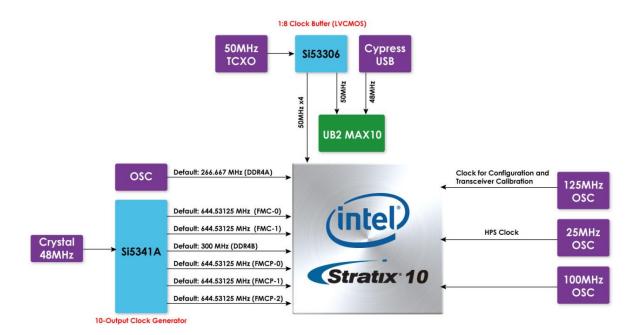

- Two 50Mhz Single-ended Clock Source

- Clock Generator Si5341

**User Manual**

LED x2, Button x2, DIP Switch x2, CPU Reset

## ■ HPS(Hard Processor System) Fabric

December 21,

- Quad-core 64 bit ARM Cortex-A53 MPCore\* processor

- MicroSD Socket

- Gigabit Ethernet with RJ45

- USB OTG with Micro USB Connector

- UART to USB with Mini USB Connector

- LED x1, Button x1, Cold Reset Button

- 1x6 GPIO Header

- RTC

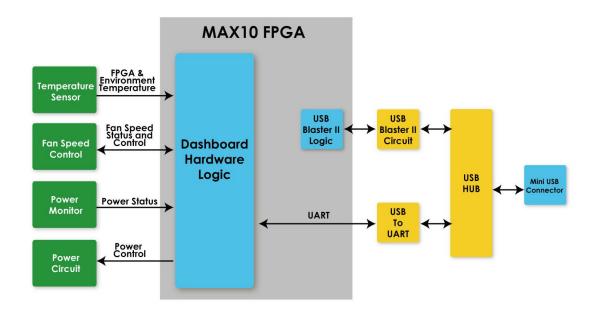

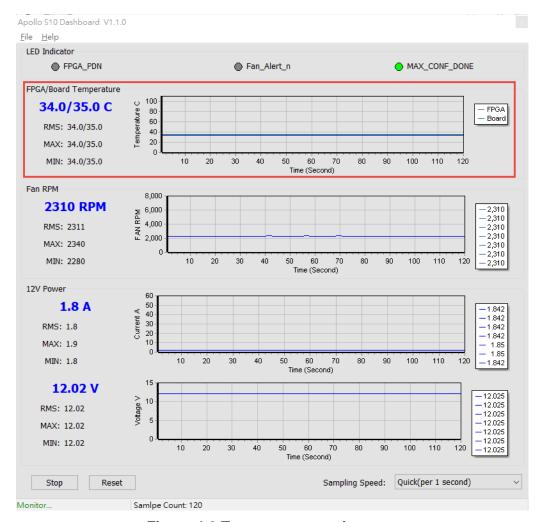

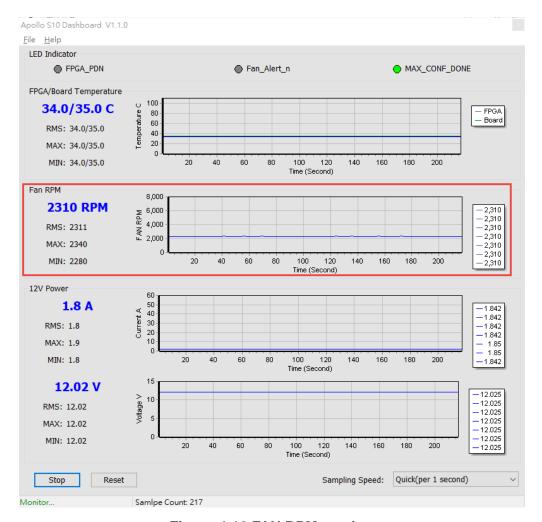

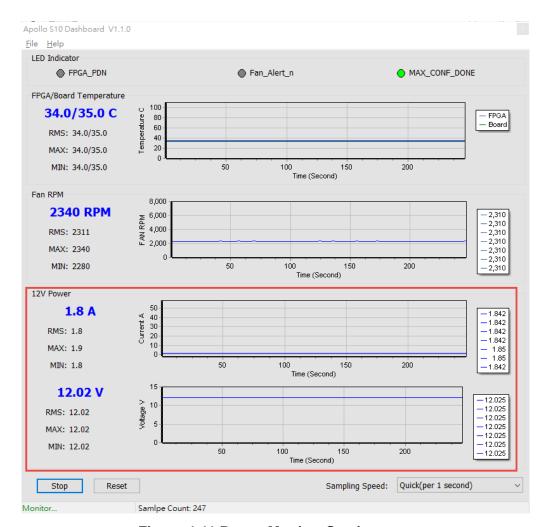

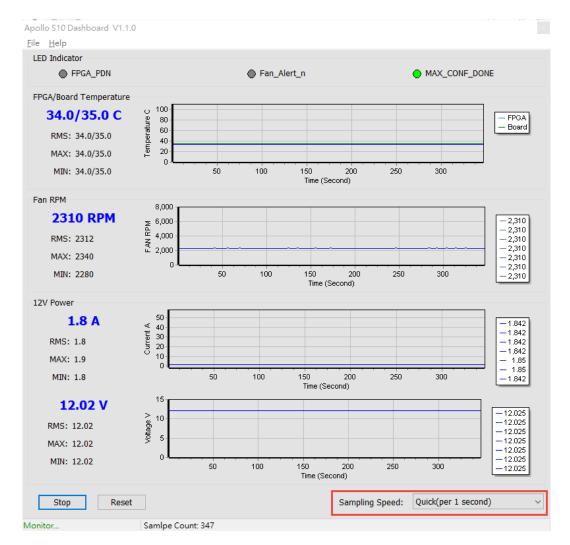

#### Dashboard System

- Input Power Monitor

- FPGA and Board Temperature Monitor

- Fan Control and Monitor

- Auto Fan Speed

- Auto Shutdown

#### **■** Power Source

- 12V from 2x4 PCle connector

- 12V from Samtec connector (reserved for carrier board)

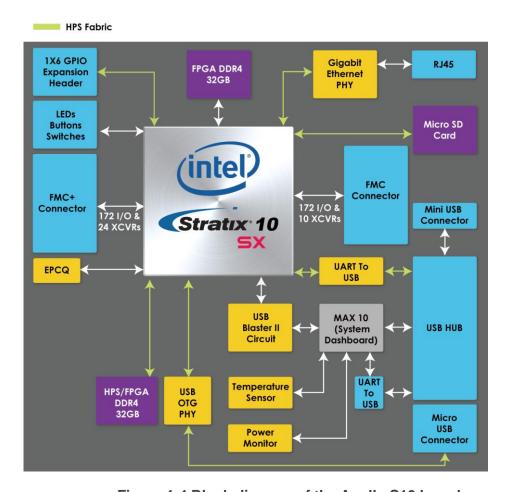

## 1.3. Block Diagram

**Figure 1-4** shows the block diagram of the Apollo S10 board. To provide maximum flexibility for the users, all key components are connected to the Stratix ®10 SX FPGA device. Thus, users can configure the FPGA to implement any system design.

December 21,

Figure 1-4 Block diagram of the Apollo S10 board

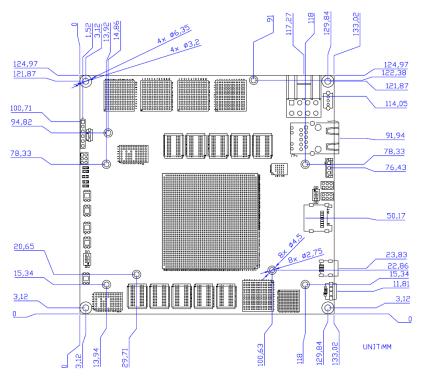

## 1.4. Mechanical Specifications

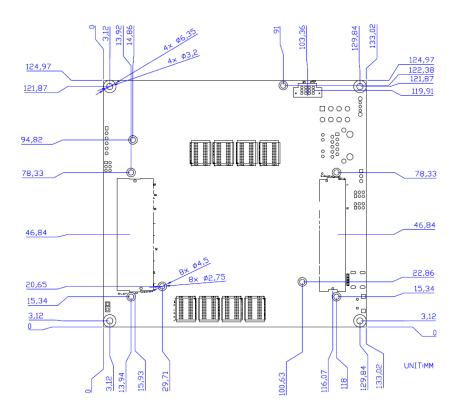

**Figure 1-5** and **Figure 1-6** are the top and bottom Mechanical Layout of Apollo S10 board. The unit of the Mechanical Layout is millimeter (mm).

Figure 1-5 Top side mechanical layout

Figure 1-6 Bottom side mechanical layout

December 21,

## 1.5. The Purpose of Screw Set

The screw set (See **Figure 1-7**) in the Apollo s10 SoM kit content is mainly provided for connecting to Terasic or user owned **carrier board** (See **Figure 1-8**). If the user wants to use screw set to the connection between Apollo S10 SoM and FMC / FMC + daughter card is not 100% applicable. We still recommend users to use the screw set provided by the daughter card to connect the Apollo S10 SoM.

For how to use screw set to connect module to carrier board, please refer to User manual of the Apollo Carrier board (*Apollo\_Carrier\_Board\_User\_Manual\_revB.pdf*) in chapter 3 : Board Assembly.

Figure 1-7 Screw set provided in the kit content

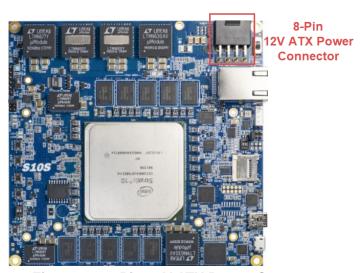

## 1.6. Power Requirement

#### ■ Stand-alone mode

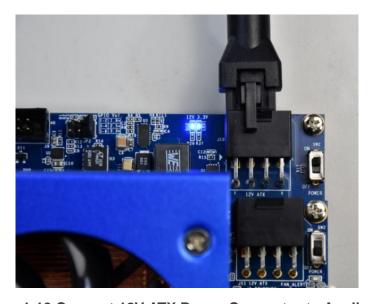

When the Apollo S10 board is used in stand-alone mode, users can use the 12V ATX power provided in the kit to connect to the 8-pin 12V ATX power connector (See **Figure 1-9** and **Figure 1-10**) of the Apollo S10.

Figure 1-9 8-Pin 12V ATX Power Connector

Figure 1-10 Connect 12V ATX Power Connector to Apollo S10

#### Connect to the based board

If user wants use the Apollo S10 board as the module board and connect it to the carrier board. The carrier board needs to provide at least **12V 15A** power to the J10 power connector (See **Figure 1-11**) of the Apollo S10 board. Please note that the 12V and 3.3V of the FMC and FMC + connector are provided by the Apollo S10 board, the carrier board does not need to provide these powers. For part number of the connector connected to J10, please refer to **Table 1-1** in the section 1.7.

Figure 1-11 Power connector for connecting based board

## 1.7. Connectivity

The Apollo S10 board provides FMC and FMC + connector as expansion interface. Users can use Apollo S10 as stand alone, connect FMC daughter card (See **Figure 1-12**).

Figure 1-12 Apollo S10 board connects to the FMC daughter card

Users can also use Apollo S10 as an FPGA module board and connect to other carrier boards to form a system (See **Figure 1-13**).

#### Figure 1-13 Apollo S10 board connects to the based board

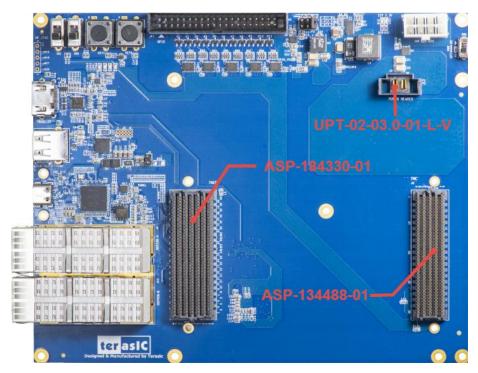

If user wants to make their owned carrier board to connect with the Apollo S10 board, there are three connectors are needed to be used, they are FMC +, FMC and Power connector (See **Figure 1-14**). The following table lists the manufacturer and manufacturer part numbers of the three connectors that can match with the connectors of the Apollo S10 board.

Table 1-1 Part Number of the connector on the Apollo S10 board

| Connector       | Apollo S10 Board's Part     | Carrier Board's              |  |

|-----------------|-----------------------------|------------------------------|--|

| Connector       | Number                      | Part Number                  |  |

| FMC             | J2                          | Samtec : ASP-134488-01       |  |

| FIVIC           | Samtec : ASP-134486-01      | Samec . ASP-134400-01        |  |

| EMO.            | J1                          | Comton: ACD 404220 04        |  |

| FMC+            | Samtec : ASP-184329-01      | Samtec : ASP-184330-01       |  |

| Dower Connector | J10                         | Samtoo : LIDT 02 02 0 04 L V |  |

| Power Connector | Samtec : UPS-02-07.0-02-L-V | Samtec : UPT-02-03.0-01-L-V  |  |

Figure 1-14 Part Number of the connector for based board

# **Chapter 2**

# **Board Component**

his chapter introduces all the important components on the Apollo S10.

## 2.1 Configuration Interface

This section describes the configuration mode for Stratix 10 SX FPGAs available on the Apollo S10. The peripheral circuits and usage scenarios for each mode will be listed.

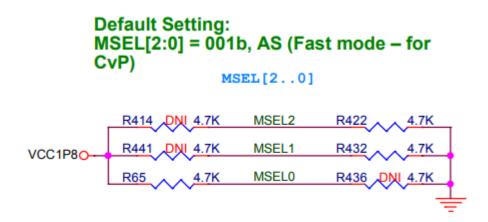

As shown in **Figure 2-1**, the mode select pin of the FPGA on the Apollo S10 board has been set to **Active Serial (AS) mode** using resistors. Thus, the Apollo S10 board supports the following configuration modes:

- JTAG Mode (Configure the FPGA using the on-board USB Blaster II).

- Active Serial (AS) mode

Users can use these modes to configure the FPGA or HPS (Hardware Process System) fabric in the Stratix 10 SX FPGA and make the FPGA to run the user's logic or boot the HPS to run the OS.

Below we will introduce more detailed information of AS mode, as well as other configuration information.

December 21,

Figure 2-1 The MSEL pin setting

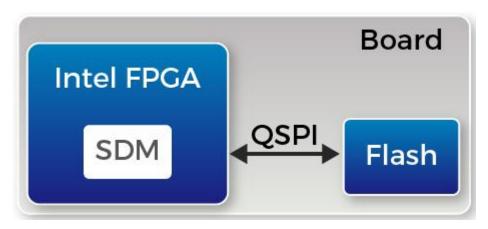

#### Active Serial (Fast) mode

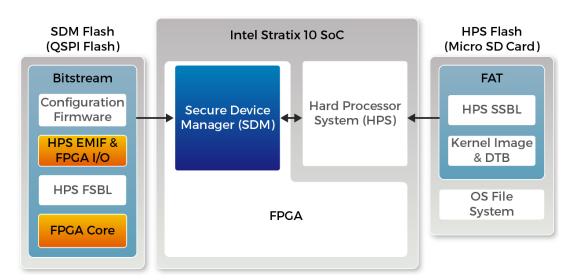

In AS mode, the FPGA's configuration file is stored in the QSPI flash. The Secure Device Manager (SDM) in Stratix 10 FPGA is responsible for the entire AS mode process and interface. The SDM will load the initial configuration firmware from the QSPI flash to configure the FPGA including FPGA I / O and core configuration. HPS part of the boot can also be completed in this mode. **Figure 2-2** shows the architecture of the AS mode of the Apollo S10 board.

Figure 2-2 AS mode for the Apollo S10 board

For more information on the configuration of Stratix 10 FPGAs, please refer to the file: <a href="Intel Stratix 10 Configuration User Guide">Intel Stratix 10 Configuration User Guide</a>

**User Manual**

#### ■ SoC FPGA boot

The boot process for Stratix 10 SoC FPGAs can be divided into two different methods:

- FPGA Configuration First Mode

- HPS Boot First Mode

The difference between the two methods is the initial difference between HPS and FPGA fabric after powering on. More details can be found in the user documentation: Intel Stratix 10 SoC FPGA Boot User Guide.

The factory setting of the SoC boot of the Apollo S10 board is the **FPGA Configuration First Mode**. The architecture is shown in the **Figure 2-3**. Two storage mediums are used. The system needs QSPI flash on Apollo S10 as SDM flash for booting.

Figure 2-3 FPGA Configuration First Dual SDM and HPS Flash

The QSPI flash memory has the following boot data for the first part of the SoC FPGA configuration:

- Configuration firmware for the SDM

- FPGA I/O and HPS external memory interface (EMIF) I/O configuration data

- FPGA core configuration data

- HPS First-Stage Boot Loader(FSBL) code and FSBL hardware handoff binary data

December 21,

Meanwhile, Terasic provides the micro SD card with built-in image data as HPS flash, which is used for HPS boot in the later part. The micro SD card stores the following data:

- Second-Stage Boot Loader(SSBL)

- Kernel Image and Device Tree Blob(DTB)

- Operating System

The factory SoC boot process of Apollo S10 is summarized as follows:

When the Apollo S10 board is powered on, the SDM will read the configuration firmware and complete SDM initial form the QSPI flash according to the MSEL pin setting. Then, the SDM will configure the FPGA I/O and core (full configuration).

After the FPGA is first configured, SDM continues to load the FSBL(First-Stage Boot Loader) from the QSPI flash and transfer it to the HPS on-chip RAM, and releases the HPS reset to let the HPS start using the FSBL hardware handoff file to setup the clocks, HPS dedicated I/Os, and peripherals.

The FSBL then loads the SSBL(Second-Stage Boot Loader) from the Micro SD Card into HPS SDRAM and passes the control to the SSBL. The SSBL enables more advanced peripherals and loads OS into SDRAM.

Finally, the OS boots and applications are scheduled for runtime launch.

### **■ JTAG Programming**

The JTAG interface of the Apollo S10 is mainly implemented by the USB Blaster II circuit on the board. For programming by on-board USB Blaster II, the following procedures show how to download a configuration bit stream into the Stratix 10 SX FPGA:

- Make sure that power is provided to the FPGA board

- Connect your PC to the FPGA board using a micro-USB cable and make sure the USB Blaster II driver is installed on the PC.

- Launch Quartus Prime programmer and make sure the USB Blaster II is

December 21,

detected.

In Quartus Prime Programmer, add the configuration bit stream file (.sof), check the associated "Program/Configure" item, and click "Start" to start FPGA programming.

#### ■ Quartus Prime 19.1 Patch

If user using the Intel® Quartus® Prime Pro Edition software version 19.1 with on-board USB Blaster II circuit on the Apollo S10 board, a USB device enumeration error may occur when using the USB Blaster II circuit to the computer hosting the Intel® Quartus® Prime Pro Edition software. To workaround this problem, please download and install patch 0.03 from the links below.

You must install the Intel® Quartus® Prime Pro Edition software version 19.1 software before installing this patch:

- Download the version 19.1 patch 0.03 for Linux (.run)

- Download the version 19.1 patch 0.03 for Window (.run)

- Download the Readme for the version 19.1 patch 0.03 (.txt)

## 2.2 Setup and Status Components

This section will introduce the use of the switch for setup on the Apollo S10 board, as well as a description of the various status LEDs.

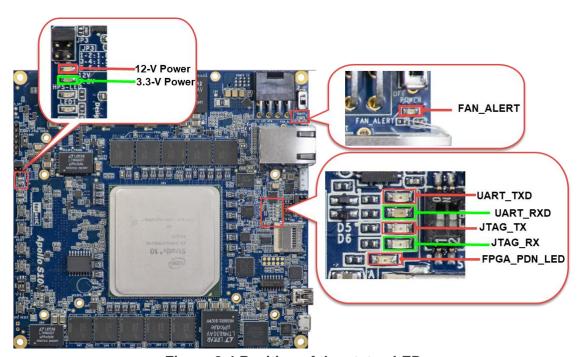

#### ■ Status LED

The FPGA development board includes board-specific status LEDs to indicate board status. Please refer to **Table 2-1** for the description of the LED indicators. **Figure 2-4** shows the location of all these status LED.

Table 2-1 Status LED

| Board<br>Reference | LED Name    | Description                                                                                 |

|--------------------|-------------|---------------------------------------------------------------------------------------------|

| D1                 | FAN ALERT   | Illuminates when the fan is abnormal, such as when the fan speed is different from expected |

| D2                 | 12-V Power  | Illuminates when 12-V power is active.                                                      |

| D3                 | 3.3-V Power | Illuminates when 3.3-V power is active.                                                     |

| TXD                | UART_TXLED  | Illuminates when the UART interface is transmitting                                         |

|           |              | data                                               |  |  |

|-----------|--------------|----------------------------------------------------|--|--|

| RXD       | UART_RXLED   | Illuminates when the UART interface is receiving   |  |  |

|           |              | data                                               |  |  |

| D7        | JTAG TX      | Illuminates when the USB Blaster II circuit is     |  |  |

| <i>D1</i> | JIAG_IX      | transmitting data                                  |  |  |

| D8        | JTAG RX      | Illuminates when the USB Blaster II circuit is     |  |  |

| D6        |              | receiving data                                     |  |  |

|           | FPGA_PDN_LED | When the FPGA temperature or the board             |  |  |

| D9        |              | temperature exceeds 95 degrees or the power        |  |  |

| Da        |              | consumption exceeds 180W, all the power of the     |  |  |

|           |              | FPGA will be cut off, and the D9 will be flashing. |  |  |

Figure 2-4 Position of the status LED

#### ■ JTAG Interface Switch

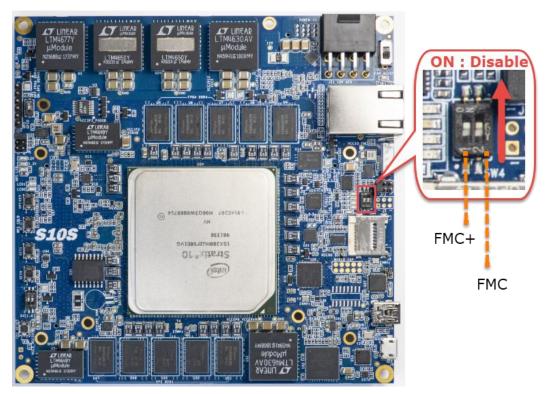

The JTAG interface switch **SW4** is to set whether the JTAG interface of the FMC and FMC + connector is connected to the JTAG chain in the Apollo S10 board. Both the FMC+ and FMC connectors will not be included in the JTAG chain if the switches are set to ON position (See **Figure 2-5**).**Table 2-2** lists the setting of the SW4.

Figure 2-5 Position of slide switches SW4

Table 2-2 SW4 setting

| Board     | Signal Name        | Description                                                                                                                                        | Default |

|-----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Reference | Oignai Name        | Description                                                                                                                                        | Delault |

| SW4.1     | FMCP_JTAG_BYPASS_n | ON: Disable the JTAG interface of the FMC+ connector into the JTAG chain  OFF: Enable the JTAG interface of the FMC+ connector into the JTAG chain | ON      |

| SW4.2     | FMC_JTAG_BYPASS_n  | ON: Disable the JTAG interface of the FMC connector into the JTAG chain  OFF: Enable the JTAG interface of the FMC connector into the JTAG chain   | ON      |

## ■ FMC\_VCCIO and FMCP\_VCCIO Select Header

The FMC and FMC + connector I / O standard on the Apollo S10 can be set to three voltages: 1.8V, 1.5V and 1.2V. Users can set the desired voltage of FMC and FMC + by setting JP2 and JP3 respectively. The JP2 and JP3 can change the VCCIO voltage of FPGA I/O on FMC and FMC+ connector. **Figure 2-6** shows the position of the JP2 and JP3. **Table 2-3** list the FMC\_VCCIO Headers (JP2) setting for FMC connector. **Table 2-4** shows the setting of the JP3 for FMC+ connector.

Figure 2-6 FMC and FMC+ I/O standard setting headers

Table 2-3 JP2 Setting for FMC I/O standard

| JP2 Setting                    | FMC I/O Standard       |

|--------------------------------|------------------------|

| FMC_VCCIO                      | 1.2V                   |

| FMC_VCCIO                      | 1.5V                   |

| FMC_VCCIO<br>1.8<br>1.5<br>JP2 | 1.8V (Default Setting) |

Table 2-4 JP3 Setting for FMC+ I/O standard

| JP3 Setting FMC I/O Standard    |                        |  |  |

|---------------------------------|------------------------|--|--|

| FMC+ VCCIO<br>1.8<br>1.5<br>1.2 | 1.2V                   |  |  |

| FMC+ VCCIO 1.8 1.8 1.2 1.2      | 1.5V                   |  |  |

| FMC+ VCCIO<br>1.8<br>1.5<br>1.2 | 1.8V (Default Setting) |  |  |

## 2.3 General User I/O

This section describes the user I/O interface of the FPGA and HPS fabric. Please note that the HPS and FPGA portions of the device each have their own pins. Pins are not freely shared between the HPS and the FPGA fabric.

#### User Defined Push-buttons

User Manual

The FPGA board includes two FPGA fabric and one HPS fabric user defined push-buttons that allow users to interact with the Stratix 10 SX device. Each push-button provides a high logic level or a low logic level when it is not pressed or pressed, respectively. **Table 2-5** lists the board references, signal names and their corresponding Stratix 10 SX device pin numbers for the push-buttons of the FPGA fabric. **Table 2-6** list the information of the push-button for the HPS fabric.

December 21,

Table 2-5 Push-button (FPGA fabric) Pin Assignments, Schematic Signal Names

| Board<br>Reference | Schematic<br>Signal Name | Description               | IVO Standard | Stratix 10 SX<br>Pin Number |

|--------------------|--------------------------|---------------------------|--------------|-----------------------------|

| PB0                | BUTTON0                  | High Logic Level when the | 3.0-V LVTTL  | PIN_AE36                    |

| PB1                | BUTTON1                  |                           | 3.0-V LVTTL  | PIN_AG34                    |

| PB3                | CPU_RESET_n              |                           | 3.0-V LVTTL  | PIN_AC35                    |

Table 2-6 Push-button (HPS fabric) Pin Assignments, Schematic Signal Names

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                                     |       | Stratix 10 SX<br>Pin Number |

|--------------------|-----------------------------|-------------------------------------------------|-------|-----------------------------|

| PB6                | HPS KEY                     | High Logic Level when the button is not pressed | 1.8-V | PIN_C28                     |

#### ■ User-Defined Dip Switch

There are two positions dip switch (SW0) on the FPGA fabric to provide additional FPGA input control. When a position of dip switch is in the DOWN position or the UPPER position, it provides a low logic level or a high logic level to the Stratix 10 SX FPGA, respectively.

**Table 2-7** lists the signal names and their corresponding Stratix 10 SX device pin numbers.

Table 2-7 Dip Switch Pin Assignments, Schematic Signal Names, and Functions

| Board<br>Reference | Schematic<br>Signal Name | Description                 |             | Stratix 10 SX<br>Pin Number |

|--------------------|--------------------------|-----------------------------|-------------|-----------------------------|

| SW0                | SW0                      | High logic level when SW in | 3.0-V LVTTL | PIN_AG35                    |

| SW1                | SW1                      | the UPPER position.         | 3.0-V LVTTL | PIN_AH33                    |

#### ■ User-Defined LEDs

The FPGA board consists of 2 FPGA fabric and 1 HPS fabric user-controllable LEDs to

allow status and debugging signals to be driven to the LEDs from the designs loaded into the Stratix 10 SX device. Each LED is driven directly by the Stratix 10 SX FPGA. The LED is turned on or off when the associated pins are driven to a low or high logic level, respectively. A list of the pin names on the FPGA that are connected to the LEDs is given in **Table 2-8**. **Table 2-9** list the information of the LED for the HPS fabric.

Table 2-8 User LEDs (FPGA fabric) Pin Assignments, Schematic Signal Names

| Board<br>Reference | Schematic<br>Signal Name | Description                                          | I/O Standard | Stratix 10 SX<br>Pin Number |

|--------------------|--------------------------|------------------------------------------------------|--------------|-----------------------------|

| LED0               | LED0                     | Driving a logic 0 on the I/O port turns the LED ON.  |              | PIN_AH32                    |

| LED1               | LED1                     | Driving a logic 1 on the I/O port turns the LED OFF. |              | PIN_AC33                    |

Table 2-9 User LEDs (HPS fabric) Pin Assignments, Schematic Signal Names

| Board     | Schematic   | Description                  | I/O      | Stratix 10 SX |

|-----------|-------------|------------------------------|----------|---------------|

| Reference | Signal Name | Description                  | Standard | Pin Number    |

| HPS_LED   | HPS_LED     | Driving a logic 0 on the I/O | 1.8-V    | PIN_G30       |

|           |             | port turns the LED ON.       |          |               |

|           |             | Driving a logic 1 on the I/O |          |               |

|           |             | port turns the LED OFF.      |          |               |

## 2.4 Micro SD Card Socket

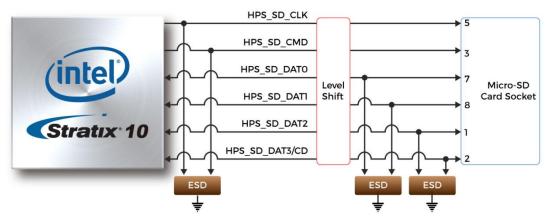

The board supports Micro SD card interface with x4 data lines. It serves for an external storage for the HPS fabric. Figure 2-7 shows signals connected between the HPS and Micro SD card socket. **Table 2-10** lists the pin assignment of Micro SD card socket to the HPS.

December 21,

Figure 2-7 Pin-out of Micro SD Card socket

Table 2-10 Micro SD Card Socket Header Pin Assignments, Schematic Signal Names, and Functions

| Schematic<br>Signal Name | Description         | I/O Standard | Stratix 10 SX<br>Pin Number |

|--------------------------|---------------------|--------------|-----------------------------|

| HPS_SD_CLK               | HPS SD Clock        | 1.8-V        | PIN_A31                     |

| HPS_SD_CMD               | HPS SD Command Line | 1.8-V        | PIN_J30                     |

| HPS_SD_DATA[0]           | HPS SD Data[0]      | 1.8-V        | PIN_P30                     |

| HPS_SD_DATA[1]           | HPS SD Data[1]      | 1.8-V        | PIN_H30                     |

| HPS_SD_DATA[2]           | HPS SD Data[2]      | 1.8-V        | PIN_D31                     |

| HPS_SD_DATA[3]           | HPS SD Data[3]      | 1.8-V        | PIN_H32                     |

## 2.5 FMC Connector

The FPGA Mezzanine Card (FMC) interface provides a mechanism to extend the peripheral-set of an FPGA host board by means of add-on daughter cards, which can address today's high-speed signaling requirements as well as low-speed device interface support. The FMC interfaces support JTAG, clock outputs and inputs, high-speed serial I/O (transceivers), and single-ended or differential signaling.

There is one FMC connector on the Apollo S10 board, it is a High Pin Count (HPC) size of connector, The HPC connector on Apollo S10 board can provides 160 user-define, single-ended signals (Not include clock, I2C and some control signals) and 10 serial transceiver pairs. **Figure 2-8** is the FPGA I/O connected to the FMC connector on the Apollo S10 board.

December 21,

Below we will introduce according to the individual functions of FMC connector.

Figure 2-8 FMC connector on Apollo S10 board

#### ■ Clock Interface

**Table 2-11** shows the FPGA dedicated clock input pin placement on the FMC connector.

Table 2-11 FMC clock interface distribution

| Signal Name    | FMC Clock in/out pin | FPGA Clock Input Pin | FPGA<br>Pin |

|----------------|----------------------|----------------------|-------------|

| Oignal Name    | name                 | Placement            | Assignment  |

| FMC_CLK_M2C_p0 | CLK0_M2C_P           | CLK_3L_1P            | C22         |

| FMC_CLK_M2C_n0 | CLK0_M2C_N           | CLK_3L_1N            | C21         |

| FMC_CLK_M2C_p1 | CLK1_M2C_P           | CLK_3K_1P            | J16         |

| FMC_CLK_M2C_n1 | CLK1_M2C_N           | CLK_3K_1N            | H16         |

| FMC_HA_p0      | HA00_P_CC            | CLK_3J_0P            | P14         |

| FMC_HA_n0      | HA00_N_CC            | CLK_3J_0N            | N13         |

| FMC_HA_p1      | HA01_P_CC            | CLK_3J_1P            | J13         |

| FMC_HA_n1      | HA01_N_CC            | CLK_3J_1N            | K13         |

| FMC_HB_p0      | HB00_P_CC            | CLK_3K_0P            | E16         |

| FMC_HB_n0      | HB00_N_CC            | CLK_3K_0N            | F16         |

| FMC_LA_p0      | LA00_P_CC            | CLK_3L_0P            | J20         |

FMC\_LA\_n0 LA00\_N\_CC CLK\_3L\_0N J19

#### ■ Power Supply

The Apollo S10 board provides 12V, 3.3V and VCCIO\_FMC power through FMC ports. **Table 2-12** indicates the maximum power consumption for the FMC connector.

CAUTION: Before powering on the Apollo S10 board with a daughter card, please check to see if there is a short circuit between the power pins and FPGA I/O.

Supplied Voltage

Max. Current Limit

12V

1A

3.3V

3A

VCCIO FMC

4A

**Table 2-12 Power Supply of the FMC**

#### Adjustable I/O Standards

The FPGA I/O standards of the FMC ports can be adjusted by configuring the header position. Each port can be individually adjusted to 1.2V, 1.5V or 1.8V via jumper JP2 on the Apollo S10 board. For detailed setting, please refer to Section 2.2: FMC\_VCCIO and FMCP VCCIO Select Header.

#### **■** JTAG Chain on FMC

The JTAG chain on the Apollo S10 board supports JTAG interface extension to the FMC connector so that the JTAG device on the user's FMC daughter card can be joined with JTAG chain on the Apollo S10 board. Users can enable this feature through the switch (**SW4.2**) on the Apollo S10 board. In the board's default setting, the JTAG interface of the FMC connector is bypassed to keep the Apollo S10 board JTAG chain to maintain close loop. For detailed setting, please refer to Section 2.2: **JTAG Interface Switch.**

#### ■ Transceiver Channels Speed

Apollo-S10 SoM

User Manual

December 21,

There are 10 transceivers connected to the Stratix 10 FPGA on the FMC connector, two of which belong to the GX channels, and the maximum transmission speed is 17.4 Gbps. The other 8 belong to GXT channels, and the maximum transmission speed can reach 25Gbps. For details, please to see "Intel ® Stratix® 10 L- and H-Tile Transceiver PHY User Guide" for section "1.3. L-Tile / H-Tile Building Blocks". Table 2-13 lists the distribution and speed of the two channels of the FMC connector.

Table 2-13 GX and GXT channels on the FMC connector

| Transceiver channel<br>Type | Net Name                       | Speed     |

|-----------------------------|--------------------------------|-----------|

| GX Channels                 | FMC_DP_M2C_p2/ FMC_DP_C2M_p2 , | 17.4 Gbps |

| OA CHAIIIIEIS               | FMC_DP_M2C_p5/ FMC_DP_C2M_p5 , | 17.4 Obps |

|                             | FMC_DP_M2C_p0/ FMC_DP_C2M_p0 , |           |

|                             | FMC_DP_M2C_p1/ FMC_DP_C2M_p1,  |           |

|                             | FMC_DP_M2C_p3/ FMC_DP_C2M_p3,  |           |

| GXT Channels                | FMC_DP_M2C_p4/ FMC_DP_C2M_p4   | 25 Chma   |

| GAT Channels                | FMC_DP_M2C_p6/ FMC_DP_C2M_p6   | 25 Gbps   |

|                             | FMC_DP_M2C_p7/ FMC_DP_C2M_p7   |           |

|                             | FMC_DP_M2C_p8/ FMC_DP_C2M_p8   |           |

|                             | FMC_DP_M2C_p9/ FMC_DP_C2M_p9   |           |

#### ■ Component Information of the FMC Connector

For information on the FMC part number used on the Apollo S10 board and the male connector connected to it, refer to **Table 1-1** in the section 1.6.

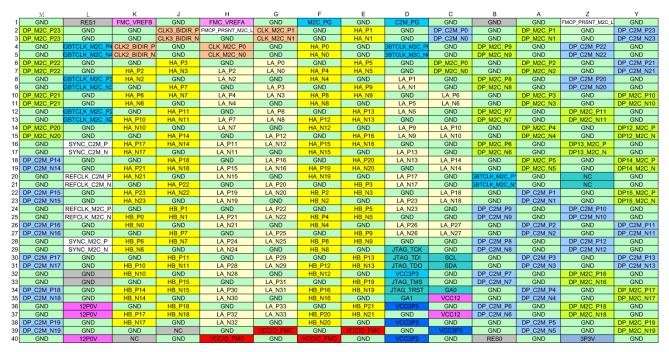

#### ■ FPGA Pin Assignments for FMC Connector

**Figure 2-9** shows the pin out table of the FMC connector on the Apollo S10 and **Table 2-14** lists the FMC connector pin assignments, signal names and functions.

December 21,

|    | K            | J            | Н          | G          | F         | E         | D             | С         | В             | Α         |

|----|--------------|--------------|------------|------------|-----------|-----------|---------------|-----------|---------------|-----------|

| 1  | FMC_VREFB    | GND          | FMC_VREFA  | GND        | M2C_PG    | GND       | C2M_PG        | GND       | NC            | GND       |

| 2  | GND          | CLK3_BIDIR_P | NC         | CLK_M2C_P1 | GND       | HA_P1     | GND           | DP_C2M_P0 | GND           | DP_M2C_P1 |

| 3  | GND          | CLK3_BIDIR_N | GND        | CLK_M2C_N1 | GND       | HA_N1     | GND           | DP_C2M_N0 | GND           | DP_M2C_N1 |

| 4  | CLK2_BIDIR_P | GND          | CLK_M2C_P0 | GND        | HA_P0     | GND       | GBTCLK_M2C_P0 | GND       | DP_M2C_P9     | GND       |

| 5  | CLK2_BIDIR_N | GND          | CLK_M2C_N0 | GND        | HA_N0     | GND       | GBTCLK_M2C_N0 | GND       | DP_M2C_N9     | GND       |

| 6  | GND          | HA_P3        | GND        | LA_P0      | GND       | HA_P5     | GND           | DP_M2C_P0 | GND           | DP_M2C_P2 |

| 7  | HA_P2        | HA_N3        | LA_P2      | LA_N0      | HA_P4     | HA_N5     | GND           | DP_M2C_N0 | GND           | DP_M2C_N2 |

| 8  | HA_N2        | GND          | LA_N2      | GND        | HA_N4     | GND       | LA_P1         | GND       | DP_M2C_P8     | GND       |

| 9  | GND          | HA_P7        | GND        | LA_P3      | GND       | HA_P9     | LA_N1         | GND       | DP_M2C_N8     | GND       |

| 10 | HA_P6        | HA_N7        | LA_P4      | LA_N3      | HA_P8     | HA_N9     | GND           | LA_P6     | GND           | DP_M2C_P3 |

| 11 | HA_N6        | GND          | LA_N4      | GND        | HA_N8     | GND       | LA_P5         | LA_N6     | GND           | DP_M2C_N3 |

| 12 | GND          | HA_P11       | GND        | LA_P8      | GND       | HA_P13    | LA_N5         | GND       | DP_M2C_P7     | GND       |

| 13 | HA_P10       | HA_N11       | LA_P7      | LA_N8      | HA_P12    | HA_N13    | GND           | GND       | DP_M2C_N7     | GND       |

| 14 | HA_N10       | GND          | LA_N7      | GND        | HA_N12    | GND       | LA_P9         | LA_P10    | GND           | DP_M2C_P4 |

| 15 | GND          | HA_P14       | GND        | LA_P12     | GND       | HA_P16    | LA_N9         | LA_N10    | GND           | DP_M2C_N4 |

| 16 | HA_P17       | HA_N14       | LA_P11     | LA_N12     | HA_P15    | HA_N16    | GND           | GND       | DP_M2C_P6     | GND       |

| 17 | HA_N17       | GND          | LA_N11     | GND        | HA_N15    | GND       | LA_P13        | GND       | DP_M2C_N6     | GND       |

| 18 | GND          | HA_P18       | GND        | LA_P16     | GND       | HA_P20    | LA_N13        | LA_P14    | GND           | DP_M2C_P5 |

| 19 | HA_P21       | HA_N18       | LA_P15     | LA_N16     | HA_P19    | HA_N20    | GND           | LA_N14    | GND           | DP_M2C_N5 |

| 20 | HA_N21       | GND          | LA_N15     | GND        | HA_N19    | GND       | LA_P17        | GND       | GBTCLK_M2C_P1 | GND       |

| 21 | GND          | HA_P22       | GND        | LA_P20     | GND       | HB_P3     | LA_N17        | GND       | GBTCLK_M2C_N1 | GND       |

| 22 | HA_P23       | HA_N22       | LA_P19     | LA_N20     | HB_P2     | HB_N3     | GND           | LA_P18    | GND           | DP_C2M_P1 |

| 23 | HA_N23       | GND          | LA_N19     | GND        | HB_N2     | GND       | LA_P23        | LA_N18    | GND           | DP_C2M_N1 |

| 24 | GND          | HB_P1        | GND        | LA_P22     | GND       | HB_P5     | LA_N23        | GND       | DP_C2M_P9     | GND       |

| 25 | HB_P0        | HB_N1        | LA_P21     | LA_N22     | HB_P4     | HB_N5     | GND           | GND       | DP_C2M_N9     | GND       |

| 26 | HB_N0        | GND          | LA_N21     | GND        | HB_N4     | GND       | LA_P26        | LA_P27    | GND           | DP_C2M_P2 |

| 27 | GND          | HB_P7        | GND        | LA_P25     | GND       | HB_P9     | LA_N26        | LA_N27    | GND           | DP_C2M_N2 |

| 28 | HB_P6        | HB_N7        | LA_P24     | LA_N25     | HB_P8     | HB_N9     | GND           | GND       | DP_C2M_P8     | GND       |

| 29 | HB_N6        | GND          | LA_N24     | GND        | HB_N8     | GND       | JTAG_TCK      | GND       | DP_C2M_N8     | GND       |

| 30 | GND          | HB_P11       | GND        | LA_P29     | GND       | HB_P13    | JTAG_TDI      | SCL       | GND           | DP_C2M_P3 |

| 31 | HB_P10       | HB_N11       | LA_P28     | LA_N29     | HB_P12    | HB_N13    | JTAG_TDO      | SDA       | GND           | DP_C2M_N3 |

| 32 | HB_N10       | GND          | LA_N28     | GND        | HB_N12    | GND       | VCC3P3        | GND       | DP_C2M_P7     | GND       |

| 33 | GND          | HB_P15       | GND        | LA_P31     | GND       | HB_P19    | JTAG_TMS      | GND       | DP_C2M_N7     | GND       |

| 34 | HB_P14       | HB_N15       | LA_P30     | LA_N31     | HB_P16    | HB_N19    | JTAG_TRST     | GA0       | GND           | DP_C2M_P4 |

| 35 | HB_N14       | GND          | LA_N30     | GND        | HB_N16    | GND       | GA1           | VCC12     | GND           | DP_C2M_N4 |

| 36 | GND          | HB_P18       | GND        | LA_P33     | GND       | HB_P21    | VCC3P3        | GND       | DP_C2M_P6     | GND       |

| 37 | HB_P17       | HB_N18       | LA_P32     | LA_N33     | HB_P20    | HB_N21    | GND           | VCC12     | DP_C2M_N6     | GND       |

| 38 | HB_N17       | GND          | LA_N32     | GND        | HB_N20    | GND       | VCC3P3        | GND       | GND           | DP_C2M_P5 |

| 39 | GND          | NC           | GND        | VCCIO_FMC  | GND       | VCCIO_FMC | GND           | VCC3P3    | GND           | DP_C2M_N5 |

| 40 | NC           | GND          | VCCIO_FMC  | GND        | VCCIO_FMC | GND       | VCC3P3        | GND       | NC            | GND       |

Figure 2-9 FMC pin out table

**Table 2-14 FMC Connector Pin Assignments, Signal Names and Functions**

| rabio 2 1 1 1 m.o de impeter 1 m./teorgente, erginal ramico aria 1 anotiene |                    |                                                              |               |  |  |

|-----------------------------------------------------------------------------|--------------------|--------------------------------------------------------------|---------------|--|--|

| Signal Name                                                                 | FPGA Pin<br>Number | Description                                                  | I/O Standard  |  |  |

| FMC_CLK2_BIDIR_p                                                            | PIN_V24            | FMC data bus                                                 | FMC_VCCIO*(1) |  |  |

| FMC_CLK2_BIDIR_n                                                            | PIN_V23            | FMC data bus                                                 | FMC_VCCIO*(1) |  |  |

| FMC_CLK3_BIDIR_p                                                            | PIN_T20            | FMC data bus                                                 | FMC_VCCIO*(1) |  |  |

| FMC_CLK3_BIDIR_n                                                            | PIN_U20            | FMC data bus                                                 | FMC_VCCIO*(1) |  |  |

| FMC_CLK_M2C_p[0] *(3)                                                       | PIN_C22            | Clock from mezzanine module to carrier card positive 0       | FMC_VCCIO*(1) |  |  |

| FMC_CLK_M2C_n[0] *(3)                                                       | PIN_C21            | Clock from mezzanine<br>module to carrier card<br>negative 0 | FMC_VCCIO*(1) |  |  |

| FMC_CLK_M2C_p[1] *(3) | PIN_J16 | Clock from mezzanine<br>module to carrier card<br>positive 1 | FMC_VCCIO*(1) |

|-----------------------|---------|--------------------------------------------------------------|---------------|

| FMC_CLK_M2C_n[1] *(3) | PIN_H16 | Clock from mezzanine<br>module to carrier card<br>negative 1 | FMC_VCCIO*(1) |

| FMC_HA_p[0] *(3)      | PIN_P14 | FMC HA bank data p0                                          | FMC_VCCIO*(1) |

| FMC_HA_p[1] *(3)      | PIN_J13 | FMC HA bank data p1                                          | FMC_VCCIO*(1) |

| FMC_HA_p[2]           | PIN_V17 | FMC HA bank data p2                                          | FMC_VCCIO*(1) |

| FMC_HA_p[3]           | PIN_V18 | FMC HA bank data p3                                          | FMC_VCCIO*(1) |

| FMC_HA_p[4]           | PIN_R17 | FMC HA bank data p4                                          | FMC_VCCIO*(1) |

| FMC_HA_p[5]           | PIN_R19 | FMC HA bank data p5                                          | FMC_VCCIO*(1) |

| FMC_HA_p[6]           | PIN_T15 | FMC HA bank data p6                                          | FMC_VCCIO*(1) |

| FMC_HA_p[7]           | PIN_R13 | FMC HA bank data p7                                          | FMC_VCCIO*(1) |

| FMC_HA_p[8]           | PIN_P12 | FMC HA bank data p8                                          | FMC_VCCIO*(1) |

| FMC_HA_p[9]           | PIN_U19 | FMC HA bank data p9                                          | FMC_VCCIO*(1) |

| FMC_HA_p[10]          | PIN_J10 | FMC HA bank data p10                                         | FMC_VCCIO*(1) |

| FMC_HA_p[11]          | PIN_U17 | FMC HA bank data p11                                         | FMC_VCCIO*(1) |

| FMC_HA_p[12]          | PIN_P16 | FMC HA bank data p12                                         | FMC_VCCIO*(1) |

| FMC_HA_p[13]          | PIN_M14 | FMC HA bank data p13                                         | FMC_VCCIO*(1) |

| FMC_HA_p[14]          | PIN_L12 | FMC HA bank data p14                                         | FMC_VCCIO*(1) |

| FMC_HA_p[15]          | PIN_K12 | FMC HA bank data p15                                         | FMC_VCCIO*(1) |

| FMC_HA_p[16]          | PIN_L11 | FMC HA bank data p16                                         | FMC_VCCIO*(1) |

| FMC_HA_p[17]          | PIN_H11 | FMC HA bank data p17                                         | FMC_VCCIO*(1) |

| FMC_HA_p[18]          | PIN_E10 | FMC HA bank data p18                                         | FMC_VCCIO*(1) |

| FMC_HA_p[19]          | PIN_H12 | FMC HA bank data p19                                         | FMC_VCCIO*(1) |

| FMC_HA_p[20]          | PIN_E12 | FMC HA bank data p20                                         | FMC_VCCIO*(1) |

| FMC_HA_p[21]          | PIN_H10 | FMC HA bank data p21                                         | FMC_VCCIO*(1) |

| FMC_HA_p[22]     | PIN_F11 | FMC HA bank data p22 | FMC_VCCIO*(1) |

|------------------|---------|----------------------|---------------|

| FMC_HA_p[23]     | PIN_D11 | FMC HA bank data p23 | FMC_VCCIO*(1) |

| FMC_HA_n[0] *(3) | PIN_N13 | FMC HA bank data n0  | FMC_VCCIO*(1) |

| FMC_HA_n[1] *(3) | PIN_K13 | FMC HA bank data n1  | FMC_VCCIO*(1) |

| FMC_HA_n[2]      | PIN_W18 | FMC HA bank data n2  | FMC_VCCIO*(1) |

| FMC_HA_n[3]      | PIN_U18 | FMC HA bank data n3  | FMC_VCCIO*(1) |

| FMC_HA_n[4]      | PIN_R16 | FMC HA bank data n4  | FMC_VCCIO*(1) |

| FMC_HA_n[5]      | PIN_R18 | FMC HA bank data n5  | FMC_VCCIO*(1) |

| FMC_HA_n[6]      | PIN_T16 | FMC HA bank data n6  | FMC_VCCIO*(1) |

| FMC_HA_n[7]      | PIN_R14 | FMC HA bank data n7  | FMC_VCCIO*(1) |

| FMC_HA_n[8]      | PIN_P13 | FMC HA bank data n8  | FMC_VCCIO*(1) |

| FMC_HA_n[9]      | PIN_T19 | FMC HA bank data n9  | FMC_VCCIO*(1) |

| FMC_HA_n[10]     | PIN_K10 | FMC HA bank data n10 | FMC_VCCIO*(1) |

| FMC_HA_n[11]     | PIN_T17 | FMC HA bank data n11 | FMC_VCCIO*(1) |

| FMC_HA_n[12]     | PIN_P15 | FMC HA bank data n12 | FMC_VCCIO*(1) |

| FMC_HA_n[13]     | PIN_M13 | FMC HA bank data n13 | FMC_VCCIO*(1) |

| FMC_HA_n[14]     | PIN_M12 | FMC HA bank data n14 | FMC_VCCIO*(1) |

| FMC_HA_n[15]     | PIN_K11 | FMC HA bank data n15 | FMC_VCCIO*(1) |

| FMC_HA_n[16]     | PIN_L10 | FMC HA bank data n16 | FMC_VCCIO*(1) |

| FMC_HA_n[17]     | PIN_J11 | FMC HA bank data n17 | FMC_VCCIO*(1) |

| FMC_HA_n[18]     | PIN_F10 | FMC HA bank data n18 | FMC_VCCIO*(1) |

| FMC_HA_n[19]     | PIN_G12 | FMC HA bank data n19 | FMC_VCCIO*(1) |

| FMC_HA_n[20]     | PIN_F12 | FMC HA bank data n20 | FMC_VCCIO*(1) |

| FMC_HA_n[21]     | PIN_G10 | FMC HA bank data n21 | FMC_VCCIO*(1) |

| FMC_HA_n[22]     | PIN_E11 | FMC HA bank data n22 | FMC_VCCIO*(1) |

| FMC_HA_n[23]     | PIN_D10 | FMC HA bank data n23 | FMC_VCCIO*(1) |

| FMC_HB_p[0] *(3) | PIN_E16 | FMC HB bank data p0  | FMC_VCCIO*(1) |

|                  |         |                      |               |

| FMC_HB_p[1]      | PIN_L15 | FMC HB bank data p1  | FMC_VCCIO*(1) |

|------------------|---------|----------------------|---------------|

| FMC_HB_p[2]      | PIN_L17 | FMC HB bank data p2  | FMC_VCCIO*(1) |

| FMC_HB_p[3]      | PIN_N15 | FMC HB bank data p3  | FMC_VCCIO*(1) |

| FMC_HB_p[4]      | PIN_H15 | FMC HB bank data p4  | FMC_VCCIO*(1) |

| FMC_HB_p[5]      | PIN_N16 | FMC HB bank data p5  | FMC_VCCIO*(1) |

| FMC_HB_p[6]      | PIN_G15 | FMC HB bank data p6  | FMC_VCCIO*(1) |

| FMC_HB_p[7]      | PIN_P18 | FMC HB bank data p7  | FMC_VCCIO*(1) |

| FMC_HB_p[8]      | PIN_L16 | FMC HB bank data p8  | FMC_VCCIO*(1) |

| FMC_HB_p[9]      | PIN_M17 | FMC HB bank data p9  | FMC_VCCIO*(1) |

| FMC_HB_p[10]     | PIN_E13 | FMC HB bank data p10 | FMC_VCCIO*(1) |

| FMC_HB_p[11]     | PIN_C15 | FMC HB bank data p11 | FMC_VCCIO*(1) |

| FMC_HB_p[12]     | PIN_G13 | FMC HB bank data p12 | FMC_VCCIO*(1) |

| FMC_HB_p[13]     | PIN_K14 | FMC HB bank data p13 | FMC_VCCIO*(1) |

| FMC_HB_p[14]     | PIN_G14 | FMC HB bank data p14 | FMC_VCCIO*(1) |

| FMC_HB_p[15]     | PIN_A16 | FMC HB bank data p15 | FMC_VCCIO*(1) |

| FMC_HB_p[16]     | PIN_C13 | FMC HB bank data p16 | FMC_VCCIO*(1) |

| FMC_HB_p[17]     | PIN_C16 | FMC HB bank data p17 | FMC_VCCIO*(1) |

| FMC_HB_p[18]     | PIN_E14 | FMC HB bank data p18 | FMC_VCCIO*(1) |

| FMC_HB_p[19]     | PIN_A14 | FMC HB bank data p19 | FMC_VCCIO*(1) |

| FMC_HB_p[20]     | PIN_B14 | FMC HB bank data p20 | FMC_VCCIO*(1) |

| FMC_HB_p[21]     | PIN_B12 | FMC HB bank data p21 | FMC_VCCIO*(1) |

| FMC_HB_n[0] *(3) | PIN_F16 | FMC HB bank data n0  | FMC_VCCIO*(1) |

| FMC_HB_n[1]      | PIN_L14 | FMC HB bank data n1  | FMC_VCCIO*(1) |

| FMC_HB_n[2]      | PIN_K17 | FMC HB bank data n2  | FMC_VCCIO*(1) |

| FMC_HB_n[3]      | PIN_M15 | FMC HB bank data n3  | FMC_VCCIO*(1) |

| FMC_HB_n[4]      | PIN_J15 | FMC HB bank data n4  | FMC_VCCIO*(1) |

| FMC_HB_n[5]      | PIN_N17 | FMC HB bank data n5  | FMC_VCCIO*(1) |

|                  |         |                      |               |

User Manual

| FMC_HB_n[6]  | PIN_F15 | FMC HB bank data n6  | FMC_VCCIO*(1) |

|--------------|---------|----------------------|---------------|

| FMC_HB_n[7]  | PIN_N18 | FMC HB bank data n7  | FMC_VCCIO*(1) |

| FMC_HB_n[8]  | PIN_K16 | FMC HB bank data n8  | FMC_VCCIO*(1) |

| FMC_HB_n[9]  | PIN_M18 | FMC HB bank data n9  | FMC_VCCIO*(1) |

| FMC_HB_n[10] | PIN_D13 | FMC HB bank data n10 | FMC_VCCIO*(1) |

| FMC_HB_n[11] | PIN_D15 | FMC HB bank data n11 | FMC_VCCIO*(1) |

| FMC_HB_n[12] | PIN_H13 | FMC HB bank data n12 | FMC_VCCIO*(1) |

| FMC_HB_n[13] | PIN_J14 | FMC HB bank data n13 | FMC_VCCIO*(1) |

| FMC_HB_n[14] | PIN_F14 | FMC HB bank data n14 | FMC_VCCIO*(1) |

| FMC_HB_n[15] | PIN_B15 | FMC HB bank data n15 | FMC_VCCIO*(1) |

| FMC_HB_n[16] | PIN_C12 | FMC HB bank data n16 | FMC_VCCIO*(1) |

| FMC_HB_n[17] | PIN_D16 | FMC HB bank data n17 | FMC_VCCIO*(1) |

| FMC_HB_n[18] | PIN_D14 | FMC HB bank data n18 | FMC_VCCIO*(1) |

| FMC_HB_n[19] | PIN_A15 | FMC HB bank data n19 | FMC_VCCIO*(1) |

| FMC_HB_n[20] | PIN_B13 | FMC HB bank data n20 | FMC_VCCIO*(1) |

| FMC_HB_n[21] | PIN_A12 | FMC HB bank data n21 | FMC_VCCIO*(1) |

| FMC_LA_p[0]  | PIN_J20 | FMC LA bank data p0  | FMC_VCCIO*(1) |

| FMC_LA_p[1]  | PIN_E18 | FMC LA bank data p1  | FMC_VCCIO*(1) |

| FMC_LA_p[2]  | PIN_K21 | FMC LA bank data p2  | FMC_VCCIO*(1) |

| FMC_LA_p[3]  | PIN_K19 | FMC LA bank data p3  | FMC_VCCIO*(1) |

| FMC_LA_p[4]  | PIN_P21 | FMC LA bank data p4  | FMC_VCCIO*(1) |

| FMC_LA_p[5]  | PIN_M20 | FMC LA bank data p5  | FMC_VCCIO*(1) |

| FMC_LA_p[6]  | PIN_J18 | FMC LA bank data p6  | FMC_VCCIO*(1) |

| FMC_LA_p[7]  | PIN_G18 | FMC LA bank data p7  | FMC_VCCIO*(1) |

| FMC_LA_p[8]  | PIN_P20 | FMC LA bank data p8  | FMC_VCCIO*(1) |

| FMC_LA_p[9]  | PIN_G20 | FMC LA bank data p9  | FMC_VCCIO*(1) |

| FMC_LA_p[10] | PIN_J21 | FMC LA bank data p10 | FMC_VCCIO*(1) |

|              |         |                      |               |

| FMC_LA_p[11] | PIN_E19 | FMC LA bank data p11 | FMC_VCCIO*(1) |

|--------------|---------|----------------------|---------------|

| FMC_LA_p[12] | PIN_A19 | FMC LA bank data p12 | FMC_VCCIO*(1) |

| FMC_LA_p[13] | PIN_E21 | FMC LA bank data p13 | FMC_VCCIO*(1) |

| FMC_LA_p[14] | PIN_F20 | FMC LA bank data p14 | FMC_VCCIO*(1) |

| FMC_LA_p[15] | PIN_G19 | FMC LA bank data p15 | FMC_VCCIO*(1) |

| FMC_LA_p[16] | PIN_F17 | FMC LA bank data p16 | FMC_VCCIO*(1) |

| FMC_LA_p[17] | PIN_C17 | FMC LA bank data p17 | FMC_VCCIO*(1) |

| FMC_LA_p[18] | PIN_D20 | FMC LA bank data p18 | FMC_VCCIO*(1) |

| FMC_LA_p[19] | PIN_A22 | FMC LA bank data p19 | FMC_VCCIO*(1) |

| FMC_LA_p[20] | PIN_B18 | FMC LA bank data p20 | FMC_VCCIO*(1) |

| FMC_LA_p[21] | PIN_A20 | FMC LA bank data p21 | FMC_VCCIO*(1) |

| FMC_LA_p[22] | PIN_A17 | FMC LA bank data p22 | FMC_VCCIO*(1) |

| FMC_LA_p[23] | PIN_B24 | FMC LA bank data p23 | FMC_VCCIO*(1) |

| FMC_LA_p[24] | PIN_K24 | FMC LA bank data p24 | FMC_VCCIO*(1) |

| FMC_LA_p[25] | PIN_P23 | FMC LA bank data p25 | FMC_VCCIO*(1) |

| FMC_LA_p[26] | PIN_E22 | FMC LA bank data p26 | FMC_VCCIO*(1) |

| FMC_LA_p[27] | PIN_J23 | FMC LA bank data p27 | FMC_VCCIO*(1) |

| FMC_LA_p[28] | PIN_F24 | FMC LA bank data p28 | FMC_VCCIO*(1) |

| FMC_LA_p[29] | PIN_G22 | FMC LA bank data p29 | FMC_VCCIO*(1) |

| FMC_LA_p[30] | PIN_E24 | FMC LA bank data p30 | FMC_VCCIO*(1) |

| FMC_LA_p[31] | PIN_C23 | FMC LA bank data p31 | FMC_VCCIO*(1) |

| FMC_LA_p[32] | PIN_D24 | FMC LA bank data p32 | FMC_VCCIO*(1) |

| FMC_LA_p[33] | PIN_A25 | FMC LA bank data p33 | FMC_VCCIO*(1) |

| FMC_LA_n[0]  | PIN_J19 | FMC LA bank data n0  | FMC_VCCIO*(1) |

| FMC_LA_n[1]  | PIN_D18 | FMC LA bank data n1  | FMC_VCCIO*(1) |

| FMC_LA_n[2]  | PIN_L21 | FMC LA bank data n2  | FMC_VCCIO*(1) |

| FMC_LA_n[3]  | PIN_L19 | FMC LA bank data n3  | FMC_VCCIO*(1) |

|              |         |                      |               |

| FMC_LA_n[4]  | PIN_N21 | FMC LA bank data n4  | FMC_VCCIO*(1) |

|--------------|---------|----------------------|---------------|

| FMC_LA_n[5]  | PIN_L20 | FMC LA bank data n5  | FMC_VCCIO*(1) |

| FMC_LA_n[6]  | PIN_K18 | FMC LA bank data n6  | FMC_VCCIO*(1) |

| FMC_LA_n[7]  | PIN_H18 | FMC LA bank data n7  | FMC_VCCIO*(1) |

| FMC_LA_n[8]  | PIN_N20 | FMC LA bank data n8  | FMC_VCCIO*(1) |

| FMC_LA_n[9]  | PIN_H20 | FMC LA bank data n9  | FMC_VCCIO*(1) |

| FMC_LA_n[10] | PIN_H21 | FMC LA bank data n10 | FMC_VCCIO*(1) |

| FMC_LA_n[11] | PIN_D19 | FMC LA bank data n11 | FMC_VCCIO*(1) |

| FMC_LA_n[12] | PIN_B20 | FMC LA bank data n12 | FMC_VCCIO*(1) |

| FMC_LA_n[13] | PIN_D21 | FMC LA bank data n13 | FMC_VCCIO*(1) |

| FMC_LA_n[14] | PIN_F21 | FMC LA bank data n14 | FMC_VCCIO*(1) |

| FMC_LA_n[15] | PIN_F19 | FMC LA bank data n15 | FMC_VCCIO*(1) |

| FMC_LA_n[16] | PIN_E17 | FMC LA bank data n16 | FMC_VCCIO*(1) |

| FMC_LA_n[17] | PIN_C18 | FMC LA bank data n17 | FMC_VCCIO*(1) |

| FMC_LA_n[18] | PIN_C20 | FMC LA bank data n18 | FMC_VCCIO*(1) |

| FMC_LA_n[19] | PIN_B22 | FMC LA bank data n19 | FMC_VCCIO*(1) |

| FMC_LA_n[20] | PIN_B19 | FMC LA bank data n20 | FMC_VCCIO*(1) |

| FMC_LA_n[21] | PIN_A21 | FMC LA bank data n21 | FMC_VCCIO*(1) |

| FMC_LA_n[22] | PIN_B17 | FMC LA bank data n22 | FMC_VCCIO*(1) |

| FMC_LA_n[23] | PIN_A24 | FMC LA bank data n23 | FMC_VCCIO*(1) |

| FMC_LA_n[24] | PIN_J24 | FMC LA bank data n24 | FMC_VCCIO*(1) |

| FMC_LA_n[25] | PIN_R23 | FMC LA bank data n25 | FMC_VCCIO*(1) |

| FMC_LA_n[26] | PIN_F22 | FMC LA bank data n26 | FMC_VCCIO*(1) |

| FMC_LA_n[27] | PIN_K23 | FMC LA bank data n27 | FMC_VCCIO*(1) |

| FMC_LA_n[28] | PIN_G24 | FMC LA bank data n28 | FMC_VCCIO*(1) |

| FMC_LA_n[29] | PIN_H22 | FMC LA bank data n29 | FMC_VCCIO*(1) |

| FMC_LA_n[30] | PIN_E23 | FMC LA bank data n30 | FMC_VCCIO*(1) |

|              |         |                      |               |

User Manual

| FMC_LA_n[31]        | PIN_B23  | FMC LA bank data n31                                                       | FMC_VCCIO*(1)               |

|---------------------|----------|----------------------------------------------------------------------------|-----------------------------|

| FMC_LA_n[32]        | PIN_D23  | FMC LA bank data n32                                                       | FMC_VCCIO*(1)               |

| FMC_LA_n[33]        | PIN_A26  | FMC LA bank data n33                                                       | FMC_VCCIO*(1)               |

| FMC_GBTCLK_M2C_p[0] | PIN_AM12 | LVDS input from the installed FMC card to dedicated reference clock inputs | LVDS                        |

| FMC_GBTCLK_M2C_p[1] | PIN_T9   | LVDS input from the installed FMC card to dedicated reference clock inputs | LVDS                        |

| FMC_REFCLK_p        | PIN_T31  | FPGA transceiver Reference<br>Clock (From on-board PLL)                    | LVDS                        |

| FMC_DP_C2M_p[0]     | PIN_AK1  | Transmit pair p0 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[1]     | PIN_AL3  | Transmit pair p1 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[2]     | PIN_AH1  | Transmit pair p2 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[3]     | PIN_AJ3  | Transmit pair p3 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[4]     | PIN_AF1  | Transmit pair p4 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[5]     | PIN_AG3  | Transmit pair p5 of the FPGA transceiver                                   | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[6]     | PIN_F1   | Transmit pair p6 of the FPGA                                               | HSSI                        |

|                 |         | transceiver                              | DIFFERENTIAL I/O            |

|-----------------|---------|------------------------------------------|-----------------------------|

| FMC_DP_C2M_p[7] | PIN_G3  | Transmit pair p7 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[8] | PIN_E3  | Transmit pair p8 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_C2M_p[9] | PIN_C3  | Transmit pair p9 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[0] | PIN_AL7 | Receiver pair p0 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[1] | PIN_AH5 | Receiver pair p1 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[2] | PIN_AJ7 | Receiver pair p2 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[3] | PIN_AF5 | Receiver pair p3 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[4] | PIN_AG7 | Receiver pair p4 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[5] | PIN_AE7 | Receiver pair p5 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[6] | PIN_G7  | Receiver pair p6 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[7] | PIN_D5   | Receiver pair p7 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

|-----------------|----------|------------------------------------------|-----------------------------|

| FMC_DP_M2C_p[8] | PIN_C7   | Receiver pair p8 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_DP_M2C_p[9] | PIN_A7   | Receiver pair p9 of the FPGA transceiver | HSSI<br>DIFFERENTIAL<br>I/O |

| FMC_GA[0]       | PIN_R21  | FMC geographical address 0               | 3.3 V*(2)                   |

| FMC_GA[1]       | PIN_T21  | FMC geographical address 1               | 3.3 V*(2)                   |

| FMC_SCL         | PIN_V21  | Management serial clock line             | 3.3 V*(2)                   |

| FMC_SDA         | PIN_V22  | Management serial data line              | 3.3 V*(2)                   |

| FMC_RES[0]      | PIN_AH16 | Reserved                                 | 3.0 V                       |

- \*(1): The FMC\_VCCIO value depends on the setting of JP2, which can adjust the FMC\_VCCIO to 1.2V, 1.5V or 1.8V. Please refer to section 2.2: "FMC\_VCCIO and FMCP\_VCCIO Select Header" for details.

- \*(2): There are level shift ICs that convert FMC\_VCCIO to 3.3V between the FPGA pins and the FMC pins.

- \*(3): FPGA dedicated clock input pin.

# 2.6 FMC+ Connector

In addition to an FMC connector on the Apollo S10 board, there is also an FMC + connector for expanding FPGA I/Os (See **Figure 2-10**). FMC+ is the latest Standard in the popular VITA FMC family. The main difference between FMC + and FMC specifications is that the number of FMC + transceiver can provide up to 24 pairs (**High Serial Pin Count version, HSPC**).

Figure 2-10 FMC+ connector on Apollo S10 board

As the number of transceivers increases, the connector size of the FMC+ becomes a 14x40 array, compared to the 10x40 array of the FMC.

Below we will introduce according to the individual functions of FMC+ connector.

### ■ Compare the FMC and FMC+

**Table 2-15** lists the number of I/O, power, transceiver, clock and other interfaces provided by FMC and FMC + connector on the Apollo S10 board.

Table 2-15 FMC and FMC+ compare list on the Apollo S10 board

| Parameter                | FMC (J2)                | FMC+(J1)                |

|--------------------------|-------------------------|-------------------------|

| Number of DIFF/SE I/O    | 80 DIFF/160 SE          | 80 DIFF/160 SE          |

| M2C Clocks (DIFF)        | 2                       | 2                       |

| SYNC M2C+C2M (DIFF)      | -                       | 1+1                     |

| REFCLK M2C+C2M (DIFF)    | -                       | 1+1                     |

| Gigabit Transceivers     | 10                      | 24                      |

| Gigabit reference clocks | 2                       | 6                       |

| Miscellaneous            | JTAG, SYNC, Power Good, | JTAG, SYNC, Power Good, |

|                          | Geographic              | Geographic              |

|                | Address                        | Address                       |

|----------------|--------------------------------|-------------------------------|

| Power supplies | VADJ(4 pins), 3V3(4 pins), 12V | VADJ(4 pins), 3V3(4 pins),    |

|                | (2 pins), 3V3 Aux (1 pin)      | 12V (2 pins), 3V3 Aux (1 pin) |

#### ■ Clock Interface

**Table 2-16** shows the FPGA dedicated clock input pin placement on the FMC+ connector.

**Table 2-16 FMCP clock input interface distribution**

| Signal Name       | FMC Clock in/out pin | FPGA Clock Input Pin | FPGA<br>Pin |

|-------------------|----------------------|----------------------|-------------|

| 3.ga              | name                 | Placement            | Assignment  |

| FMCP_CLK_M2C_p0   | CLK0_M2C_P           | CLK_2C_1P            | ВН36        |

| FMCP_CLK_M2C_n0   | CLK0_M2C_N           | CLK_2C_1N            | BH37        |

| FMCP_CLK_M2C_p1   | CLK1_M2C_P           | CLK_2B_0P            | AW36        |

| FMCP_CLK_M2C_n1   | CLK1_M2C_N           | CLK_2B_0N            | AV36        |

| FMCP_HA_p0        | HA00_P_CC            | CLK_2A_0P            | BE31        |

| FMCP_HA_n0        | HA00_N_CC            | CLK_2A_0N            | BD31        |

| FMCP_HA_p1        | HA01_P_CC            | CLK_2A_1P            | AW30        |

| FMCP_HA_n1        | HA01_N_CC            | CLK_2A_1N            | AV36        |

| FMCP_HB_p0        | HB00_P_CC            | CLK_2F_1P            | AN27        |

| FMCP_HB_n0        | HB00_N_CC            | CLK_2F_1N            | AN28        |

| FMCP_LA_p0        | LA00_P_CC            | CLK_2C_0P            | AW38        |

| FMCP_LA_p0        | LA00_N_CC            | CLK_2C_0N            | AW39        |

| FMCP_REFCLK_M2C_p | REFCLK_M2C_P         | CLK_2B_1P            | BH33        |

| FMCP_REFCLK_M2C_n | REFCLK_M2C_N         | CLK_2B_1N            | BG33        |

#### Power Supply

The Apollo S10 board provides 12V, 3.3V and VCCIO\_FMCP power through FMC+ port. **Table 2-17** indicates the maximum power consumption for the FMC+ connector.

CAUTION: Before powering on the Apollo S10 board with a daughter card, please check to see if there is a short circuit between the power pins and FPGA

Table 2-17 Power Supply of the FMC

| Supplied Voltage | Max. Current Limit |

|------------------|--------------------|

| 12V              | 1A                 |

| 3.3V             | 3A                 |

| VCCIO_FMCP       | 4A                 |

#### ■ Adjustable I/O Standards

The FPGA I/O standards of the FMC+ ports can be adjusted by configuring the header position. Each port can be individually adjusted to 1.2V, 1.5V or 1.8V via jumper JP3 on the Apollo S10 board. For detailed setting, please refer to Section 2.2: FMC\_VCCIO and FMCP\_VCCIO Select Header.

#### JTAG Chain on FMC

The JTAG chain on the Apollo S10 board supports JTAG interface extension to the FMC+ connector so that the JTAG device on the user's FMC+ daughter card can be joined with JTAG chain on the Apollo S10 board. Users can enable this feature through the switch (SW4.1) on the Apollo S10 board. In the board's default setting, the JTAG interface of the FMC connector is bypassed to keep the Apollo S10 board JTAG chain to maintain close loop. For detailed setting, please refer to Section 2.2: JTAG Interface Switch.

#### Transceiver Channels Speed

There are **24** transceivers connected to the Stratix 10 FPGA on the FMCP connector, **5** of which belong to the GX channels, and the maximum transmission speed is 17.4 Gbps. The other 19 belong to GXT channels, and the maximum transmission speed can reach 25Gbps. For details, please to see "Intel ® Stratix® 10 L- and H-Tile Transceiver PHY User Guide" for section "1.3. L-Tile / H-Tile Building Blocks". **Table 2-18** lists the distribution and speed of the two channels of the FMCP connector.

Table 2-18 GX and GXT channels on the FMCP connector

| Transceiver channel<br>Type | Net Name                         | Speed     |

|-----------------------------|----------------------------------|-----------|

| GX Channels                 | FMCP_DP_M2C_p2/ FMCP_DP_C2M_p2 , | 17.4 Gbps |

|              | FMCP_DP_M2C_p5/ FMCP_DP_C2M_p5 ,   |         |

|--------------|------------------------------------|---------|

|              | FMCP_DP_M2C_p8/ FMCP_DP_C2M_p8,    |         |

|              | FMCP_DP_M2C_p11/ FMCP_DP_C2M_p11 , |         |

|              | FMCP_DP_M2C_p14/ FMCP_DP_C2M_p14   |         |

|              | FMC_DP_M2C_p0/ FMC_DP_C2M_p0 ,     |         |

|              | FMC_DP_M2C_p1/ FMC_DP_C2M_p1 ,     |         |

|              | FMC_DP_M2C_p3/ FMC_DP_C2M_p3,      |         |

|              | FMC_DP_M2C_p4/ FMC_DP_C2M_p4,      |         |

|              | FMC_DP_M2C_p6/ FMC_DP_C2M_p6,      |         |

|              | FMC_DP_M2C_p7/ FMC_DP_C2M_p7,      |         |

|              | FMC_DP_M2C_p9/ FMC_DP_C2M_p9,      |         |

|              | FMC_DP_M2C_p10/ FMC_DP_C2M_p10 ,   |         |

|              | FMC_DP_M2C_p12/ FMC_DP_C2M_p12 ,   |         |

|              | FMC_DP_M2C_p13/ FMC_DP_C2M_p13 ,   |         |

| GXT Channels | FMC_DP_M2C_p15/ FMC_DP_C2M_p15,    | 25 Gbps |

|              | FMC_DP_M2C_p16/ FMC_DP_C2M_p16,    |         |

|              | FMC_DP_M2C_p17/ FMC_DP_C2M_p17,    |         |

|              | FMC_DP_M2C_p18/ FMC_DP_C2M_p18,    |         |

|              | FMC_DP_M2C_p19/ FMC_DP_C2M_p19,    |         |

|              | FMC_DP_M2C_p20/ FMC_DP_C2M_p20 ,   |         |

|              | FMC_DP_M2C_p21/ FMC_DP_C2M_p21 ,   |         |

|              | FMC_DP_M2C_p22/ FMC_DP_C2M_p22 ,   |         |

|              | FMC_DP_M2C_p23/ FMC_DP_C2M_p23     |         |

|              |                                    |         |

|              |                                    |         |

## **■** FPGA Pin Assignments for FMCP Connector

**Figure 2-11** shows the pin out table of the FMC connector on the Apollo S10 and **Table 2-19** lists the FMC connector pin assignments, signal names and function.

Figure 2-11 FMC+ pin out table

Table 2-19 FMCP Connector Pin Assignments, Signal Names and Functions

| Table 2-13 1 Mor Confidence of Till Assignments, Signal Names and Tunctions |                    |                                                              |                |

|-----------------------------------------------------------------------------|--------------------|--------------------------------------------------------------|----------------|

| Signal Name                                                                 | FPGA Pin<br>Number | Description                                                  | I/O Standard   |

| FMCP_CLK2_BIDIR_p                                                           | PIN_AW33           | FMCP data bus                                                | FMCP_VCCIO*(1) |

| FMCP_CLK2_BIDIR_n                                                           | PIN_AY33           | FMCP data bus                                                | FMCP_VCCIO*(1) |

| FMCP_CLK3_BIDIR_p                                                           | PIN_AW34           | FMCP data bus                                                | FMCP_VCCIO*(1) |

| FMCP_CLK3_BIDIR_n                                                           | PIN_AW35           | FMCP data bus                                                | FMCP_VCCIO*(1) |

| FMCP_CLK_M2C_p[0]                                                           | PIN_ BH36          | Clock from mezzanine module to carrier card positive 0       | FMCP_VCCIO*(1) |

| FMCP_CLK_M2C_n[0]                                                           | PIN_BH37           | Clock from mezzanine<br>module to carrier card<br>negative 0 | FMCP_VCCIO*(1) |

| FMCP_CLK_M2C_p[1]                                                           | PIN_ AW36          | Clock from mezzanine<br>module to carrier card<br>positive 1 | FMCP_VCCIO*(1) |

| FMCP_CLK_M2C_n[1]                                                           | PIN_AV36           | Clock from mezzanine                                         | FMCP_VCCIO*(1) |

|               |          | module to carrier card negative 1 |                |

|---------------|----------|-----------------------------------|----------------|

| FMCP_HA_p[0]  | PIN_BE31 | FMCP HA bank data p0              | FMCP_VCCIO*(1) |

| FMCP_HA_p[1]  | PIN_AW30 | FMCP HA bank data p1              | FMCP_VCCIO*(1) |

| FMCP_HA_p[2]  | PIN_BC30 | FMCP HA bank data p2              | FMCP_VCCIO*(1) |

| FMCP_HA_p[3]  | PIN_AW28 | FMCP HA bank data p3              | FMCP_VCCIO*(1) |

| FMCP_HA_p[4]  | PIN_AT29 | FMCP HA bank data p4              | FMCP_VCCIO*(1) |

| FMCP_HA_p[5]  | PIN_AU29 | FMCP HA bank data p5              | FMCP_VCCIO*(1) |

| FMCP_HA_p[6]  | PIN_BD29 | FMCP HA bank data p6              | FMCP_VCCIO*(1) |

| FMCP_HA_p[7]  | PIN_BC31 | FMCP HA bank data p7              | FMCP_VCCIO*(1) |

| FMCP_HA_p[8]  | PIN_AU30 | FMCP HA bank data p8              | FMCP_VCCIO*(1) |

| FMCP_HA_p[9]  | PIN_BA29 | FMCP HA bank data p9              | FMCP_VCCIO*(1) |

| FMCP_HA_p[10] | PIN_BE32 | FMCP HA bank data p10             | FMCP_VCCIO*(1) |

| FMCP_HA_p[11] | PIN_BG29 | FMCP HA bank data p11             | FMCP_VCCIO*(1) |

| FMCP_HA_p[12] | PIN_AY31 | FMCP HA bank data p12             | FMCP_VCCIO*(1) |

| FMCP_HA_p[13] | PIN_AY29 | FMCP HA bank data p13             | FMCP_VCCIO*(1) |

| FMCP_HA_p[14] | PIN_BF31 | FMCP HA bank data p14             | FMCP_VCCIO*(1) |

| FMCP_HA_p[15] | PIN_BA32 | FMCP HA bank data p15             | FMCP_VCCIO*(1) |

| FMCP_HA_p[16] | PIN_BA31 | FMCP HA bank data p16             | FMCP_VCCIO*(1) |

| FMCP_HA_p[17] | PIN_BH32 | FMCP HA bank data p17             | FMCP_VCCIO*(1) |

| FMCP_HA_p[18] | PIN_BH31 | FMCP HA bank data p18             | FMCP_VCCIO*(1) |

| FMCP_HA_p[19] | PIN_BF29 | FMCP HA bank data p19             | FMCP_VCCIO*(1) |

| FMCP_HA_p[20] | PIN_BB30 | FMCP HA bank data p20             | FMCP_VCCIO*(1) |

| FMCP_HA_p[21] | PIN_BG30 | FMCP HA bank data p21             | FMCP_VCCIO*(1) |

| FMCP_HA_p[22] | PIN_BJ30 | FMCP HA bank data p22             | FMCP_VCCIO*(1) |

| FMCP_HA_p[23] | PIN_BJ28 | FMCP HA bank data p23             | FMCP_VCCIO*(1) |

| FMCP_HA_n[0]  | PIN_BD31 | FMCP HA bank data n0              | FMCP_VCCIO*(1) |

| FMCP_HA_n[1]  | PIN_AW31 | FMCP HA bank data n1              | FMCP_VCCIO*(1) |

| FMCP_HA_n[2]  | PIN_BD30 | FMCP HA bank data n2  | FMCP_VCCIO*(1) |

|---------------|----------|-----------------------|----------------|

| FMCP_HA_n[3]  | PIN_AV28 | FMCP HA bank data n3  | FMCP_VCCIO*(1) |

| FMCP_HA_n[4]  | PIN_AT30 | FMCP HA bank data n4  | FMCP_VCCIO*(1) |

| FMCP_HA_n[5]  | PIN_AU28 | FMCP HA bank data n5  | FMCP_VCCIO*(1) |

| FMCP_HA_n[6]  | PIN_BE29 | FMCP HA bank data n6  | FMCP_VCCIO*(1) |

| FMCP_HA_n[7]  | PIN_BC32 | FMCP HA bank data n7  | FMCP_VCCIO*(1) |

| FMCP_HA_n[8]  | PIN_AV30 | FMCP HA bank data n8  | FMCP_VCCIO*(1) |

| FMCP_HA_n[9]  | PIN_BB28 | FMCP HA bank data n9  | FMCP_VCCIO*(1) |

| FMCP_HA_n[10] | PIN_BF32 | FMCP HA bank data n10 | FMCP_VCCIO*(1) |

| FMCP_HA_n[11] | PIN_BG28 | FMCP HA bank data n11 | FMCP_VCCIO*(1) |

| FMCP_HA_n[12] | PIN_AY32 | FMCP HA bank data n12 | FMCP_VCCIO*(1) |

| FMCP_HA_n[13] | PIN_AW29 | FMCP HA bank data n13 | FMCP_VCCIO*(1) |

| FMCP_HA_n[14] | PIN_BF30 | FMCP HA bank data n14 | FMCP_VCCIO*(1) |

| FMCP_HA_n[15] | PIN_BB32 | FMCP HA bank data n15 | FMCP_VCCIO*(1) |

| FMCP_HA_n[16] | PIN_BA30 | FMCP HA bank data n16 | FMCP_VCCIO*(1) |

| FMCP_HA_n[17] | PIN_BG32 | FMCP HA bank data n17 | FMCP_VCCIO*(1) |

| FMCP_HA_n[18] | PIN_BJ31 | FMCP HA bank data n18 | FMCP_VCCIO*(1) |

| FMCP_HA_n[19] | PIN_BE28 | FMCP HA bank data n19 | FMCP_VCCIO*(1) |

| FMCP_HA_n[20] | PIN_BB29 | FMCP HA bank data n20 | FMCP_VCCIO*(1) |

| FMCP_HA_n[21] | PIN_BH30 | FMCP HA bank data n21 | FMCP_VCCIO*(1) |

| FMCP_HA_n[22] | PIN_BJ29 | FMCP HA bank data n22 | FMCP_VCCIO*(1) |

| FMCP_HA_n[23] | PIN_BH28 | FMCP HA bank data n23 | FMCP_VCCIO*(1) |

| FMCP_HB_p[0]  | PIN_AN27 | FMCP HB bank data p0  | FMCP_VCCIO*(1) |

| FMCP_HB_p[1]  | PIN_AP30 | FMCP HB bank data p1  | FMCP_VCCIO*(1) |

| FMCP_HB_p[2]  | PIN_AP25 | FMCP HB bank data p2  | FMCP_VCCIO*(1) |

| FMCP_HB_p[3]  | PIN_AP26 | FMCP HB bank data p3  | FMCP_VCCIO*(1) |

| FMCP_HB_p[4]  | PIN_AP28 | FMCP HB bank data p4  | FMCP_VCCIO*(1) |

|               |          |                       |                |

User Manual

| FMCP_HB_p[5]  | PIN_AV27 | FMCP HB bank data p5  | FMCP_VCCIO*(1) |

|---------------|----------|-----------------------|----------------|

| FMCP_HB_p[6]  | PIN_AR26 | FMCP HB bank data p6  | FMCP_VCCIO*(1) |

| FMCP_HB_p[7]  | PIN_AT27 | FMCP HB bank data p7  | FMCP_VCCIO*(1) |

| FMCP_HB_p[8]  | PIN_AY28 | FMCP HB bank data p8  | FMCP_VCCIO*(1) |

| FMCP_HB_p[9]  | PIN_AR28 | FMCP HB bank data p9  | FMCP_VCCIO*(1) |

| FMCP_HB_p[10] | PIN_BC28 | FMCP HB bank data p10 | FMCP_VCCIO*(1) |

| FMCP_HB_p[11] | PIN_AV25 | FMCP HB bank data p11 | FMCP_VCCIO*(1) |

| FMCP_HB_p[12] | PIN_BC27 | FMCP HB bank data p12 | FMCP_VCCIO*(1) |

| FMCP_HB_p[13] | PIN_AW26 | FMCP HB bank data p13 | FMCP_VCCIO*(1) |

| FMCP_HB_p[14] | PIN_BG27 | FMCP HB bank data p14 | FMCP_VCCIO*(1) |

| FMCP_HB_p[15] | PIN_BE27 | FMCP HB bank data p15 | FMCP_VCCIO*(1) |

| FMCP_HB_p[16] | PIN_BE26 | FMCP HB bank data p16 | FMCP_VCCIO*(1) |

| FMCP_HB_p[17] | PIN_BJ25 | FMCP HB bank data p17 | FMCP_VCCIO*(1) |

| FMCP_HB_p[18] | PIN_BH26 | FMCP HB bank data p18 | FMCP_VCCIO*(1) |

| FMCP_HB_p[19] | PIN_BA25 | FMCP HB bank data p19 | FMCP_VCCIO*(1) |

| FMCP_HB_p[20] | PIN_BJ26 | FMCP HB bank data p20 | FMCP_VCCIO*(1) |

| FMCP_HB_p[21] | PIN_BC26 | FMCP HB bank data p21 | FMCP_VCCIO*(1) |

| FMCP_HB_n[0]  | PIN_AN28 | FMCP HB bank data n0  | FMCP_VCCIO*(1) |

| FMCP_HB_n[1]  | PIN_AP31 | FMCP HB bank data n1  | FMCP_VCCIO*(1) |

| FMCP_HB_n[2]  | PIN_AN25 | FMCP HB bank data n2  | FMCP_VCCIO*(1) |

| FMCP_HB_n[3]  | PIN_AN26 | FMCP HB bank data n3  | FMCP_VCCIO*(1) |

| FMCP_HB_n[4]  | PIN_AP29 | FMCP HB bank data n4  | FMCP_VCCIO*(1) |

| FMCP_HB_n[5]  | PIN_AV26 | FMCP HB bank data n5  | FMCP_VCCIO*(1) |

| FMCP_HB_n[6]  | PIN_AT26 | FMCP HB bank data n6  | FMCP_VCCIO*(1) |

| FMCP_HB_n[7]  | PIN_AU27 | FMCP HB bank data n7  | FMCP_VCCIO*(1) |

| FMCP_HB_n[8]  | PIN_AY27 | FMCP HB bank data n8  | FMCP_VCCIO*(1) |

| FMCP_HB_n[9]  | PIN_AR27 | FMCP HB bank data n9  | FMCP_VCCIO*(1) |

|               |          |                       |                |

User Manual

| FMCP_HB_n[10] | PIN_BD28 | FMCP HB bank data n10 | FMCP_VCCIO*(1) |

|---------------|----------|-----------------------|----------------|

| FMCP_HB_n[11] | PIN_AW25 | FMCP HB bank data n11 | FMCP_VCCIO*(1) |

| FMCP_HB_n[12] | PIN_BB27 | FMCP HB bank data n12 | FMCP_VCCIO*(1) |

| FMCP_HB_n[13] | PIN_AY26 | FMCP HB bank data n13 | FMCP_VCCIO*(1) |

| FMCP_HB_n[14] | PIN_BF27 | FMCP HB bank data n14 | FMCP_VCCIO*(1) |

| FMCP_HB_n[15] | PIN_BF26 | FMCP HB bank data n15 | FMCP_VCCIO*(1) |

| FMCP_HB_n[16] | PIN_BD26 | FMCP HB bank data n16 | FMCP_VCCIO*(1) |

| FMCP_HB_n[17] | PIN_BH25 | FMCP HB bank data n17 | FMCP_VCCIO*(1) |

| FMCP_HB_n[18] | PIN_BG25 | FMCP HB bank data n18 | FMCP_VCCIO*(1) |

| FMCP_HB_n[19] | PIN_BB25 | FMCP HB bank data n19 | FMCP_VCCIO*(1) |

| FMCP_HB_n[20] | PIN_BH27 | FMCP HB bank data n20 | FMCP_VCCIO*(1) |

| FMCP_HB_n[21] | PIN_BC25 | FMCP HB bank data n21 | FMCP_VCCIO*(1) |

| FMCP_LA_p[0]  | PIN_AW38 | FMCP LA bank data p0  | FMCP_VCCIO*(1) |

| FMCP_LA_p[1]  | PIN_AP35 | FMCP LA bank data p1  | FMCP_VCCIO*(1) |

| FMCP_LA_p[2]  | PIN_AN33 | FMCP LA bank data p2  | FMCP_VCCIO*(1) |

| FMCP_LA_p[3]  | PIN_AP36 | FMCP LA bank data p3  | FMCP_VCCIO*(1) |

| FMCP_LA_p[4]  | PIN_AT37 | FMCP LA bank data p4  | FMCP_VCCIO*(1) |

| FMCP_LA_p[5]  | PIN_BB37 | FMCP LA bank data p5  | FMCP_VCCIO*(1) |

| FMCP_LA_p[6]  | PIN_AT38 | FMCP LA bank data p6  | FMCP_VCCIO*(1) |

| FMCP_LA_p[7]  | PIN_BB39 | FMCP LA bank data p7  | FMCP_VCCIO*(1) |

| FMCP_LA_p[8]  | PIN_AP34 | FMCP LA bank data p8  | FMCP_VCCIO*(1) |